- •1.1. Компенсация реактивной мощности 7

- •Здесь будет лист со штампом Общесистемный раздел

- •1.1. Компенсация реактивной мощности

- •1.2. Промышленные потребители реактивной мощности

- •1.3. Устройства компенсации реактивной мощности

- •1.4. Основные положения проектирования микропроцессорных устройств.

- •1.5. Pcad -основное средство проектирования микропроцессорных систем

- •1.5.1. Основные характеристики

- •1.5.2. Структура пакета

- •Здесь будет лист со штампом.

- •2. Специальный раздел

- •2.1. Техническое задание на разработку контроллера - компенсатора реактивной мощности

- •2.2. Общая характеристика

- •2.3. Обоснование элементной базы

- •2.3.1. Микропроцессор и микропроцессорный комплект

- •2.3.2. Память и логические элементы

- •2.3.3. Силовые элементы

- •2.4. Аппаратные средства контроллера

- •2.4.1. Плата контроллера

- •2.4.2. Плата тиристорного управления

- •2.4.3. Блок питания

- •2.4.4. Подключение контроллера – компенсатора

- •2.5. Алгоритмы контроля и управления

- •2.5.1. Измерение тока, напряжения и угла

- •2.5.2. Принцип управления конденсаторной установкой

- •2.6. Программное обеспечение контроллера

- •2.6.1. Структура программного обеспечения

- •2.6.1.1. Основная программа

- •2.6.1.2. Подпрограмма обработки прерывания trap

- •2.6.1.3. Подпрограмма обработки прерывания rst 7.5

- •2.6.1.4. Комплекс подпрограмм типа bios

- •2.6.2. Распределение адресного пространства

- •Область векторов прерываний

- •2.7.2. Технология разработки и отладки программ контроллера наIbm– совместимом компьютере.

- •2.7.3. Программные средства Сервисная программа контроллера-компенсатора

- •2.7.4. Конструктив

- •3. Организационно – экономический раздел

- •4. Раздел безопасности и экологичности Заключение

- •Литература

- •Приложение

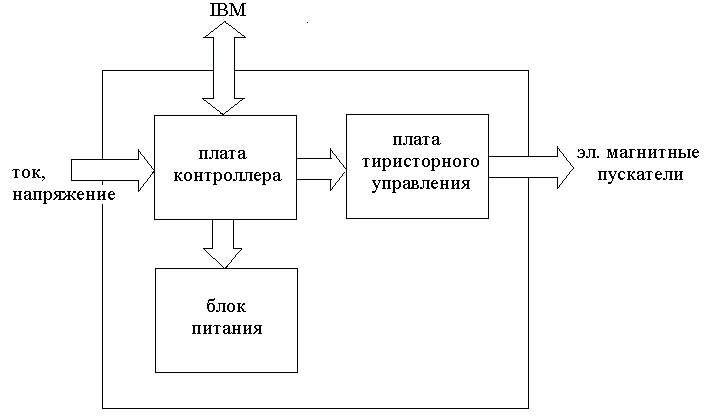

2.4. Аппаратные средства контроллера

Контроллер – компенсатор реактивной мощности включает в себя следующие компоненты (рисунок 2.4.1.):

-плата контроллера;

-плата тиристорного управления;

-блок питания.

Рисунок 2.4.1. Структурная схема контроллера-компенсатора.

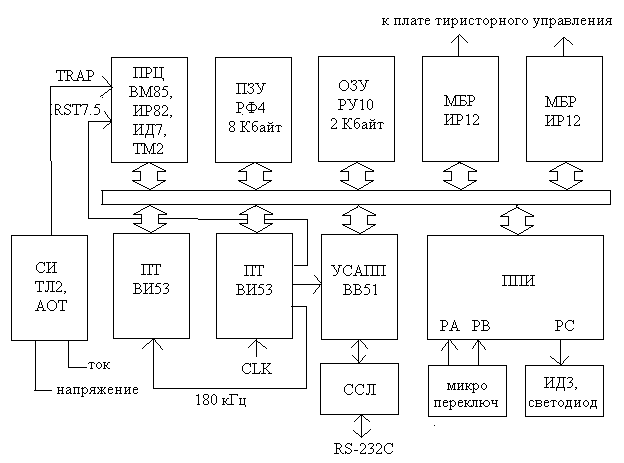

2.4.1. Плата контроллера

Плата контроллера содержит следующие узлы (рис. 2.4.1.1.):

процессор на основе микропроцессора (МП) М1821ВМ85А (микросхемы D1, D2, D4, D6.2);

постоянное запоминающее устройство (ПЗУ) К573РФ6 (D9);

оперативное запоминающее устройство (ОЗУ) КР573РУ10 (D10);

два буферных регистра (МБР) КР589ИР12 (D14, D15);

параллельный интерфейс (ППИ) КР580ВВ55А (D11);

программируемый таймер (ПТ) прерываний и синхронизации КР580ВИ53 (D13);

последовательный интерфейс (УСАПП) КР580ВВ51А (D17);

схема связи с линией (ССЛ) RS-232C (D18, D19);

схема измерения (СИ) тока и напряжения (T1, D5, D7, D6.1, D12)

схема индикации и микропереключатели (D16, Q1, Q2);

Рисунок

2.4.1.1. Структурная схема платы контроллера.

Рисунок

2.4.1.2. Электрическая принципиальная

схема контроллера – компенсатора.

Рисунок

2.4.1.3. Электрическая принципиальная

схема контроллера – компенсатора.

Рисунок

2.4.1.4. Схема расположения элементов на

плате контроллера.

Принцип измерения величин тока, напряжения и угла между ними.

В контроллере-компенсаторе заложен оригинальный принцип измерения тока, напряжения сети и угла между ними.

Измерительная схема контроллера построена на триггерах Шмитта. Триггер Шмитта серии микросхем ТТЛ имеет порог срабатывания 1.7 В при входном сигнале до 5 В. При "пропускании" синусоиды напряжения через триггер получаются импульсы, ширина которых будет зависеть от амплитуды синусоиды. Чем больше амплитуда, тем шире импульсы и наоборот. Длина импульсов в контроллере измеряется с помощью программируемого таймера КР580ВИ53 на входы CLK которого с генератора постоянно подается частота 180 Кгц.

И Рисунок

2.4.1.3. Принцип измерения величин тока

и напряжения.

Чтобы измерить угол ФИ между током и напряжением в измерительной схеме используется третий счетчик таймера КР580ВИ53. Он фиксирует разность во времени между приходом импульсов тока и напряжения.

Адреса и назначение программируемых БИС контроллера представлены в таблицах 2.4.1.1 – 2.4.1.7.

Таблица 2.4.1.1.

Последовательный интерфейс К580ВВ51 (RS-232)

|

4000H |

SARTD |

регистр данных |

|

4001H |

SARTC |

регистр состояния и управления |

Таблица 2.4.1.2.

Таймер1 К580ВИ53

|

4800H |

ST1Z0 |

счетчик А импульса напряжения U |

|

4801H |

ST1Z1 |

счетчик В импульса тока I |

|

4802H |

ST1Z2 |

счетчик С импульса первой ступени |

|

4803H |

RUST1 |

регистр управляющего слова |

Таблица 2.4.1.3.

Таймер2 К580ВИ53

|

5000H |

ST2Z0 |

запрос прерывания TRAP процессора |

|

5001H |

ST2Z1 |

синхронизация счетчиков A, B, C 180кГц |

|

5002H |

ST2Z2 |

синхронизация RS-232C 9.6 КГц |

|

5003H |

RUST2 |

регистр управляющего слова |

Таблица 2.4.1.4.

Параллельный интерфейс К580ВВ55

|

5800H |

PRTA |

порт A |

|

|

|

PA3-PA0 коэффициент для расчета дискретности управления |

|

|

|

PA7-PA4 коэффициент для расчета задания ФИ |

|

5801H |

PRTB |

порт B |

|

|

|

PB3-PB0 коэффициент для расчета нечувствительности |

|

|

|

PB4 режим отладки |

|

|

|

PB5 порядок включения коммутаторов |

|

|

|

PB6 передача видеобуфера |

|

|

|

PB7 знак задания ФИ |

Продолжение табл. 2.4.1.4.

|

5802H |

PRTC |

порт C |

|

|

|

PC3-PC0 на дешифратор индикаторов |

|

|

|

PC4 разрешение дешифратора |

|

5803H |

RUSP |

регистр управляющего слова |

Таблица 2.4.1.5.

Буферные регистры К589ИР12

|

6000H |

MBR1 |

младшие разряды |

|

67FFH |

MBRD |

слово целиком |

|

6800H |

MBR2 |

старшие разряды |

Таблица 2.4.1.6.

Прерывания контроллера

|

Источник запроса прерывания |

вход МП |

начальный адрес подпрограммы |

|

Начальный сброс |

RESET |

0000 H |

|

Логика D8.1 |

TRAP |

0024 H |

|

ПТ D13 счетчик 0 |

RST 7.5 |

003C H |

Таблица 2.4.1.7.

Выходные порты контроллера

|

Обозначение |

Микросхема |

Разряд |

разъем |

куда |

|

D14 |

К589ИР12 |

Q0 |

ХР3: 1 |

|

|

|

|

Q1 |

ХР3: 2 |

на плату |

|

МБР1 |

|

Q2 |

ХР3: 3 |

тиристорного |

|

|

|

Q3 |

ХР3: 4 |

управления |

|

|

|

Q4 |

ХР3: 5 |

|

|

|

|

Q5 |

ХР3: 6 |

(младшие |

|

|

|

Q6 |

ХР3: 7 |

разряды) |

|

|

|

Q7 |

ХР3: 8 |

|

|

D13 |

К589ИР12 |

Q0 |

ХР2: 9 |

|

|

|

|

Q1 |

ХР2: 10 |

на плату |

|

МБР2 |

|

Q2 |

ХР2: 11 |

тиристорного |

|

|

|

Q3 |

ХР2: 12 |

управления |

|

|

|

Q4 |

ХР2: 13 |

|

|

|

|

Q5 |

ХР2: 14 |

(старшие |

|

|

|

Q6 |

ХР2: 15 |

разряды) |

|

|

|

Q7 |

ХР2: 16 |

|