- •Оглавление

- •Введение

- •Техническое задание

- •Описание мпи

- •Описание бмк 5501хм2

- •Используемые семисегментные индикаторы.

- •Разработка проекта Определение списка выводов бис.

- •Синтез структурной схемы устройства

- •Определение структуры устройства на верхнем уровне иерархии

- •Блок интерфейса с мпи

- •Первый вариант взаимодействия интерфейсного блока с внутренними регистрами

- •Альтернативный взаимодействия интерфейсного блока с внутренними регистрами

- •Внутренние регистры устройства

- •Блок индикации

- •Арифметико-логическое устройство (алу)

- •Синтез принципиальной схемы устройства Реализация принципиальной схемы на верхнем уровне иерархии

- •Реализация блока inout (интерфейса с мпи)

- •Реализация блока win (схемы управления адресным окном)

- •Реализация блоков outdv (буферных блоков)

- •Реализация блока dc8b (определения смещения внутри окна)

- •Реализация блока dc8n4 (индикации)

- •Реализация блока mux4x1

- •Реализация блока dec(семисегментного индикатора)

- •Реализация блоков reg8 (внутренних регистров)

- •Реализация блока summ8 (алу)

- •Реализация блока deccom (дешифрации команд)

- •Заказ контрольных точек

- •Моделирование работы устройства

- •Разработка топологии устройства Размещение устройства на бмк 5501хм2

- •Трассировка и оценка задержек

- •Оптимизация размещения

- •Маршрут проектирования

- •Технико-экономическое обоснование выбора проектирования схемы на бмк

- •Технико-экономический анализ прогрессивности принимаемого решения и формирование исходных данных для расчета

- •Выбор различных вариантов реализации схемы для сравнения и приведения их к сопоставимому виду

- •Расчет капитальных вложений

- •Расчет текущих затрат

- •Расчет основных показателей сравнительной экономической эффективности

- •Расчет капитальных вложений

- •Расчет текущих затрат

- •Расчет основных показателей сравнительной экономической эффективности

- •Список принятых сокращений

- •Инженерно-психологические факторы при обработке программ на эвм. Экологическая безопасность. Предисловие

- •Цели и задачи инженерно-психологического проектирования

- •Понятие интерфейса взаимодействия и принципы его проектирования

- •Человек как звено обработки информации Зрительная система человека и ее основные характеристики

- •Характеристики слухового аппарата человека

- •Преобразование информации в кратковременной памяти человека

- •Сенсомоторная деятельность оператора

- •Надежность выполнения операций

- •Надежность работы оператора с ручкой управления

- •Задачи инженерно-психологического проектирования взаимодействия человека и эвм

- •Экология

- •Выводы по главе 6

- •Приложение а. Описание магистрального параллельного интерфейса (мпи) Общая организация.

- •Функциональная организация.

- •Временные диаграммы взаимодействия сигналов мпи в выбранном режиме

- •Приложение б. Описание семисегментных индикаторов

- •Приложение в. Описание бмк 5501хм2

Арифметико-логическое устройство (алу)

АЛУ является пользовательским блоком, т.е. блоком который проектирует тот, кто будет приспособлять данное УСТРОЙСТВО к конкретной БИС. В данном УСТРОЙСТВЕ

АЛУ представлено в качестве примера и необходимо для проверки работоспособности БИС в целом. Поэтому ограничимся формулировкой требований к АЛУ разрабатываемых пользователем:

АЛУ может обеспечивать вычисление единственной функции от трех переменных, либо набора функций от 2-х переменных.

Разрядность переменных и кода ограничена разрядностью МПИ.

Дешифрация функций возлагается на АЛУ, т.е. на вход АЛУ подается код оператора в двоичном виде.

Синтез принципиальной схемы устройства Реализация принципиальной схемы на верхнем уровне иерархии

Схема УСТРОЙСТВА на верхнем уровне иерархии приведена в приложении Г.

Представленные на схеме блоки выполняют следующие функции:

INOUT-Блок интерфейса с МПИ.

SUMM-Арифметико-логическое устройство.

DC8N4-Блок индикации.

RGU8-Внутренние регистры УСТРОЙСТВА.

Реализация блока inout (интерфейса с мпи)

Принципиальная логическая схема блока INOUT Приведена в приложении Г.

Рассмотрим функции блоков, составляющих схему:

WIN-схема управления адресным окном и идентификации обращения по адресам, лежащим в адресном окне.

OUTD-буферные схемы для преобразования внешних сигналов БИС во внутренние и обратно, имеют третье состояние.

RGU3-регистр для хранения смещения внутри адресного окна.

DC8B-дешифратор смещения внутри окна.

Реализация блока win (схемы управления адресным окном)

Для управления адресным окном нам необходимо знать адрес его начала. Однако мы должны иметь возможность оперативно изменять этот адрес. Для достижения этой цели мы зарезервируем один из адресов адресного пространства шины (в данном случае FFFFh) и присвоим его (адрес) регистру управления адресным окном. Поскольку внутри окна нам необходимо три адреса то легче всего позиционировать окно по 14 разрядам адреса. При этом под окно будут отведены 4 адреса, один из которых не будет использоваться.

При обращении на шине по любому адресу блок управления сравнивает старшие 14 разрядов адреса и содержимое регистра управления окном. При совпадении этих величин на выходе блока появляется сигнал.

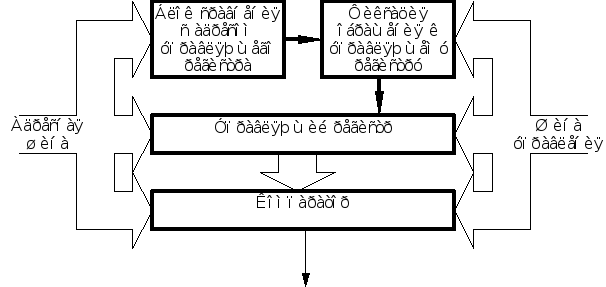

С учетом всего сказанного мы можем построить структурную схему блока управления окном. Она приведена ниже.

Рис. 9. Структурно-функциональная схема блока управления адресным окном

Принципиальная логическая схема построенная на основе данной структурной приведена в приложении Г.

Блоки приведенные на рисунке 9 выполняют следующие функции:

COMPFF-определяет, является ли текущий адрес адресом управляющего регистра

COMP-определяет, лежит ли текущий адрес внутри адресного окна

REG-регистр хранения начального адреса адресного окна (управляющий регистр)

DT-регистр-защелка

Принципиальные логические схемы этих блоков и их раскрытие до нижнего уровня иерархии приведены в приложении Г.

Реализация блоков outdv (буферных блоков)

Буферные блоки OUTDV предназначены для согласования внешних и внутренних электрических сигналов. Они построены на основе мощных Z-ячеек и по сути не выполняют каких либо логических или арифметических функций. Кроме того буферные блоки могут переводить выводы БИС в т.н. третье состояние, которое применяется в тех случаях, когда БИС находится в неактивном состоянии.

Принципиальная логическая схема блоков OUTDV приведена в приложении Г.