aaaГОСЫ / Лекции Кузнецов часть 1

.pdf

1

1 Введение

Эволюция развития микропроцессорной техники

Первый |

микропроцессор |

был изготовлен фирмой |

Intel в 1971 г. - |

Intel 4004 |

||

(Fclk = 0,75 МГц). До этого |

момента функции микропроцессора |

реализовывались |

с помощью |

|||

набора |

ИС |

средней и |

малой |

степени интеграции (счетчики, регистры, |

сумматоры, |

|

комбинационная ложка и т.д.). Первый микропроцессор был 4-х разрядным, реализован по n- МОП технологии, содержал 2,3 тыс. транзисторов, выполнял 80 000 операций в секунду и 45 команд. Это был однокристальный центральный процессор, имеющий в своем составе четырехразрядный параллельный сумматор, 15 четырехразрядных регистров и стек.

Современный микропроцессор Alpha содержит 15,2 миллионов транзисторов (по данным 1999-2000 г.). Тактовая частота составляет 800 МГц, выполняет 5,2 миллиарда операций в секунду.

1673 г. – первое вычислительное устройство. Оно называлось Арифмометр. К. Лейбниц 1943 г. – вычислительная машина «Марк 1» на электромагнитном реле.

1945 г. – вычислительная машина на радиолампах.

1948 г. – изобретение транзистора..

1953 г. – Кирхе соединил несколько транзисторов на одной подложке 1958 г. – получены первые микросборки Нойсом и Кирхе.

Основные понятия

Микропроцессор (МП) – это микросхема или совокупность небольшого числа микросхем (один или несколько кристаллов БИС), выполняющая над данными арифметические и логические

операции и осуществляющая программное управление вычислительным процессом. Микропроцессорная система (МПС) – специализированная информационная или

управляющая система, построенная на основе микропроцессорных средств. Микропроцессорный комплект (МПК) – набор различных ИМС различной степени

интеграции, объединенных по конструктивно-технологическому признаку и предназначенных для

совместного использования при построении МП, микроЭВМ, контроллеров и др. Конструктивно-технологический признак – одна конструкция и технология изготовления.

Один и тот же вид корпуса (один или разные) для объединения их в один.

3 вида МП:

1)универсальный

2)специализированный – для создания конкретной микроЭВМ (например, Электроника 60)

3)секционный – позволяют получать гибкую систему команд и позволяют набирать из секции любые разряды ЭВМ. Секции входят в различные комплекты.

ИМС делятся по степени интеграции (k)

k = ] lg N [

N – число активных элементов на подложке.

МИС (1÷10) – ИС малой степени интеграции (например, элементы И, ИЛИ, НЕ)

СИС (10÷100) – средней степени интеграции (счетчики, регистры, буферное устройство) БИС (100÷1000) – большие ИС (микроконтроллеры)

СБИС (> 1000) – сверхбольшие ИС (большие ОЗУ)

В МПК нет смешения технологий и конструктивно-технологический признаков.

2

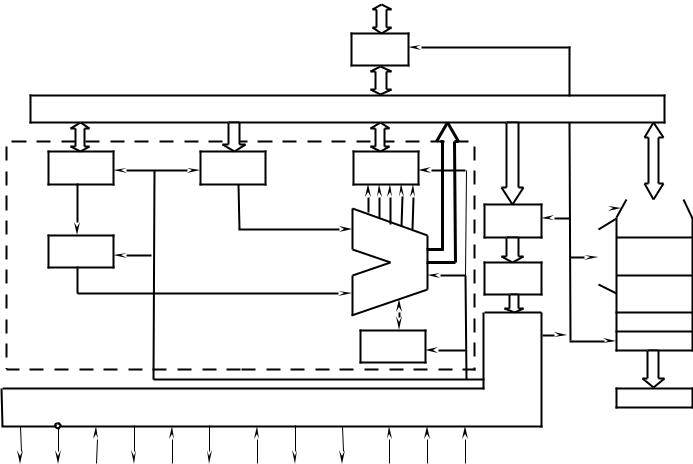

Структурная схема трех-магистральной микроЭВМ

МП |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

шина Адреса |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

АЛУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

шина |

Данных |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

шина управления |

||||

|

УУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЧтЗап. |

|

|

|

|

|

|

ЧтЗап. |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

КПДП |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

ОЗУ |

|

ПЗУ |

|

|

|

|

|

П.Ввод |

|

П.Выв. |

|

|

||||||||

Устройство |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

Устр.памяти |

|

|

|

|

|

|

Устр. ввода/выв. |

|

||||||||||||||||

сопряжени |

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

||||||||||||||||||||

я |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

к ВУ |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

АЛУ – арифметическое логическое устройство (реализует вычислительные действия) УУ – устройство управления

Устройство сопряжения (синхронизации). Включает в себя тактовый генератор, который выводятся из МП, т.к. чем больше частота, тем больше выделяется тепла. Применяется для уменьшения влияния генераторов.

УВВ – устройство ввода – вывода. Обмен информацией между внешним устройством и ЭВМ.

П.Ввод – порт ввода

П.Вывод – порт вывода

Шина адреса – для адресации шин памяти (однонаправленная)

Шина данных – основная шина данных (двунаправленная) Шина управления (может быть двунаправленной)

ПЗУ – постоянное запоминающее устройство. При выключении питания информация не теряется.

ВУ – внешнее устройство – подсоединяется к шинам МП не непосредственно, а через ППА. КПДП – контроллер прямого доступа к памяти – проставляет шину адреса и данных.

Ведущее устройство в режиме DMA.

Система шин МПС: Для МП характерна трехшинная структура, содержащая шину адреса, двунаправленную шину данных и шину управления.

Основные характеристики:

−тип микроэлектронной технологии

−количество кристаллов, образующих МП, размеры кристалла, количество элементов (транзисторов) на кристалле, количество выводов корпуса кристалла

−длина (количество разрядов) слова

−быстродействие МП (тактовая частота, время выполнения команд основных операций)

−емкость адресуемой памяти

−тип управляющего устройства (схемное или микропрограммное управление)

−эффективность системы команд (количество команд, выполняемые операции, возможные способы адресации, наличие команд работы со стековой памятью, команд операций с битами, десятичными числами и т.п.)

−число уровней прерывания

−возможность прямого доступа к памяти

−пропускная способность интерфейса ввода-вывода

3

−количество и уровни питающих напряжений

−номинальные параметры используемых сигналов

−мощность

2 типа корпусов по конструкции:

1)Dip – контакты расположены так, что необходимо сверлить корпус.

2)Планарный – выводы соединены с контактными площадками и сверления не требуется.

В состав базового комплекта входят следующие основные БИС:

ИК 80А – центральный процессор (ЦП)

ГФ 24 – генератор тактовых импульсов (ГТИ) ВК 28 (38) – системный контроллер (СК)

ИК 57 – контроллер прямого доступа в память (КПДП)

ВН 59 – программированный контроллер прерываний (ПКП) ИК 55 – программируемый параллельный адаптер (ППА) ВИ 53 – программируемый интервальный таймер (ПИТ)

ВА 86 (87) – шинный формирователь (ШФ) ВГ 75 – контроллер клавиатуры и индикации

ВГ 79 – контроллер дисплея и клавиатуры (КД и КА) Это универсальный комплект.

Каждая магистраль подключается через соответствующие устройства сопряжения. Чем больше линий шин адреса, тем мощнее машина. Чем больше линий шин данных, тем интеллектуальнее машина.

Данные перердаются в параллельной форме.

Режим прямого доступа к памяти – информация передается из внешнего устройства в устройство памяти, минуя МП (через шину данных) DMA.

2 Структурная схема МП

к ш. Данных

|

|

БШД |

|

8-разрядная шина данных |

|

А |

БР |

РП |

РК

РЗА |

АЛУ |

|

ДШК

АЛБ |

|

|

|

|

|

|

|

DK |

|

УУ и |

|

|

|

|

|

|

|

|

|

синхр. |

|

|

|

|

|

|

|

|

|

|

|

|

ПМ |

ВД ЗПР |

РПР |

ЗПДП |

ППДП |

ГТ |

ОЖ |

Синхр. |

С1 |

С2 |

СБР. |

4

|

|

|

|

|

MS |

|

|

|

|

|

|

|

|

||

|

|

|

|

W |

|

Z |

|

|

|

|

|

|

|||

|

DШ |

|

B |

|

C |

||

|

|

D |

|

E |

|||

|

|

|

|

|

|||

|

|

|

H |

|

K |

||

|

|

|

|

||||

УС

СК

РА

БРА к ш.Адреса

ИК 80А представляет собой изготовленную по n-МОП технологии БИС, содержит 5 тыс. транзисторов, длина слова – 8 разрядов, тактовая частота – 2 МГц, уровни напряжения питания

± 5В, + 12 В.

Особенности МП:

∙Трехшинная структура с шинами данных, адреса и управления

∙Магистральные принципы связи, реализованные в виде связывающей основные узлы двунаправленной ШД, имеющей ширину 8 разрядов, равную длине слов, обрабатываемых МП

∙Наличие регистровой памяти, образованной программно-доступными общими и специальными регистрами (СК, УС), и регистрами временного хранения

∙Наличие средств организации стековой памяти

∙Наличие 16-разрядной ША (возможность прямой адресации любого байта в памяти)

∙Наличие операций над 2-байтными словами(обеспечивается спец.командами, тандемных пересылок)

∙Использование 3-х форматов команд и разнообразных способов адресации

∙Возможность реализации векторного многоуровневого приоритетного прерывания (ПКП)

∙Возможность организации ПДП (КПДП)

∙Наличие средств работы с подпрограммами и обработки запросов прерываний

МП состоит из 3 основных частей: АЛБ, Регистры, УУ

5

АЛБ – арифметический логический блок включает в себя:

АЛУ – 8-разрядная комбинационная схема, выполняющая арифметические и логические операции над 8-разрядными числами. К одному из входов схемы АЛУ всегда подключен Аккумулятор, к другому – любой из региров РОН через ШД. АЛУ имеет собственный регистр временного хранения БР, который позволяет избежать гонок, когда один из регистров РОН используется в одной операции как регистр источник и регистр приемник. АЛУ выполняет следующие операции: сложение, вычитание, и, или, исключающее или, инверсия, сдвиги,

приращения.

ДК – десятичный корректор – устройство, которое под воздействием специальной команды интерпретирует результат выполнения двоичной операции как результат операции десятичной арифметики. Коррекция осуществляется прибавлением двоичного кода числа шесть к младшей или старшей тетраде результата, когда содержимое их находится в пределах А – F или в случае

возникновения основного или дополнительного переноса.

Регистры МП:

А – аккумулятор –основной 8-разрядный регистр микропроцессора служит для хранения одного из операндов (до операции) и результата после нее. Все операции АЛУ выполняет через

А. Существуют микропроцессоры с несколькими А.

РЗА – регистр-защелка аккумулятора – 8-разрядный регистр. Хранит предыдущее значение аккумулятора, пока результат идет через регистр признаков (РП) в аккумулятор.

Благодаря ему аккумулятор не является источником и приемником АЛУ.

БР - буферный регистр операнда (8-разр.). Служит для промежуточного хранения 2-го

операнда (1-й операнд - в А).

РП – регистр признаков – 5-разрядный регистр (иногда называемый регистром состояния), связанный с АЛУ. В соответствующих разрядах фиксируются особенности выполнения каждой из операций. Он представляет собой набор триггеров, называемых флажками.

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

S |

Z |

0 |

H |

0 |

P |

1 |

C |

S – (sign) признак отрицательности числа Z – (zero) признак 0

H – признак переноса между тетрадами. Необходим для работы ДК P – признак четности числа единиц в результате

C – (carry) основной перенос – переполнение разрядной сетки

РК – регистр команд – предназначен для хранения кода текущей выполняемой команды. Выполнение каждой команды производится МП в строгой последовательности, определяемой

кодом команды, и синхронизируется во времени с сигналам ГТИ.

ДШК – дешифратор команд РОН – регистры общего назначения – используются для хранения операндов,

промежуточных и конечных результатов, а также адресов и индексов при косвенной и индексной адресациях. Причем регистры могут составлять пары (BC, DE, HL).

Особые регистры:

РС – счетчик команд (СК) (со схемой приращения +1) - используется для приема и

хранения адреса следующей команды (16)

SP – указатель стека (УС) 16-разрядный регистр, который содержит адрес ячейки стековой памяти занятой информацией (вершины стека). Используется стек обратного типа, т.е. при передаче в стек информации величина УС уменьшается, а при извлечении информации из стека УС – увеличивается.

HL – пара 8-разрядных регистров, которые могут использоваться совместно. В этом случае Н - старший байт, L - младший байт. Пару называют регистром адреса/данных. Регистры HL

6

являются универсальными: они могут быть инкрементированы, декрементированы, загружены данными или служить их источником. Особенностью HL является то, что они могут использоваться в качестве адресного регистра, т.е. хранить адрес назначения при размещении данных или источника при загрузке данных в МП. Пример: ADD M - команда сложить А с данными, расположенными по адресу HL.

Стек – область ОЗУ магазинного типа (последний пришел, первый вышел), в которой запись

и чтение информации производится через вершину стека.

РА – регистр адреса – 16-разрядный служит для приема и хранения в течение одного

машинного цикла адреса команды или операнда и выдачи его на буферный регистр адреса. Регистры W, Z – программно-недоступные регистры – предназначены для тандемных

пересылок, когда в цикле выполнения команды последовательно друг за другом передаются два

байта информации.

Устройство управления (УУ)

УУ и Синхр. – устройство управления и синхронизации МП состоит из двух отдельно независимых частей:

−Первичного автомата, управляющего процессами внутри МП

−Логической схемы, обрабатывающей входные сигналы и формирующей управляющие

сигналы в микропроцессорной системе.

Микрокоманды могут быть двух видов: |

|

|

||||

1 Управляющие |

31-1 - |

ВР1 используется для изменения последовательности команд в |

||||

зависимости от тех или иных условий. |

|

|

||||

2 Операционные |

31-0 - ВР0 - слово управляет вентильными схемами. |

|

||||

|

|

|

|

Сигналы устройства управления: |

|

|

ПМ |

DBIN |

Прием МП – сигнал высокого уровня, информация на ШД будет считана в МП |

||||

ВД |

WR |

Выдача данных – сигнал инверсный низкого уровня, показывает, что МП |

||||

|

|

выставил на ШД информацию |

|

|

||

ЗПР |

INT |

Запрос на прерывание – сигнал запроса прерывания высокого уровня от |

||||

|

|

внешнего устройства. Каждому сигналу соответствует своя программа |

||||

|

|

прерывания. |

|

|

|

|

РПР |

INTE |

Разрешение прерывания – сигнал высокого уровня, показывает, что |

||||

|

|

внутренний триггер прерывания в устройстве управления МП установлен в |

||||

|

|

«1», т.е. МП переходит в режим обслуживания прерываний |

|

|||

ЗПДП |

HOLD |

Запрос прямого доступа в память – сигнал высокого уровня, указывает на |

||||

|

|

зарос другими устройствами прямого доступа к памяти (чтение или запись), |

||||

|

|

для увеличения быстродействия |

|

|

||

ППДП |

HLDA |

Подтверждение прямого доступа в память – сигнал высокого уровня, |

||||

|

|

указывает на перевод ША и ШД в состояние высокого сопротивления |

||||

ОЖ |

WAIT |

Ожидание – сигнал высокого уровня. Для работы с внешними устройствами |

||||

ГТ |

READY |

Готовность – сигнал высокого уровня, показывает на готовность внешнего |

||||

|

|

устройства к обмену информацией, т.е. к синхронизации работы внешнего |

||||

|

|

устройства с АЛУ |

|

|

||

С1, С2 |

CLK1, |

Тактовые импульсы от ГТИ для того, чтобы МП производил действия. |

||||

|

CLK2 |

Применяются |

непересекающиеся |

последовательности |

(сдвинутые |

|

СИНХР |

SYNC |

относительно друг друга) для исключения гонок в узлах |

|

|||

Начало машинного цикла МП, вырабатывается Устройством управления |

||||||

СБР |

RESET |

Системный |

сброс. Находится на |

ГТИ и привязан к тактовой частоте. |

||

Обнуляется программный счетчик, сбрасывается УС и устройство переходит к начальной загрузке операционной системы или программы.

7

Работа управляющего автомата. Цикл и такт

Форматы команд:

1)В1 – однобайтные

2)В1, В2 – двухбайтные

3)В1, В2, В3 – трехбайтные

Команды должны располагаться последовательно в ячейках: в 1 ячейке код команды, в

остальных – информация, отличная от кода.

МЦ – машинный цикл – время выборки (извлечения) кода команды или 1 байта команды. МТ – машинный такт – время одного периода тактовой последовательности.

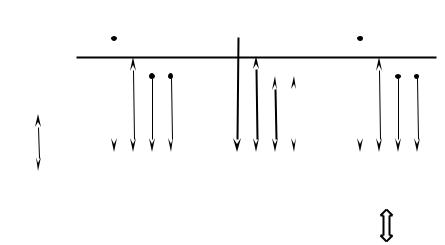

Т1 |

Т2 |

C1

t = 0.9 нс

t

C2

t

синхр.

t

строб

t

УУ может находиться в одном из следующих состояний (машинных циклов): выборки

(извлечения), декодирования, выполнения. Следует отметить, что МП всегда работает по принципу: извлечение - декодирование - выполнение

Строб /STSTB/ - сигнал малой длительности. Служит для вывода слова состояния SW МП для записи его в буферный регистр (во 2-м МТ). С его помощью МП знает, в какой МЦ вводить слово состояния. Вырабатывается ГТИ.

Выполнение рабочего цикла команды начинается с опроса триггера прерывания.

Если запрос прерывания поступил, то автомат передает управление программе обработки прерывания и выполняется соответствующая программа обслуживания данного запроса прерывания.

При отсутствии прерыванию управляющей автомат генерирует управляющие сигналы выборки команды из памяти и формирования в СК адреса следующей команды. После выборки команды автомат дешифрирует код операции (КОП) в команде и генерирует серию управляющих сигналов, соответствующих КОП, обеспечивая реализацию в МП заданной операции.

Код команды определяет количество машинных циклов, необходимых для выполнения данной команды. Каждая команда состоит из 1 до 5 машинных циклов. Каждый МЦ содержит от 3

до 5 машинных тактов.

Типы машинных циклов в зависимости от кода команды:

М1 – извлечение кода команды, М2 – Чтение памяти, М3 – Запись в память, М4 – Чтение стека, М5 – Запись в стек, М6 – Чтение внешнего устройства, М7 – Запись во внешнее устройство, М8 – Обслуживание прерывания, М9 – Обслуживание остановок, М10 – Обслуживание прерывания в режиме остановок.

|

Работа первичного автомата |

|

8 |

|||

|

|

|

||||

|

СБР |

|

|

|

|

|

|

Т1 |

|

|

|

|

|

|

v HLTA |

|

|

|

|

|

|

Т2 |

HLTA |

|

|

|

|

|

|

|

|

|

||

|

READY |

нет |

READY |

INT*INTE |

|

Тwн |

|

Тw |

|

(РПР*ЗПР) |

|

||

|

|

|

|

|

|

|

|

HOLD (ЗПДП) |

|

|

|

Уст ТТ2 (ЗПДП) |

|

|

нет |

Уст ТТ2 |

сброс |

|

|

|

|

|

|

Захват |

|||

|

Т3 |

|

|

|||

|

(зпдп) |

|

|

|

(режим ПДП) |

|

|

|

ПДП |

|

|

|

HOLD |

|

|

|

|

|

|

|

|

Т4 |

Режим |

|

|

Сброс ТТ2 (ПДП) |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

Т5 |

|

|

|

|

|

|

HOLD |

|

HOLD (ПДП) |

|

|

|

|

|

|

|

|

||

|

|

Захват |

|

|

|

|

нет |

конец команды |

(режим ПДП) |

|

|

|

|

|

HOLD |

|

|

|

||

|

да |

|

|

|

||

|

Сброс ТТ2 (ПДП) |

|

|

|

||

нет |

|

|

|

|

||

ЗПР*РПР |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Уст. ТТ1 (РПР) |

|

|

|

|

|

Tw – такт ожидания по неготовности, Twн – такт ожидания по останову – эти состояния не |

||||||

связаны с тактовой частотой, их продолжительность неопределенная, т.к. зависит от внешних по |

||||||

отношению к МП событий. |

|

|

|

|

|

|

1 Первичный автомат находится в УУ. Цикл команды реализуется за 1-5 машинных циклов. Машинный цикл содержит от 3 до 5 машинных тактов Т. Каждый такт образует пара сигналов тактирования С1 и С2, поступающих от внешнего генератора. В начале каждого МЦ первичный автомат генерирует сигнал синхронизации СИНХР.

2 Подача сигнала высокого уровня на вход RESET длительностью не менее 3-х периодов такотвой частоты устанавливает МП в исходное состояние. Схема управления формирует сигнал Т1 выборки команды М1.

3 В такте Т2 идет анализ сигналов READY, HLTA, HOLD. При наличии сигнала высокого уровня на входе READY и отсутствии сигналов HLTA, HOLD МП переходит к такту T3. Если

9

выполнение команды не закончено, то МП переходит к следующему машинному циклу команды, начиная с такта Т1. В конце каждой команды МП проверяет наличие запроса прерывания. Если есть высокий уровень сигнала на входе INT и триггер разрешения прерывания установлен INTE=1, то МП устанавливает триггер прерывания ТТ1 и приступает к выполнению машинного цикла прерывания, начиная с Т1.

При наличии на входе READY сигнала низкого уровня в такте Т2 МП переходит в состояние ожидания Tw, пока не появится сигнал READY от внешнего устройства.

4 В такте Т2 при наличии сигналов на входах READY и HOLD производится установка внутреннего триггера захвата ТТ2. Переход к режиму захвата до такта Т3 не разрешается, чтобы МП мог закончить обмен с внешним регистром в начале такта Т3. По окончанию состояния захвата МП переходит к такту Т1 следующего МЦ. Если текущий МЦ содержит такты Т4 и Т5, то они совмещаются с режимом захвата.

5 В состоянии останова МП переходит при наличии сигнала HLTА, формируемого во втором машинном цикле команды HLT, при этом внутренние шины адреса и данных переводятся в высокоимпедансное состояние и появляется высокий уровень напряжения на выходе WAIT – выполнение программы прекращается. Из состояния останова МП выходит по сигналу сброса RESET или по сигналу запроса прерывания INT при установленном триггере разрешения прерываний INTE=1. В состоянии останова МП может переходить в режим захвата, если поступает сигнал высокого уровня на вход HOLD.

В конце каждой команды МП проверяет наличие запроса прерывания. Если есть высокий уровень сигнала на входе INT и триггер разрешения прерывания установлен в состояние «1», то МП фиксирует поступивший запрос прерывания во внутреннем триггере ТТ1 и приступает к выполнению машинного цикла прерывания, начиная с такта Т1.

Отличие машинного цикла прерывания от машинного цикла выработки состоит в том, что содержимое СК не инкрементируется, а запоминается в стеке с последующим восстановлением после окончания программы прерывания.

Слово состояния микропроцессора

Из хранимых признаков МП составляет свое |

слово |

состояния (1 байт). Содержит 8 |

|||||

разрядов: |

|

|

|

|

|

|

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

S |

Z |

0 |

H |

0 |

P |

1 |

C |

S – (sign) признак отрицательности числа

Z – (zero) признак 0

H – признак переноса между тетрадами. Необходим для работы ДК

P – признак четности числа единиц в результате

C – (carry) основной перенос – переполнение разрядной сетки

10

3 Способы адресации. Форматы команд Способ адресации – нахождение источников и приемников команды.

5 способов адресации: Регистровый – адрес регистра источника и приемника находится в коде команды (например, команды пересылки). Регистрово-косвенный – адрес ячейки памяти

находится как содержимое индексного (адресного, косвенного) регистра – регистровая пара HL. Непосредственный – информация находится в самой команде – во 2-м или 3-м байте команды. Прямой – в коде команды во 2-м или во 2-м и 3-м байте указывается адрес внешнего комплексного устройства или ячейки памяти. Стековый – включается механизм стековой памяти.

Адрес ячейки памяти находится как содержимое указателя стека.

Программная модель МП

B |

000 |

C |

D |

010 |

E |

H |

100 |

L |

|

|

M |

A |

111 |

F |

SPH |

|

SPL |

PCH |

|

PCL |

0000

0001

65 536

FFFE

FFFF

001

101011  } РОН

} РОН

110 Абстрактная ячейка памяти

Абстрактная ячейка памяти

PSW – слово состояния программы, включающее аккумулятор и регистр

PSW – слово состояния программы, включающее аккумулятор и регистр

SP – указатель стека

SP – указатель стека

PC – программный счетчик

PC – программный счетчик

256

00  …

…  Порт ввода FF

Порт ввода FF

256

00  …

…  Порт

Порт

вывода

FF

Размер слова МП составляет 8 двоичных разрядов, поэтому разрядность всех регистров (кроме счетчика команд и указателя стековой памяти) составляет также 8 разрядов.

Для команд косвенной адресации и удвоенной длины слова РОН могут объединяться в пары BC, DE, HL. HL – индексный регистр. Служит для регистрово-косвенного способа адресации.

В регистрах B, D, H находится старший байт слова. C, D, E – младшие байты. F – регистр флагов и условий, использует 5 байтов из 8.

PC и SP – по 16 разрядов.