Методичка ЛР

.pdf

Дозволяючий вхід? Компонент має дозволяючий вхід, коли значення цього атрибута так. Цей атрибут потрібний в основному для підтримки схем, побудованих з використанням старіших версій Logisim, які не передбачали дозволяючий вхід.

Хід виконання:

1.Вивчити теоретичний матеріал.

2.Побудувати лінійний дешифратор за таблицею істинності, схему додати до звіту.

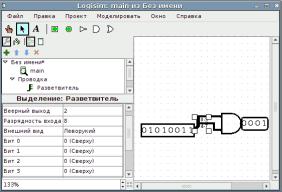

3.Побудувати повний лінійний дешифратор на три входи. Побудувати таблицю істинності, логічні рівняння та схему дешифратора використовуючи автоматизацію Logisim. Схему, рівняння і таблицю навести у звіті.

4.Побудувати наступний прямокутний дешифратор. Схему навести у звіті.

5.Розробити каскадний дешифратор за допомогою елементів «Декодер». (З’єднати два трирозрядні дешифратори для декодування чотирирозрядного коду). Схему навести у звіті.

6.Для візуального відображення роботи дешифратора створити комбінаційну схему з генератора тактових імпульсів, регістра, дешифратора (3→8) та семисегментного індикатора, які поєднуються таким чином, що при зміні значення регістра і подачі тактового сигналу змінюється вигляд семисегментного індикатора.

Контрольні питання:

1.Який дешифратор називають повним?

2.Що таке пірамідальні дешифратори?

3.Що таке стробуючий вхід у дешифраторі?

21

Лабораторна робота 4

Тема: Проектування та дослідження двійкових суматорів.

Мета: Дослідити можливості проектування однорозрядних та багаторозрядних двійкових суматорів у середовищі Logisim.

Зміст роботи: Ознайомлення з основними методами та прийомами проектування суматорів. Візуалізація результатів проектування.

Організаційні та методичні вказівки: Виконується в два етапи:

1-й етап – необхідно вивчити теоретичні відомості щодо основних прийомів проектування суматорів в Logisim.

2-й етап – виконати завдання.

Технічне забезпечення: ПК під ОС Windows, Logisim.

Час: 2 академічні години

Теоретичні відомості Загальна характеристика суматорів

Суматором називається функціональний вузол комп’ютера, призначений для додавання двох n-розрядних слів (чисел). Операція віднімання заміняється додаванням слів в оберненому або доповняльному коді. Операції множення та ділення зводяться до реалізації багаторазового додавання та зсування. Тому суматор є важливою частиною арифметикологічного пристрою. Функція суматора позначається буквами SM або X.

Однорозрядним суматором називається логічна схема, яка виконує додавання значень i-x розрядів Xi та Yi двійкових чисел з урахуванням перенесення Zi з молодшого сусіднього розряду та виробляє на виходах функції результат Si і перенесення Рi в старший сусідній розряд. На основі однорозрядних схем додавання на три входи та два виходи будуються багаторозрядні суматори будь-якого типу. Алгоритм роботи однорозрядного суматора відображається наступною таблицею істинності.

Багаторозрядний суматор складається з окремих схем, які називаються однорозрядними суматорами; вони виконують усі дії з додавання значень однойменних розрядів двох чисел (операндів).

У паралельних n-розрядних суматорах значення всіх розрядів операндів поступають одночасно на відповідні входи однорозрядних підсумовуючих схем. У послідовних суматорах значення розрядів операндів та перенесення, що запам’ятовувалися в минулому такті, поступають послідовно в напрямку від молодших розрядів до старших на входи одного однорозрядного суматора. В паралельно-послідовних суматорах числа розбиваються на частини, наприклад, байти, розряди байтів поступають на входи восьмирозрядного суматора паралельно (одночасно), а самі байти — послідовно, в напрямку від молодших до старших

22

байтів з урахуванням запам’ятованого перенесення.

У комбінаційних суматорах результат операції додавання запам’ятовується в регістрі результату. У накопичувальних суматорах процес додавання поєднується із зберіганням результату.

Елемент «двійковий суматор» в Logisim.

Поведінка

Цей компонент складає два значення, що надходять на західні входи і видає суму на східний вихід. Компонент розроблений таким чином, що його можна включати каскадно з іншими суматорами щоб забезпечити складання з більшою кількістю бітів, ніж можливо з одним суматором: вхід переносу надає однобітні значення, яке теж має бути додано до суми (якщо воно задане), а вихід перенесення надає однобітні значення переповнення, яке може бути подано на другий суматор. Якщо будь-який доданок містить кілька плаваючих бітів або кілька бітів з помилкою, то компонент виконає часткове складання. Тобто він буде обчислювати стільки молодших бітів, скільки можливо. Але вище плаваючого біта або біта з помилкою результат матиме плаваючі біти або біти з помилкою.

Контакти

Західний край, північний кінець (вхід, розрядність відповідає атрибуту Біти даних). Перше з двох значень для складання.

Західний край, південний кінець (вхід, розрядність відповідає атрибуту Біти даних). Друге значення для складання.

Північний край, відзначений «с in» (вхід, розрядність дорівнює 1). Значення переносу для додавання до суми. Якщо значення невідоме (наприклад, плаваюче), то передбачається, що воно дорівнює 0.

Східний край (вихід, розрядність відповідає атрибуту «Біти даних»). Молодші біти даних бітів суми двох значень, що надходять на західний край плюс біт «c in».

Південний край, відзначений «c out» (вихід, розрядність дорівнює 1). Біт перенесення, обчислений для суми.

Елемент «розгалужувач» в Logisim.

При роботі з багатобітними значеннями Вам часто захочеться направити різні біти за різними напрямками. Інструмент «Розгалужувач» з бібліотеки «Проводка» дозволяє вам вирішити це завдання. Наприклад, припустимо, що нам потрібна схема, яка обчислює побітове І між двома частинами її 8-бітного входу (старшими чотирма бітами і молодшими чотирма бітами). Ми будемо мати 8-бітне значення, яке надходить із вхідного контакту, і ми хочемо розділити його на два 4-бітних значення. На схемі нижче ми використовували для цього розгалужувач: 8-бітний вхід підводиться до розгалужувача, який розділяє 8 бітів на два 4- бітних значення, які потім подаються на елемент І, а з нього - на вихід.

23

У цьому прикладі розгалужувач поділяє вхідні значення на кілька вихідних значень. Але розгалужувачі також можуть працювати по-іншому: вони можуть об'єднувати кілька значень в одне значення. Насправді вони не мають напрямки: вони можуть пересилати значення один раз в одному напрямку, а пізніше - в іншому, вони навіть можуть робити і те й інше одночасно, як показано в прикладі нижче, де значення проходить на схід через два розгалужувача, потім направляється назад через них на захід, і потім назад на схід, де воно нарешті досягає виходу.

Ключ до розуміння розгалужувачів – їх атрибути.

Далі термін роз'єднаний кінець відноситься до одного з декількох проводів на одній стороні, а термін об'єднаний кінець відноситься до одиночного проводу на іншій стороні.

Атрибут Напрямок говорить про те, де повинні бути роз'єднані кінці по відношенню до об'єднаного кінця.

Атрибут Віяловий вихід визначає, скільки має бути роз'єднаних решт. Атрибут Розрядність входу визначає розрядність об'єднаного кінця.

Атрибут Біт x(0,1) визначає, який роз'єднаний кінець відповідає біту x об'єднаного кінця. Якщо кілька бітів відповідають одному й тому ж роз'єднаному кінцю, то їх відносний порядок буде тим же, що і в об'єднаному кінці.

Елемент «датчик» в Logisim. |

|

Датчик – елемент, який просто відображає значення в даній точці схеми. |

Він сам |

по собі не взаємодіє з іншими компонентами. У багатьох відносинах датчик |

дублює |

функціональність, властиву компоненту Контакт, налаштованому як вихід. Основна різниця в тому, що якщо схема використовується як підсхема, то вихідний контакт буде

частиною цього інтерфейсу, тоді як |

датчик не |

буде. Крім того, вони відрізняються тим, |

що датчик не має атрибута «Біти |

даних»: |

розрядність визначається із значення, що |

надходить на вхід компонента. Графічно вони схожі, але трохи відрізняються кордонами: контакт має товсту, чорну границю, у той час як датчик – тонку, сіру.

Непід’єднаний датчик

Датчик під’єднаний до 8-розрядного регістра

Датчик під’єднаний до 8-розрядного регістра

Хід виконання:

1.Вивчити теоретичний матеріал.

2.Побудувати однорозрядний суматор. Другий суматор побудувати виключно на елементах «І НЕ». Порівняти схеми за допомогою інструменту «Отримати статистику схеми»

зменю «Проект». Результат порівняння відобразити у звіті. Схеми додати до звіту.

3.Побудувати 4-розрядний паралельний суматор на базі 1-розрядних суматорів (використовуючи елемент Logisim суматор). У схему додати два регістри-джерела для доданків, які з’єднуються з суматором за допомогою розгалужувача та 4 датчики для відображення результату. Передбачити в схемі світлодіод, який вмикається при переповненні розрядної сітки в результаті додавання. Роботу схеми синхронізувати за допомогою генератору синхросигналів. Змінюючи значення в регістрах-джерелах, проконтролювати роботу суматора та відобразити результати у звіті. Схему навести у звіті.

24

4. Розробити схему каскадування суматорів. За допомогою двох 8-розрядних суматорів та розгалужувачів провести сумування значень двох 16-розрядних регістрів. Результат додавання помістити в 16-розрядний регістр. Додати у схему датчики для моніторингу проміжних результатів. Схему навести у звіті.

Контрольні питання:

1.Що таке напівсуматор?

2.Чим відрізняються комбінаційний суматор від накопичувального?

3.Порівняйте послідовний і паралельний суматор.

25

Лабораторна робота 5

Тема: Проектування та дослідження компараторів.

Мета: Дослідити можливості проектування однорозрядних та багаторозрядних компараторів у середовищі Logisim.

Зміст роботи: Ознайомлення з основними методами та прийомами проектування компараторів. Візуалізація результатів проектування.

Організаційні та методичні вказівки: Виконується в два етапи:

1-й етап – необхідно вивчити теоретичні відомості щодо основних прийомів проектування компараторів в Logisim.

2-й етап – виконати завдання.

Технічне забезпечення: ПК під ОС Windows, Logisim.

Час: 2 академічні години

Теоретичні відомості:

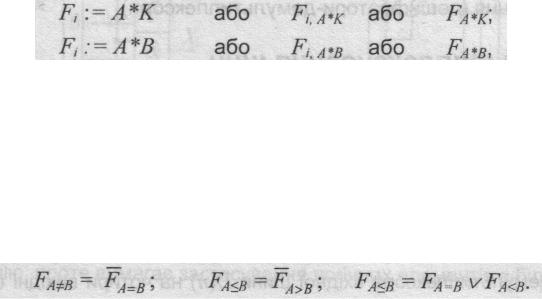

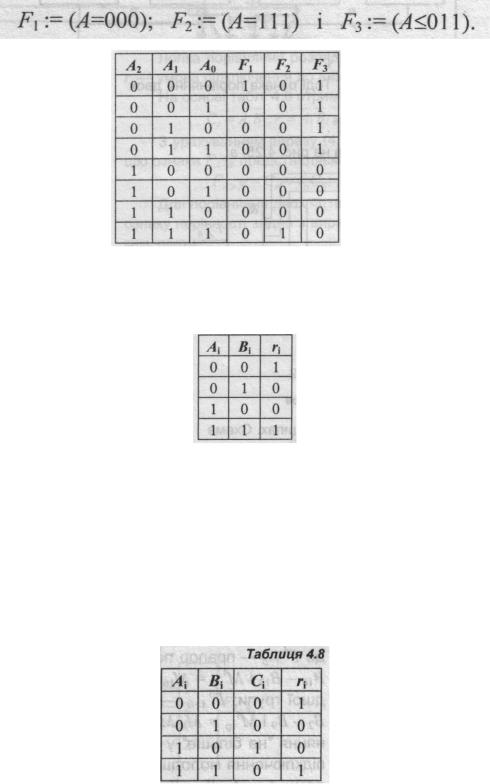

Схемою порівняння (компаратором) називається функціональний вузол комп'ютера, призначений для вироблення ознак відношень між двійковими словами (числами). Ознаки відношень записуються у вигляді:

де А і В — двійкові або двійково-десяткові числа; K — двійкова константа; і — номер відношення (часто пропускається); * - операція відношення вигляду =, ≠, <, >, ≤, ≥ і т. ін.; Fi

— функція, що задає результат відношення: лог. 1 — якщо відношення виконується, тобто істинне, і лог. 0 — якщо відношення не виконується, тобто помилкове. Функція компаратора позначається буквами COMP (comparator) або знаками = =.

Основними відношеннями вважаються: “рівне” FA=B, “більше” FA>B і “менше” FA<B. Часто схеми, що реалізують відношення FA>B або FA<B, називають схемами порівняння “на більше” або “на менше”. Маючи у своєму розпорядженні основні ознаки відношень, можна на їхній основі отримати ряд додаткових ознак, наприклад:

Ознаки відношення використовуються як логічні умови (повідомляючі сигнали) в мікропрограмах, командах передачі керування, а також у пристроях контролю і діагностики. Після виконання кожної команди в машині автоматично формуються ознаки результатів операції. Ці ознаки, які називаються прапорами (прапорцями), вміщуються в спеціальний регістр прапорів. До прапорів звичайно відносять ознаки нульового результату, переповнення розрядної сітки, знак результату, наявність перенесень із старшого розряду суматора, парне або непарне число одиниць в результаті та ін.

Зазначимо, що формування і використання ознак (прапорців) — це основна відмінність комп’ютера від калькулятора. Тільки за допомогою прапорців машина приймає рішення про хід обчислювального процесу, тобто володіє інтелектуальними властивостями.

26

Схеми порівняння двійкових слів А і В

Багаторозрядні двійкові слова рівні, коли одночасно попарно рівні всі їхні розряди, тобто А(п) = В(п), якщо Ai = Bi, і = 1, 2, n.

Схеми порівняння двох слів “на більше"

Схема порівняння двох слів А і В “на більше" за абсолютним значенням виробляє ознаку FA>B і будується за таким алгоритмом:

•аналіз нерівності слів А і В виконується послідовно в напрямку від старших розрядів до молодших;

•молодші розряди включаються в аналіз в тому випадку, коли старші розряди рівні (еквівалентні);

•для отримання ознаки РА>В будується диз'юнктивна сума порозрядних умов.

Компаратор у Logisim

Поведінка

Порівнює два значення як беззнакові або як доповнення до 2, залежно від атрибута Формат числа. Як правило, на одному з виходів буде 1, а на двох інших – 0.

Порівняння проводиться починаючи з найбільш значущих бітів у кожному числі, спускаючись вниз до місця, де знайдено два розрізняються значення. Однак, якщо в ході цього спуску зустрінеться значення помилки або плаваюче, то на всіх виходах буде значення помилки або плаваюче.

Контакти

Західний край, північний кінець (вхід, розрядність відповідає атрибуту Біти даних). Одне з двох значень для порівняння.

Західний край, південний кінець (вхід, розрядність відповідає атрибуту Біти даних). Друге значення для порівняння.

Східний край, відзначений> (вихід, розрядність дорівнює 1). На цьому виході 1, якщо значення на першому вході більше, ніж на другому, і 0, якщо менше або дорівнює.

Східний край, відзначений = (вихід, розрядність дорівнює 1). На цьому виході 1, якщо значення на першому вході дорівнює значенню на другому, і 0, якщо вони не рівні.

Східний край, відзначений <(вихід, розрядність дорівнює 1). На цьому виході 1, якщо значення на першому вході менше, ніж на другому, і 0, якщо більше або дорівнює.

Хід виконання:

1. Повторити теоретичний матеріал.

27

2. Побудувати схему порівняння двійкового слова A=A2A1A0 з наступними заданими константами:

Перевірити роботу схеми, результат перевірки записати у звіт. Схему додати до звіту.

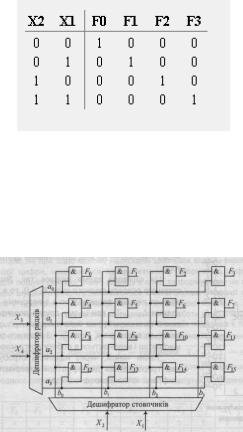

3. Побудувати однорозрядну схему схему порівняння двох слів А і В відповідно до наступної таблиці істинності.

Проаналізувати схему що отримали, та визначити один логічний елемент, який може замінити всі логічні вентилі, що використанні у схемі (висновок відобразити у звіті). На базі знайденого логічного елемента побудувати 4-розрядний компаратор. Як джерела для 4- розрядних слів А і В використати два регістри відповідної розрядності. Проаналізувати роботу схеми, висновки відобразити у звіті. Схеми додати до звіту.

4. Побудувати схему однорозрядного компаратора для порівняння двох слів на більше. Логіка порівняння розрядів А і В наведена в табл. 4.8, де Сі, — ознака A1>B1; ri — умова підключення до аналізу сусідніх молодших розрядів обох слів.

Після перевірки роботи схеми побудуйте на її базі 2-розрядну схему порівняння на більше, шляхом копіювання схеми і об’єднання двох схем в одну (При під’єднанні необхідно пам’ятати, що спочатку поєднуються старші розряди).

Проаналізувати роботу схеми, висновки відобразити у звіті. Схеми додати до звіту.

5. Побудувати 8-розрядний компаратор на базі елемента Logisim «Компаратор». Як джерела для 8-розрядних слів А і В використати два регістри відповідної розрядності.

Проаналізувати роботу схеми, висновки відобразити у звіті. Схеми додати до звіту.

28

Лабораторна робота 6

Тема: Проектування мультиплексорів та демультиплексорів.

Мета: Дослідити можливості проектування мультиплексорів та демультиплексорів у середовищі Logisim.

Зміст роботи: Ознайомлення з основними методами та прийомами проектування мультиплексорів та демультиплексорів. Візуалізація результатів проектування.

Організаційні та методичні вказівки: Виконується в два етапи:

1-й етап – необхідно вивчити теоретичні відомості щодо основних прийомів проектування мультиплексорів та демультиплексорів в Logisim.

2-й етап – виконати завдання.

Технічне забезпечення: ПК під ОС Windows, Logisim.

Час: 2 академічні години

Теоретична частина:

Мультиплексором називається функціональний вузол комп’ютера, призначений для почергової комутації (перемикання) інформації від одного з п входів на загальний вихід. Номер конкретної вхідної лінії, що підключається до виходу в кожний такт машинного часу, визначається адресним кодом A0, A1…Am-1. Зв’язок між числом інформаційних п і адресних т входів визначається співвідношенням п = 2т. Таким чином, мультиплексор реалізує керовану передачу даних від кількох вхідних ліній в одну вихідну.

Умовне графічне позначення мультиплексорів показане на рис. 4.12. Функція мультиплексорів записується буквами MUX (multiplexor).

Каскадування мультиплексорів

В інтегральному виконанні мультиплексори випускають на чотири, вісім або шістнадцять входів. Каскадування дозволяє реалізувати комутацію довільного числа вхідних ліній на базі серійних мікросхем мультиплексорів меншої розрядності.

Мультиплексування шин — це почергове перемикання шин (груп ліній) від кількох джерел інформації до одного приймача. Такі мікрооперації реалізуються схемами на основі мультиплексорів одиночних ліній. При виборі кількості й типу мультиплексорів враховують:

•число комутованих шин дорівнює 2т, де т — довжина адресного коду;

•i-й номер входу всіх мультиплексорів служить для підключення розрядів певної

однієї шини.

29

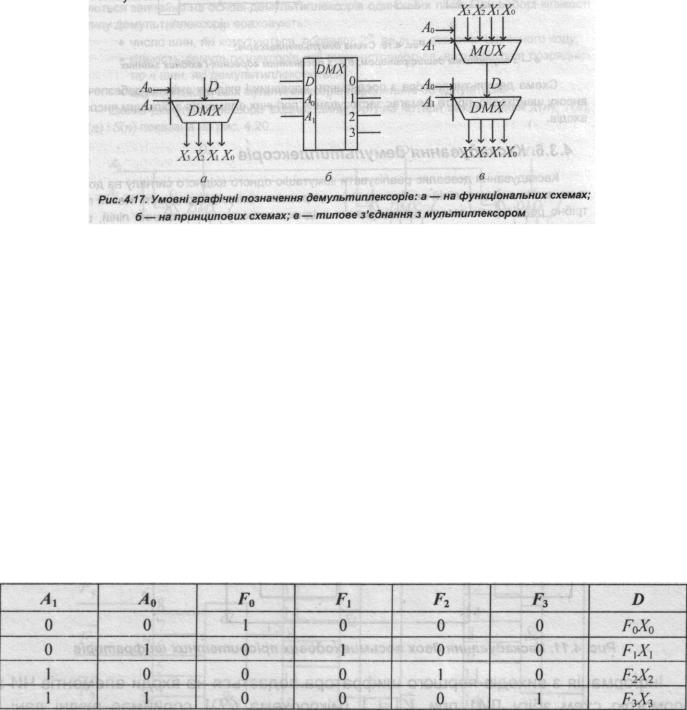

Загальна характеристика демультиплексорів

Демультиплексором називається функціональний вузол комп’ютера, призначений для комутації (перемикання) сигналу з одного інформаційного входу D на один з п інформаційних виходів. Номер виходу, на який в кожний такт машинного часу передається значення вхідного сигналу, визначається адресним кодом A0, A1, А2,…Ат-1. Адресні входи т та інформаційні виходи п пов’язані співвідношенням п = 2т або т = Log2п.

Демультиплексор виконує функцію, обернену функції мультиплексора. Стосовно мультиплексорів і демультиплексорів користуються також терміном “селектори” даних.

В умовних графічних позначеннях (рис. 4.17) функція демультиплексора позначається буквами DMX.

Демультиплексування шин

Під демультиплексуванням шин розуміється почергове перемикання груп ліній від одного джерела інформації до багатьох приймачів. Такі мікрооперації реалізуються звичайно на основі демультиплексорів одиночних ліній. При виборі кількості і типу демультиплексорів враховують:

•число шин, які комутуються, дорівнює 2m, де т — довжина адресного коду;

•кількість демультиплексорів, які використовуються, визначається розрядністю п шин, які демультиплексуються;

•адресні входи всіх мультиплексорів паралельно об’єднуються.

Хід виконання:

1.Повторити теоретичний матеріал.

2.Спроектувати мультиплексор, використовуючи логіку, наведену в Таблиці 1 , де A0, А1 — адресний код; F0, F1, F2, F3 — виходи внутрішнього дешифратора; Х0, X1 X2, X3 — вхідна інформація; D — загальний інформаційний вихід.

Таблиця 1. Логіка роботи мультиплексора на 4 входи

Схеми та таблицю істинності додати до звіту.

30