- •2. 5. Практическая реализация логических вентилей

- •2.5.1. Схемы кмоп

- •2.5.2. Задержка на распространение сигнала

- •2.5.3. Ограничения по входу и выходу

- •2. 6. Триггеры

- •2.6.1. Вентильные защелки

- •2.6.2. Двухступенчатые триггеры

- •2.6.3. Тактирование фронтом сигнала

- •2.6.4. Т-триггеры

- •2.6.5. Триггеры с дополнительными входами для установки и очистки

- •2.7. Регистры и сдвиговые регистры

- •2.8. Счетчики

- •2. 9. Дешифраторы

- •2. 10. Мультиплексоры

- •2. 11. Программируемые логические устройства

- •2.11.1. Программируемая логическая матрица

- •2.11.2. Программируемая матричная логика

- •2.11.3. Сложные программируемые логические устройства

- •2. 12. Программируемые вентильные матрицы

- •2.13. Последовательные схемы

- •2.13.1. Пример счетчика с прямым/обратным счетом

2.11.1. Программируемая логическая матрица

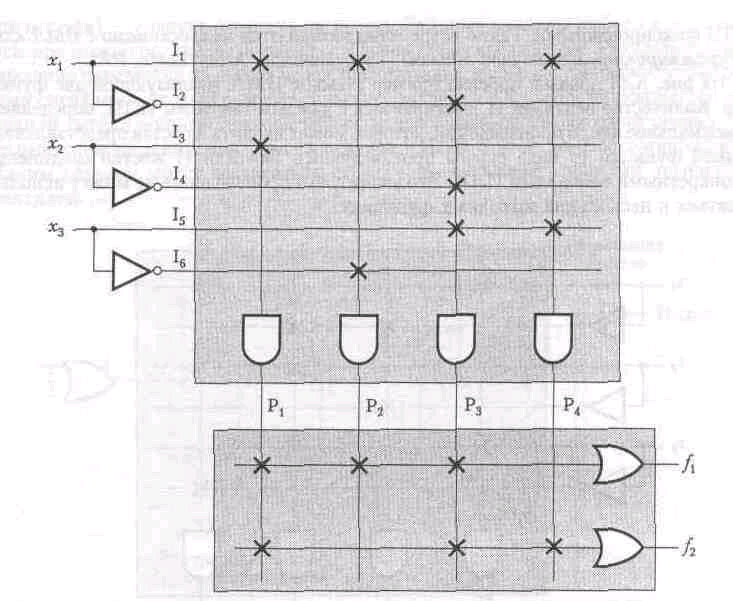

Схема, в которой соединения с массивами И и ИЛИ можно программировать, называется программируемой логической матрицей, ПЛМ (Programmable Logic Array, PLA). Структура такой схемы представлена на рис. 2.39. Программируемые соединения должны быть спроектированы таким образом, чтобы при отсутствии соединения с заданным входом вентиля И схема вела себя так, словно на этот вход подано значение 1 (следовательно, вход не будет влиять на произведение, вычисляемое данным вентилем). Аналогичным образом, при отсутствии соединения с заданным входом вентиля ИЛИ этот вход не должен воздействовать на выход вентиля (как если бы на него было подано логическое значение 0).

Программируемые соединения могут быть реализованы разными способами. Один из них состоит в том, чтобы расплавить перемычки в тех точках, где соединения не требуются. Для этого через определенные точки пропускается сильный ток. Кроме того, можно использовать транзисторные переключатели, управляемые стираемыми элементами памяти.

Простая программируемая логическая матрица, показанная на рис, 2.39, может генерировать до четырех термов-произведений на основе трех входных переменных. С их помощью могут быть реализованы две выходные функции. Некоторые термы могут использоваться в нескольких функциях. В данном случае ПЛМ сконфигурирована для реализации двух функций:

f1

=

![]()

f2

=

![]()

Для этих функций достаточно четырех термов, так как два из них будут использоваться обеими функциями. Реальные же ПЛМ имеют гораздо большие размеры.

Рис. 2.39. Функциональная структура ПЛМ

Рис. 2.40. Упрощенная схема ПЛМ, показанной на рис. 2.39

Хотя представленная выше схема прекрасно отражает базовые принципы функционирования ПЛМ, для описания больших матриц она неудобна. В технической литературе суммы и произведения нескольких переменных обычно обозначают значками с одним символическим входом. Линия, ведущая к этому входу, помечается крестиком х, указывающим на программируемое подключение. Это соглашение принято и для рис. 2.40, где приведена та же схема, что и на рис. 2.39. В общем случае соединение может быть создано в любой точке пересечения вертикальной и горизонтальной линий, что позволяет реализовать разные функции заданных входных переменных.

Структура ПЛМ очень эффективна с точки зрения занимаемой, ею площади на чипе интегральной микросхемы. Поэтому подобные структуры часто используются для реализации управляющих схем на чипах процессоров. В таком случае желаемые подключения создаются на последней стадии производственного процесса, а не после его завершения.

2.11.2. Программируемая матричная логика

В программируемой логической матрице программируются обе составляющие;

и матрица И, и матрица ИЛИ. На практике очень популярны похожие схемы, в которых входы матрицы И являются программируемыми, а соединения с матрицей ИЛИ фиксированными. Такие устройства называются микросхемами с ПМЛ или программируемой матричной логикой (Programmable Array Logic, PAL).

На рис. 2.41 показан простой пример схемы с ПМЛ, реализующей две функции. Количество вентилей И, соединенных с каждым вентилем ИЛИ, определяет максимальное число произведений, которое может входить в состав представления данной функции (в виде суммы произведений). Вентили И жестко соединены с конкретными вентилями ИЛИ. Это значит, что произведение не может использоваться в нескольких выходных функциях.

Рис. 2.41. Пример схемы с ПМЛ

Микросхемы ПМЛ выпускаются в разных конфигурациях. В них может быть много входных переменных и выходов, что позволяет на их основе реализовать очень сложные функции. Для большей гибкости на выходе вентилей ИЛИ в них включают триггеры. Таким образом, на одном чипе ПМЛ может быть реализована достаточно сложная логическая схема.

Насколько гибкими могут быть схемы на основе ПМЛ, можно судить по рис. 2.42. Здесь вычисляется значение функции f а затем мультиплексор определяет, какое ее значение — истинное, дополненное либо сохраненное (с предыдущего такта) — следует передать на выход. Входные сигналы выбора в мультиплексоре можно реализовать как программируемые соединения. Результирующее значение передается на выход через повторитель с тремя состояниями, управляемый сигналом, который разрешает выдачу значения. Обратите внимание, что выходной сигнал мультиплексора может использоваться как входной сигнал для термов-произведений или других вентилей ИЛИ в этой же ПМЛ-микросхеме. Таким образом могут создаваться схемы с несколькими уровнями логических вентилей.

Рис. 2.42. Пример обработки выходного сигнала ПМЛ-элемента