- •2. 5. Практическая реализация логических вентилей

- •2.5.1. Схемы кмоп

- •2.5.2. Задержка на распространение сигнала

- •2.5.3. Ограничения по входу и выходу

- •2. 6. Триггеры

- •2.6.1. Вентильные защелки

- •2.6.2. Двухступенчатые триггеры

- •2.6.3. Тактирование фронтом сигнала

- •2.6.4. Т-триггеры

- •2.6.5. Триггеры с дополнительными входами для установки и очистки

- •2.7. Регистры и сдвиговые регистры

- •2.8. Счетчики

- •2. 9. Дешифраторы

- •2. 10. Мультиплексоры

- •2. 11. Программируемые логические устройства

- •2.11.1. Программируемая логическая матрица

- •2.11.2. Программируемая матричная логика

- •2.11.3. Сложные программируемые логические устройства

- •2. 12. Программируемые вентильные матрицы

- •2.13. Последовательные схемы

- •2.13.1. Пример счетчика с прямым/обратным счетом

2.5.2. Задержка на распространение сигнала

В электронных логических схемах переключение из одного состояния в другое происходит не мгновенно. Поэтому скорость работы схемы определяется тем, насколько быстро может измениться ее состояние. Соответствующий параметр схемы называется задержкой на распространение сигнала. Как он вычисляется, показано на рис. 2.21. Выходное состояние изменяется с некоторой задержкой относительно момента изменения входного состояния. Обычно задержка определяется как интервал времени между точками, лежащими посередине графиков переходных характеристик входного и выходного сигналов (рис. 2.21). Еще одной важной характеристикой схемы является время перехода, измеряемое как время между точками с 10- и 90-процентным изменением сигнала. С увеличением задержки на распространение сигнала по различным маршрутам максимальная скорость функционирования логической схемы снижается.

Рис. 2.20. Передаточная характеристика КМОП-инвертора

Рис. 2.21. Задержка на распространение сигнала и время перехода

2.5.3. Ограничения по входу и выходу

Количество входов логического вентиля называется его нагрузочной способностью по входу или коэффициентом объединения по входу (fan-in). Количество входов логических вентилей, с которыми соединен выход данного вентиля, называется его нагрузочной способностью по выходу или коэффициентом разветвления по выходу (fan-out). В реальных микросхемах значения этих двух параметров невелики, поскольку с их увеличением возрастает задержка на распространение сигнала, а следовательно, снижается скорость работы схемы. Каждый транзистор повышает общее сопротивление вентиля в КМОП-схеме, а с увеличением сопротивления работа схемы замедляется и такие ее характеристики, как уровни сигнала и запас помехоустойчивости, ухудшаются. Поэтому нагрузочную способность по входу и по выходу обычно ограничивают до значений, не превышающих 10. Если исходная схема предполагает наличие вентиля с большим количеством входов, в нее просто добавляют еще один вентиль того же типа. Пример каскадирования однотипных вентилей вы видели на рис. 2.9. Если же количество выходов вентиля превышает допустимый предел, можно просто использовать две копии этого вентиля.

2. 6. Триггеры

Большинству устройств, в которых задействована цифровая логика, требуются элементы для хранения информации. Например, схема управления кодовым замком должна запоминать последовательность открывающего его набора цифр. Еще один важный пример — электронная память для хранения данных, необходимая цифровым компьютерам. Базовый электронный элемент, используемый для хранения информации, называется защелкой (latch).

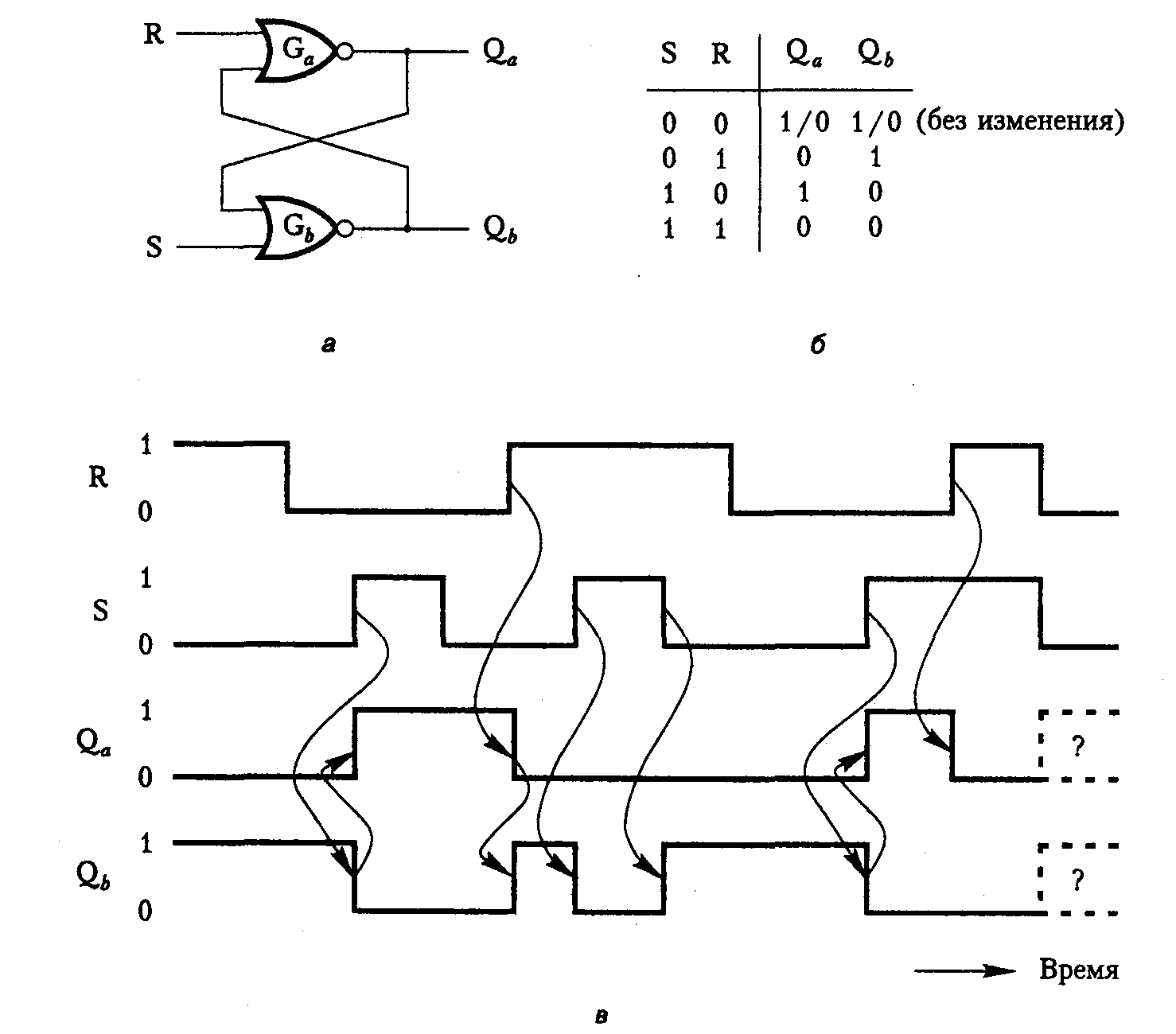

Давайте рассмотрим два вентиля ИЛИ-НЕ с перекрестным соединением, показанные на рис. 2.24, а. Начнем с ситуации, когда R = 1, а S = 0. Очевидно, что в этом случае Qa = 0, а Qb - 1. Сигналы на обоих входах вентиля Ga равны 1. Поэтому, если сигнал на входе R изменить на 0, на выходах Qa и Qb, ничего не изменится. Но если сигнал на входе R изменить на 0, а сигнал на входе S — на 1, то на выходах Qa и Qb появятся соответственно значения 1 и 0, причем они будут сохраняться даже после того, как сигнал на входе S снова станет равным 0. Описанная логическая схема представляет собой запоминающий элемент или защелку — она запоминает, на каком из двух входов (R или S) подавался последний сигнал 1.

Рис. 2.24. Защелка на основе вентилей ИЛИ-НЕ: логическая схема (а);

таблица истинности (б); временная диаграмма (в)

Таблица истинности этой схемы приведена на рис. 2.24, б. На рис. 2.24, в представлены простейшие временные диаграммы прохождения сигналов через защелку. Стрелки показывают причинно-следственные отношения между сигналами. Обратите внимание, что когда значения на входах R и S одновременно изменяются с 1 на 0, результирующее состояние не определено. На практике защелка перейдет в одно из двух своих стабильных состояний, но в какое именно — предсказать невозможно. Комбинация входных значений R = S = 1 в подобных защелках обычно не используется.

В соответствии с

принципом действия данной электронной

схемы ее контакты S и R называют входами

установки

и сброса

(set

и reset

соответственно, откуда и их обозначения).

Поскольку значения R = S = 1 обычно не

используются, выходы Qa

и Qb

обозначаются

как Q

и ![]() .Однако обозначение

.Однако обозначение

![]() ,

является просто символом, указывающим

на второй выход защелки, а вовсе не

дополнением сигнала Q, поскольку для

набора входных значений R = S = 1 на выходе

получается Q

=

,

является просто символом, указывающим

на второй выход защелки, а вовсе не

дополнением сигнала Q, поскольку для

набора входных значений R = S = 1 на выходе

получается Q

= ![]() = 0.

= 0.