- •2. 5. Практическая реализация логических вентилей

- •2.5.1. Схемы кмоп

- •2.5.2. Задержка на распространение сигнала

- •2.5.3. Ограничения по входу и выходу

- •2. 6. Триггеры

- •2.6.1. Вентильные защелки

- •2.6.2. Двухступенчатые триггеры

- •2.6.3. Тактирование фронтом сигнала

- •2.6.4. Т-триггеры

- •2.6.5. Триггеры с дополнительными входами для установки и очистки

- •2.7. Регистры и сдвиговые регистры

- •2.8. Счетчики

- •2. 9. Дешифраторы

- •2. 10. Мультиплексоры

- •2. 11. Программируемые логические устройства

- •2.11.1. Программируемая логическая матрица

- •2.11.2. Программируемая матричная логика

- •2.11.3. Сложные программируемые логические устройства

- •2. 12. Программируемые вентильные матрицы

- •2.13. Последовательные схемы

- •2.13.1. Пример счетчика с прямым/обратным счетом

2.6.3. Тактирование фронтом сигнала

Триггер называется тактируемым фронтом сигнала, если поданные на его вход данные передаются на выход только в момент изменения тактового сигнала. Все остальное время вход и выход изолированы друг от друга. Термины тактируемый положительным (передним) фронтом сигнала и тактируемый отрицательным (задним) фронтом сигнала относятся к триггерам, в которых передача данных происходит в ответ на изменение тактового сигнала соответственно с 0 на 1 и с 1 на 0. Для корректного функционирования триггера, тактируемого фронтом сигнала, необходимо, чтобы фронт тактового сигнала был четко определен и имел очень малое время перехода. На рис. А.28 изображен двухступенчатый триггер, тактируемый отрицательным фронтом сигнала.

2.6.4. Т-триггеры

Наиболее часто используемым типом триггеров являются D-триггеры, поскольку они могут использоваться для временного хранения данных. Однако во многих случаях требуются триггеры других типов. Например, схемы счетчиков эффективнее реализуются на основе триггеров типа Т. Состояние Т-триггера изменяется на каждом такте, если на его вход Т подается значение 1. Говорят, что такой триггер «переключает» свое состояние.

Схема Т-триггера, а также его таблица истинности, графическое обозначение, пример временной диаграммы представлены на рис. 2.З0, а. Как следует из рисунка, в основе Т-триггера лежит D-триггер. Обратите внимание, что D-триггер тактируется положительным фронтом сигнала.

Рис. 2.30. Т-триггер: схема (а); таблица истинности (б); графическое обозначение (в);

временная диаграмма (г)

2.6.5. Триггеры с дополнительными входами для установки и очистки

Состояние триггера определяется его предшествующим состоянием и логическими значениями на входных терминалах. Иногда для триггера нужно задать конкретное состояние вне зависимости от его текущего состояния и значений на стандартных входах. Например, определенное состояние триггеров задается при включении компьютера. Обычно это означает, что значения на выходах всех триггеров устанавливаются в 0. Лишь в отдельных случаях они могут быть равными 1.

На рис. 2.31 показано,

как добавить в двухступенчатый D-триггер

управляющие сигналы установки и

очистки, которые переводят триггер в

состояние 1 или 0 независимо от сигналов

на входе D и на тактовом входе. Как видно

из схемы, на указанные входы подается

сигнал низкого уровня. Когда оба сигнала

на входах ![]() (установка)

и

(установка)

и ![]() (очистка)

равны 1, триггером, как обычно, управляют

входы Clock

и D. Когда на вход

(очистка)

равны 1, триггером, как обычно, управляют

входы Clock

и D. Когда на вход ![]() подается сигнал 0, триггер переходит в

состояние 1, а когда

подается сигнал 0, триггер переходит в

состояние 1, а когда ![]() - 0, триггер устанавливается в состояние

0. Управляющие сигналы установки и

очистки часто добавляются и в триггеры

других типов.

- 0, триггер устанавливается в состояние

0. Управляющие сигналы установки и

очистки часто добавляются и в триггеры

других типов.

Рис. 2.31. Двухступенчатый D-триггер с входами установки и очистки: схема (а);

графическое обозначение (б)

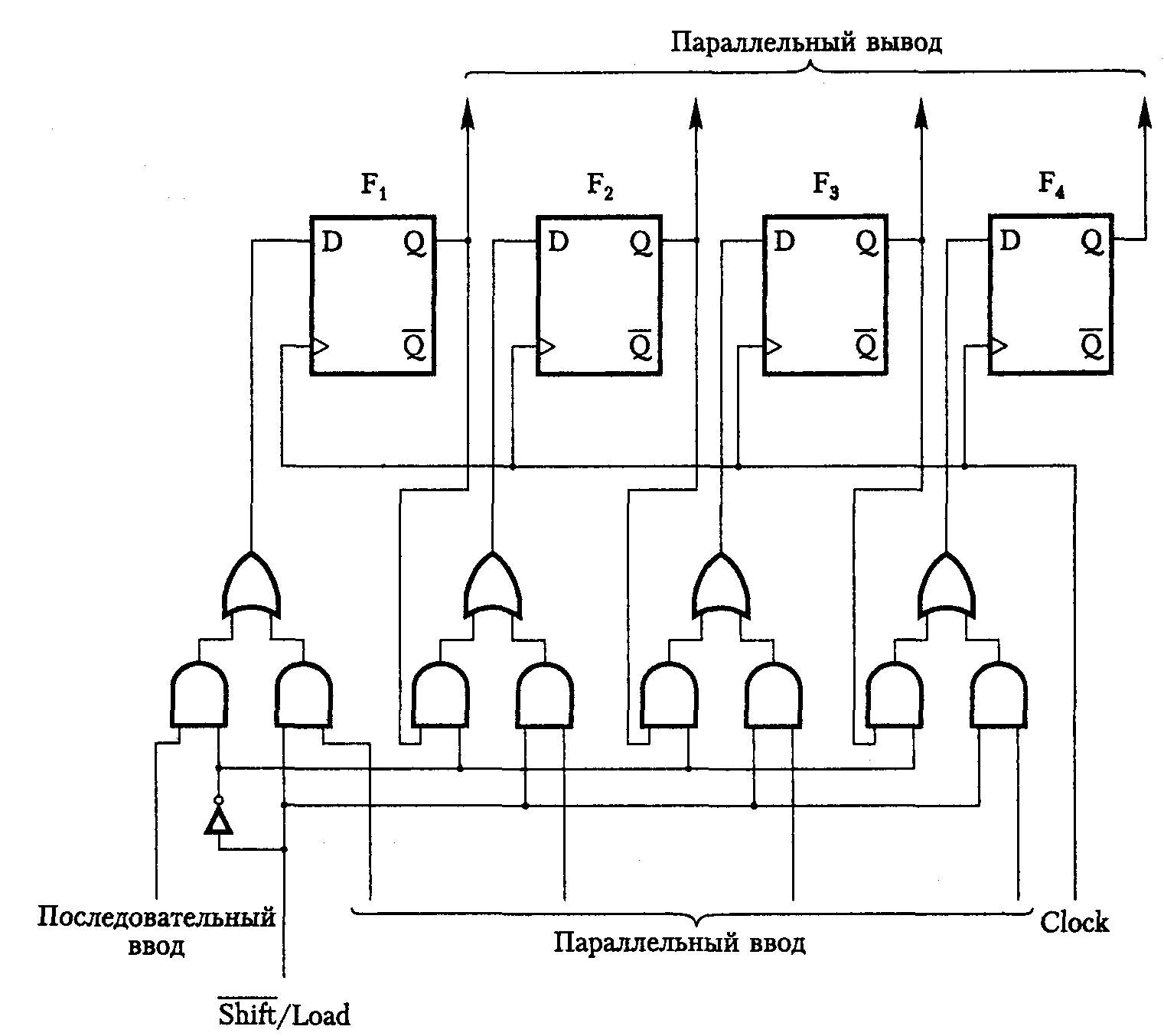

2.7. Регистры и сдвиговые регистры

2тдельный триггер может использоваться для хранения одного бита информации. Однако для машин, которые должны обрабатывать слова данных, состоящие из множества битов (обычно 64), удобнее объединить группу триггеров в стандартную структуру, называемую регистром. Работа триггеров, входящих в состав регистра, синхронизируется общим тактовым входом. Поэтому данные записываются (нагружаются) во все триггеры и считываются изо всех триггеров одновременно. В ходе обработки цифровых данных часто требуется сдвинуть или циклически прокрутить значения группы битов данных. Реализуются эти операции аппаратно. Простейшим механизмом для их выполнения является регистр, содержимое которого легко может быть сдвинуто вправо или влево на одну позицию за раз. В качестве примера рассмотрим 4-разрядный сдвиговый регистр, показанный на рис. 2.32, Он состоит из четырех D-триггеров, соединенных таким образом, что каждый тактовый импульс вызывает перемещение содержимого триггера Fi, в триггер Fi+1, в результате чего получается сдвиг вправо. Данные последовательно «вдвигаются в регистр и «выдвигаются» из него. Для выполнения циклического смещения данных достаточно соединить выход Out и вход In.

Для корректного функционирования сдвигового регистра необходимо, чтобы на каждый тактовый импульс его содержимое смещалось ровно на одну позицию. Это условие накладывает некоторые ограничения на запоминающие элементы, которые могут использоваться в сдвиговых регистрах. Например, вентильные защелки (рис. 2.27) для этой цели не подходят. При высоком уровне тактового сигнала значение на входе D немедленно передается на выход, а оттуда — на следующую защелку. В результате количество сдвигов на один тактовый импульс никак не контролируется. Поэтому сдвиговые регистры создаются на основе двухступенчатых триггеров или триггеров, тактируемых фронтом сигнала.

Рис. 2.З2. Простейший сдвиговый регистр

Интересной

разновидностью сдвигового регистра

является регистр, разряды которого

могут считываться и загружаться

параллельно. Для этого в него добавляются

дополнительные вентильные схемы (рис.

2.34), Загрузка данного регистра может

выполняться как последовательно, так

и параллельно. Когда на тактовый вход

регистра подается очередной импульс,

при условии, что ![]() /Load

= 0, выполняется сдвиг, а в противном

случае — параллельная загрузка регистра.

/Load

= 0, выполняется сдвиг, а в противном

случае — параллельная загрузка регистра.

Рис. 2.33. Сдвиговый регистр с параллельным доступом