- •2. 5. Практическая реализация логических вентилей

- •2.5.1. Схемы кмоп

- •2.5.2. Задержка на распространение сигнала

- •2.5.3. Ограничения по входу и выходу

- •2. 6. Триггеры

- •2.6.1. Вентильные защелки

- •2.6.2. Двухступенчатые триггеры

- •2.6.3. Тактирование фронтом сигнала

- •2.6.4. Т-триггеры

- •2.6.5. Триггеры с дополнительными входами для установки и очистки

- •2.7. Регистры и сдвиговые регистры

- •2.8. Счетчики

- •2. 9. Дешифраторы

- •2. 10. Мультиплексоры

- •2. 11. Программируемые логические устройства

- •2.11.1. Программируемая логическая матрица

- •2.11.2. Программируемая матричная логика

- •2.11.3. Сложные программируемые логические устройства

- •2. 12. Программируемые вентильные матрицы

- •2.13. Последовательные схемы

- •2.13.1. Пример счетчика с прямым/обратным счетом

2. 10. Мультиплексоры

В предыдущем разделе рассказывалось о дешифраторах, устанавливающих на основе входных сигналов значение 1 на одной из выходных линий. На выбранную линию дешифратор передает логическое значение 1, а на остальные — значение 0. Существует еще один очень полезный класс селекторных схем, предназначенный для выбора одного из n входов данных, значение которого передается на выход схемы. Выбор осуществляется на основе значений, поданных на так называемые входы выбора. Такие схемы называются мультиплексорами. Пример схемы мультиплексора приведен на рис. 2.36.

У данной схемы два входных сигнала выбора — w1 и w2. Четыре возможные комбинации их значений используются для выбора одного из входов данных (x1, x2, x3 или x4), значение которого передается на выход z. Очевидно, такую же структуру будут иметь и большие мультиплексоры, в которых k входных сигналов выбора используются для соединения одного из 2k входов данных с выходом. Типичной областью применения мультиплексоров является фильтрация данных, поступающих из множества разных источников. В частности, с помощью шестнадцати четырехвходовых мультиплексоров можно реализовать загрузку 16-разрядного регистра данных из одного из четырех источников.

Еще мультиплексоры

используются в качестве базовых элементов

для реализации логических функций.

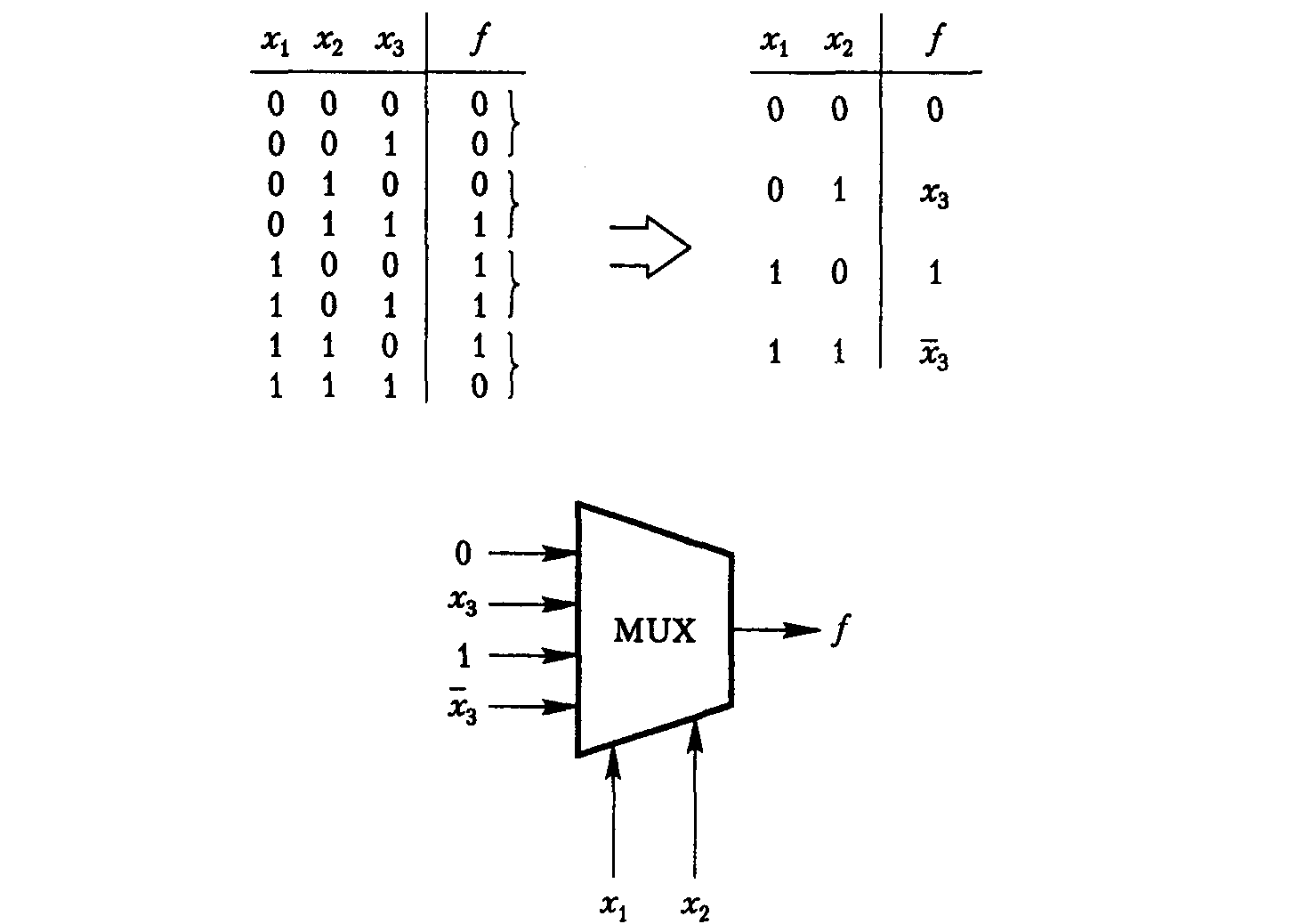

Для примера рассмотрим функцию f,

определяемую таблицей истинности,

приведенной на рис. 2.37. Чтобы упростить

эту функцию, переменные х1

и х2

следует рассматривать отдельно, как

показано на рисунке. Обратите внимание,

что для каждой пары значений переменных

х1

и х2

значение функции соответствует одному

из четырех термов: 0, 1, x3

или ![]() .

Это означает, что функцию можно реализовать

с помощью четырехвходовой мультиплексорной

схемы, где переменные х1

и х2

используются

для выбора одного из четырех

.

Это означает, что функцию можно реализовать

с помощью четырехвходовой мультиплексорной

схемы, где переменные х1

и х2

используются

для выбора одного из четырех

Рис. 2.36. Четырехвходовый мультиплексор

входных сигналов.

Далее, если на входы данных подаются

значения 0, 1, x3

или ![]() ,

то, согласно

таблице истинности, на выход мультиплексора

передается значение, соответствующее

функции f.

Это универсальный подход. Любую функцию

трех переменных можно реализовать с

помощью одного четырехвходового

мультиплексора. Любую функцию четырех

переменных подобным же образом можно

реализовать с помощью одного

восьмивходового мультиплексора и т. д.

,

то, согласно

таблице истинности, на выход мультиплексора

передается значение, соответствующее

функции f.

Это универсальный подход. Любую функцию

трех переменных можно реализовать с

помощью одного четырехвходового

мультиплексора. Любую функцию четырех

переменных подобным же образом можно

реализовать с помощью одного

восьмивходового мультиплексора и т. д.

Рис. 2.37. Реализация логической функции на основе мультиплексора

2. 11. Программируемые логические устройства

В разделах 2.2 и 2.З было показано, как можно любую логическую функцию представить в виде суммы произведений и реализовать с помощью схемы на основе вентилей И и ИЛИ. В разделе 2.10 рассказывалось о реализации логической функции с применением мультиплексора. Теперь же речь пойдет об еще одном классе схем, обычно используемом для этой же цели. Описанные здесь схемы состоят из массивов логических элементов, которые для получения заданной сумы произведений можно программировать. Такие схемы называются ПЛУ — программируемыми логическими устройствами (Programmable Logic Device, PLD).

Блок-схема программируемого логического устройства показана на рис. 2.38. У него n входных переменных (х,...,xn) и т выходных функций (f1, ...,fm). Каждая функция реализуется как сумма произведений входных переменных. Значения переменных x1, …, xn в исходной форме и в форме дополнений подаются на входы матрицы И, где из них формируется k термов-произведений. Оттуда они передаются в матрицу ИЛИ, где формируются выходные функции. В этом разделе описываются два наиболее распространенных типа программируемых логических устройств.

Рис. 2.38. Блок-схема ПЛУ