- •1. Основные параметры и характеристики логических элементов

- •2. Сравнительная оценка базовых логических элементов

- •3. Системы обозначений отечественных и зарубежных имс

- •4. Типы корпусов микросхем

- •5. Условные графические обозначения микросхем

- •6. Основы булевой алгебры

- •7. Аксиомы и законы булевой алгебры

- •8. Формы представления логических функций

- •9. Кнф, днф, сднф, скнф. Функционально полные системы логических функций

- •14.Метод минимизации Квайна и Мак-Класки.

- •15. Метод минимизации Квайна и Мак-Класки. Получение мкнф функции.

- •17 Комбинационныеустройства:Определение.Методика проектирования

- •18. Шифраторы

- •2.8. Дешифраторы

- •22. Преобразователи кодов

- •24. Мультиплексоры

- •25. Мультиплексорное дерево

- •26. Построение логических функций на мультифлексорах

- •27. Демультиплексоры

- •28. Сумматоры

- •30. Полусумматор

- •31. Многоразрядные двоичные сумматоры

- •33.Цифровые Компараторы

- •35 . Пороговые схемы, мажоритарные элементы

- •40.Реализация шифраторов, дешифраторов, мультиплексоров и демультиплексоров на плм.

- •41.Назначение и базовая структура пмл

- •42.Назначение и базовая структура бмк.

- •44. Триггеры: определение, общая структура кбя дбя, классификация по способу записи информации

- •46. Регистры

- •47. Функционирование регистров хранения. Схемы и условное графическое обозначение регистров хранения

- •48. Функционирование, схемы и условное графическое обозначение регистров сдвига

- •49. Счетчики

- •50. Последовательные счетчики

- •51. Параллельные счетчики.

- •52. Вычитающие и реверсивные синхронные двоичные счетчики

- •53. Синтез декадных синхронных счетчиков

- •54. Синтез синхронных двоичных счетчиков с переменным коэффициентом счета

- •55. Кольцевые счетчики

- •56. Определение генераторов кодов. Синтез генераторов кодов на основе счетчиков

- •57. Синтез генераторов кодов на основе сдвиговых регистров.

- •58. Определение делительной частоты. Синтез делителей частоты

- •60. Цифровые запоминающие устройства

- •61. Классификация запоминающих устройств по технологии выполнения и по способу обращения к массиву памяти. Основные параметры зу

- •62. Структура микросхем памяти с произвольной выборкой. Управляющие сигналы

- •63. Статические и динамические озу

- •64. Постоянные запоминающие устройства

- •65.Способы увеличения объема памяти запоминающих устройств

- •67. Основные характеристики цап и ацп

- •68. Цап с матрицей взвешенных коэффициентов

- •69. Цап с матрицей r-2r

- •70. Цап с весовым суммированием выходных сигналов

- •71. Области применения цап

- •72. Ацп времяимпульсного типа

- •73. Ацп с двойным интегрированием

- •74. Ацп параллельного преобразования (прямого преобразования)

- •75. Ацп последовательного счета (развертывающего типа)

- •76. Ацп следящего типа

- •77. Ацп последовательного приближения (поразрядного уравновешивания)

- •78. Классификация и области применения ацп

- •79. Схема выборки и хранения

- •80. Микропроцессор

- •81. Характеристики, достоинства и недостатки cisc-, risc-, vlim-

- •82. Характеристики, достоинства и недостатки Принстонской и Гарвардской архитектурой микропроцессоров.

- •84 Классификация микропроцессоров по функциональному признаку и количеству входящих в устройство бис.

- •85 Структура и состав микропроцессорных систем.

- •86. Системная шина. Шина адреса, шина данных, шина управления, их назначение и разрядность. Мультиплексированная шина адреса-данных.

- •90. Режим Примой доступ к памяти работы микропроцессора

- •91. Способы адресации операндов. Особенности способов адресации

- •92. Формат типовой команды микропроцессора.

- •93. Команды пересылки

- •94. Команды сдвига. Команды сравнения и тестирования.

- •95.Команды битовых операций. Операции управления программой

- •96. Структурная схема, физический интерфейс и условное графическое изображение однокристального микроконтроллера (мк) к1816ве48

- •97. Структурная организация центрального процессора мк к1816ве48

- •98.Организация память программ и данных мк к1816ве48.

- •99. Организация системы ввода-вывода мк к1816ве48

- •100. Организация систем подсчета времени, прерываний и синхронизации мк к1816ве48.

- •101. Средства расширения памяти программ мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •102. Средства расширения памяти данных мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •103 . Средства расширенияввода-вывода мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

103 . Средства расширенияввода-вывода мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

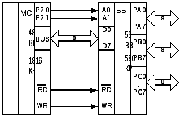

Система

с расширенным вводом-выводом.

Интерфейс расширения ввода-вывода

содержит 4-разрядную информационную

шину команд/данных P20–P23

и линию управления

.

Интерфейс активизируется по командам

.

Интерфейс активизируется по командам

MOVD A, Pp

MOVD Pp, A

ORLD Pp, A

ANLD Pp, A

Протокол

интерфейса состоит в передаче через

4-разрядный канал P20–P23

кода операции и данных обмена, которые

однозначно связаны с четырьмя

вышеуказанными командами. Состав линии

и временные диаграммы протокола приведены

на рис. 13. Управление обменом осуществляется

с помощью сигнала

,

срез которого синхронизирует передачу

кода операции обмена, а фронт – данных

обмена. В операциях участвует младшая

тетрада аккумулятора. При чтении портов

старшая тетрадаA

сбрасывается.

,

срез которого синхронизирует передачу

кода операции обмена, а фронт – данных

обмена. В операциях участвует младшая

тетрада аккумулятора. При чтении портов

старшая тетрадаA

сбрасывается.

Рис. 13. Интерфейс расширения ввода-вывода: а – состав; б – вывод данных;

в – ввод данных

На рис. 14 приведен вариант подключения устройства ввода-вывода к микроконтроллеру через порты программируемого параллельного интерфейса (ППИ) КР580ВВ55. Адресация порта ППИ производится через два младших разряда порта P2 (P20 и P21), передача байта данных – через порт BUS.

Рис. 14. Подключение устройств ввода–вывода через ППИ