- •1. Основные параметры и характеристики логических элементов

- •2. Сравнительная оценка базовых логических элементов

- •3. Системы обозначений отечественных и зарубежных имс

- •4. Типы корпусов микросхем

- •5. Условные графические обозначения микросхем

- •6. Основы булевой алгебры

- •7. Аксиомы и законы булевой алгебры

- •8. Формы представления логических функций

- •9. Кнф, днф, сднф, скнф. Функционально полные системы логических функций

- •14.Метод минимизации Квайна и Мак-Класки.

- •15. Метод минимизации Квайна и Мак-Класки. Получение мкнф функции.

- •17 Комбинационныеустройства:Определение.Методика проектирования

- •18. Шифраторы

- •2.8. Дешифраторы

- •22. Преобразователи кодов

- •24. Мультиплексоры

- •25. Мультиплексорное дерево

- •26. Построение логических функций на мультифлексорах

- •27. Демультиплексоры

- •28. Сумматоры

- •30. Полусумматор

- •31. Многоразрядные двоичные сумматоры

- •33.Цифровые Компараторы

- •35 . Пороговые схемы, мажоритарные элементы

- •40.Реализация шифраторов, дешифраторов, мультиплексоров и демультиплексоров на плм.

- •41.Назначение и базовая структура пмл

- •42.Назначение и базовая структура бмк.

- •44. Триггеры: определение, общая структура кбя дбя, классификация по способу записи информации

- •46. Регистры

- •47. Функционирование регистров хранения. Схемы и условное графическое обозначение регистров хранения

- •48. Функционирование, схемы и условное графическое обозначение регистров сдвига

- •49. Счетчики

- •50. Последовательные счетчики

- •51. Параллельные счетчики.

- •52. Вычитающие и реверсивные синхронные двоичные счетчики

- •53. Синтез декадных синхронных счетчиков

- •54. Синтез синхронных двоичных счетчиков с переменным коэффициентом счета

- •55. Кольцевые счетчики

- •56. Определение генераторов кодов. Синтез генераторов кодов на основе счетчиков

- •57. Синтез генераторов кодов на основе сдвиговых регистров.

- •58. Определение делительной частоты. Синтез делителей частоты

- •60. Цифровые запоминающие устройства

- •61. Классификация запоминающих устройств по технологии выполнения и по способу обращения к массиву памяти. Основные параметры зу

- •62. Структура микросхем памяти с произвольной выборкой. Управляющие сигналы

- •63. Статические и динамические озу

- •64. Постоянные запоминающие устройства

- •65.Способы увеличения объема памяти запоминающих устройств

- •67. Основные характеристики цап и ацп

- •68. Цап с матрицей взвешенных коэффициентов

- •69. Цап с матрицей r-2r

- •70. Цап с весовым суммированием выходных сигналов

- •71. Области применения цап

- •72. Ацп времяимпульсного типа

- •73. Ацп с двойным интегрированием

- •74. Ацп параллельного преобразования (прямого преобразования)

- •75. Ацп последовательного счета (развертывающего типа)

- •76. Ацп следящего типа

- •77. Ацп последовательного приближения (поразрядного уравновешивания)

- •78. Классификация и области применения ацп

- •79. Схема выборки и хранения

- •80. Микропроцессор

- •81. Характеристики, достоинства и недостатки cisc-, risc-, vlim-

- •82. Характеристики, достоинства и недостатки Принстонской и Гарвардской архитектурой микропроцессоров.

- •84 Классификация микропроцессоров по функциональному признаку и количеству входящих в устройство бис.

- •85 Структура и состав микропроцессорных систем.

- •86. Системная шина. Шина адреса, шина данных, шина управления, их назначение и разрядность. Мультиплексированная шина адреса-данных.

- •90. Режим Примой доступ к памяти работы микропроцессора

- •91. Способы адресации операндов. Особенности способов адресации

- •92. Формат типовой команды микропроцессора.

- •93. Команды пересылки

- •94. Команды сдвига. Команды сравнения и тестирования.

- •95.Команды битовых операций. Операции управления программой

- •96. Структурная схема, физический интерфейс и условное графическое изображение однокристального микроконтроллера (мк) к1816ве48

- •97. Структурная организация центрального процессора мк к1816ве48

- •98.Организация память программ и данных мк к1816ве48.

- •99. Организация системы ввода-вывода мк к1816ве48

- •100. Организация систем подсчета времени, прерываний и синхронизации мк к1816ве48.

- •101. Средства расширения памяти программ мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •102. Средства расширения памяти данных мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •103 . Средства расширенияввода-вывода мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

77. Ацп последовательного приближения (поразрядного уравновешивания)

Проиллюстрируем работу данного АЦП на примере упрощенной структурной схемы, показанной на рис. 7.14. Основой устройства является регистр последовательных приближений (РПП). Алгоритм его работы следующий. По каждому импульсу ГТИ РПП последовательно, начиная со старшего разряда, формирует на выходах Q сигнал логической 1, который в зависимости от сигнала, поступающего на его управляющий вход с выхода компаратора, либо остается неизменным, либо заменяется сигналом логического 0.

Рис. 7.14. Структурная схема АЦП последовательного приближения

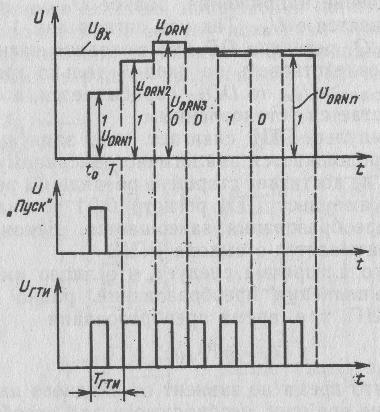

Работу АЦП рассмотрим с использованием временных диаграмм, приведенных на рис. 7.15.

Рис. 7.15. Временные диаграммы работы АЦП последовательного приближения

В

момент

по сигналу «Пуск» в выходной статический

регистр РПП, выполненный наRS-триггерах

по сигналу «Пуск» в выходной статический

регистр РПП, выполненный наRS-триггерах

записывается код, содержащий единицу

только в старшем разряде

записывается код, содержащий единицу

только в старшем разряде .

Этот код при помощи ЦАП преобразуется

в напряжение

.

Этот код при помощи ЦАП преобразуется

в напряжение ,

которое на входе компаратораDA

сравнивается с входным напряжением

устройства. Если

,

которое на входе компаратораDA

сравнивается с входным напряжением

устройства. Если

,

то на выходе компаратора формируется

единичный сигнал, если

,

то на выходе компаратора формируется

единичный сигнал, если – то нулевой сигнал.

– то нулевой сигнал.

Одновременно

сигналом «Пуск» в младший разряд

сдвигового регистраDD1

РПП по фронту ГТИ также записывается

сигнал логической единицы. Этот сигнал

открывает логический переключатель на

элементе 2И

сдвигового регистраDD1

РПП по фронту ГТИ также записывается

сигнал логической единицы. Этот сигнал

открывает логический переключатель на

элементе 2И

и выходной сигнал компаратора передается

на входR

триггера

и выходной сигнал компаратора передается

на входR

триггера

.

При этом, если

.

При этом, если ,

то триггер

,

то триггер сбрасывается и на выходе РПП формируется

нулевой код. В противном случае (

сбрасывается и на выходе РПП формируется

нулевой код. В противном случае ( )

триггер

)

триггер остается установленным и на выходе РПП

сохраняется код с единицей в старшем

разряде.

остается установленным и на выходе РПП

сохраняется код с единицей в старшем

разряде.

Следующий

фронт ГТИ сдвигает код, записанный в

DD1

влево. В результате этого сигнал

логической единицы перемещается в его

первый разряд ( ),

что устанавливает триггер

),

что устанавливает триггер .

На выходе РПП формируется код, содержащий

единицу в разряде

.

На выходе РПП формируется код, содержащий

единицу в разряде ,

а на выходе ЦАП – новое значение

напряжения, равное

,

а на выходе ЦАП – новое значение

напряжения, равное .

Это напряжение также сравнивается с

.

Это напряжение также сравнивается с .

Так как сигнал логической единицы

присутствует только на выходе

.

Так как сигнал логической единицы

присутствует только на выходе регистраDD1,

то выходной сигнал компаратора DA

может воздействовать на вход R

только триггера

регистраDD1,

то выходной сигнал компаратора DA

может воздействовать на вход R

только триггера

.

При этом, если

.

При этом, если ,

то

,

то сбрасывается, а если

сбрасывается, а если – триггер остается установленным.

– триггер остается установленным.

Следующий

импульс ГТИ сдвигает код, записанный в

DD1

влево и процесс продолжается аналогично

описанному до тех пор, пока сигнал

логической единицы не достигнет старшего

разряда

регистраDD1.

В этом случае по импульсу ГТИ регистр

DD1

устанавливается в нуль и процесс

преобразование завершается. Искомое

значение выходного кода считывается с

выхода РПП.

регистраDD1.

В этом случае по импульсу ГТИ регистр

DD1

устанавливается в нуль и процесс

преобразование завершается. Искомое

значение выходного кода считывается с

выхода РПП.

Из приведенного алгоритма следует, что число импульсов, необходимое для выполнения преобразования, равно разрядности выходного кода АЦП, т.е. время преобразования

(7.22)

(7.22)

Очевидно, что это время не зависит от входного напряжения и существенно меньше времени, необходимого для преобразования в АЦП последовательного счета.

Ввиду своей достаточной простоты и хорошего быстродействия данный тип АЦП находит широкое применение при разработке интегральных схем.

78. Классификация и области применения ацп

По структуре построения АЦП делятся на две группы:

1) АЦП, не содержащие ЦАП;

2) АЦП, содержащие ЦАП.

К первой группе относятся:

– АЦП времяимпульсного типа;

– АЦП с двойным интегрированием;

– АЦП параллельного преобразования (прямого преобразования);

Ко второй группе относятся:

– АЦП последовательного счета (развертывающего типа);

– АЦП следящего типа;

– АЦП последовательного приближения (поразрядного уравновешивания);

Каждый тип АЦП имеет свои достоинства и недостатки. На практике встречаются все выше перечисленные типы АЦП.

Основные направления и области применения АЦП кратко перечислены в табл. 5.2. В описании таблицы использованы следующие сокращения: ПС – АЦП последовательного счета; ПП – АЦП последовательного приближения; ПрП – АЦП прямого преобразования; И – АЦП двойного интегрирования; ПНЧ – преобразователь напряжение–частота.

В табл. 5.3 приведены основные параметры наиболее популярных АЦП.