- •1. Основные параметры и характеристики логических элементов

- •2. Сравнительная оценка базовых логических элементов

- •3. Системы обозначений отечественных и зарубежных имс

- •4. Типы корпусов микросхем

- •5. Условные графические обозначения микросхем

- •6. Основы булевой алгебры

- •7. Аксиомы и законы булевой алгебры

- •8. Формы представления логических функций

- •9. Кнф, днф, сднф, скнф. Функционально полные системы логических функций

- •14.Метод минимизации Квайна и Мак-Класки.

- •15. Метод минимизации Квайна и Мак-Класки. Получение мкнф функции.

- •17 Комбинационныеустройства:Определение.Методика проектирования

- •18. Шифраторы

- •2.8. Дешифраторы

- •22. Преобразователи кодов

- •24. Мультиплексоры

- •25. Мультиплексорное дерево

- •26. Построение логических функций на мультифлексорах

- •27. Демультиплексоры

- •28. Сумматоры

- •30. Полусумматор

- •31. Многоразрядные двоичные сумматоры

- •33.Цифровые Компараторы

- •35 . Пороговые схемы, мажоритарные элементы

- •40.Реализация шифраторов, дешифраторов, мультиплексоров и демультиплексоров на плм.

- •41.Назначение и базовая структура пмл

- •42.Назначение и базовая структура бмк.

- •44. Триггеры: определение, общая структура кбя дбя, классификация по способу записи информации

- •46. Регистры

- •47. Функционирование регистров хранения. Схемы и условное графическое обозначение регистров хранения

- •48. Функционирование, схемы и условное графическое обозначение регистров сдвига

- •49. Счетчики

- •50. Последовательные счетчики

- •51. Параллельные счетчики.

- •52. Вычитающие и реверсивные синхронные двоичные счетчики

- •53. Синтез декадных синхронных счетчиков

- •54. Синтез синхронных двоичных счетчиков с переменным коэффициентом счета

- •55. Кольцевые счетчики

- •56. Определение генераторов кодов. Синтез генераторов кодов на основе счетчиков

- •57. Синтез генераторов кодов на основе сдвиговых регистров.

- •58. Определение делительной частоты. Синтез делителей частоты

- •60. Цифровые запоминающие устройства

- •61. Классификация запоминающих устройств по технологии выполнения и по способу обращения к массиву памяти. Основные параметры зу

- •62. Структура микросхем памяти с произвольной выборкой. Управляющие сигналы

- •63. Статические и динамические озу

- •64. Постоянные запоминающие устройства

- •65.Способы увеличения объема памяти запоминающих устройств

- •67. Основные характеристики цап и ацп

- •68. Цап с матрицей взвешенных коэффициентов

- •69. Цап с матрицей r-2r

- •70. Цап с весовым суммированием выходных сигналов

- •71. Области применения цап

- •72. Ацп времяимпульсного типа

- •73. Ацп с двойным интегрированием

- •74. Ацп параллельного преобразования (прямого преобразования)

- •75. Ацп последовательного счета (развертывающего типа)

- •76. Ацп следящего типа

- •77. Ацп последовательного приближения (поразрядного уравновешивания)

- •78. Классификация и области применения ацп

- •79. Схема выборки и хранения

- •80. Микропроцессор

- •81. Характеристики, достоинства и недостатки cisc-, risc-, vlim-

- •82. Характеристики, достоинства и недостатки Принстонской и Гарвардской архитектурой микропроцессоров.

- •84 Классификация микропроцессоров по функциональному признаку и количеству входящих в устройство бис.

- •85 Структура и состав микропроцессорных систем.

- •86. Системная шина. Шина адреса, шина данных, шина управления, их назначение и разрядность. Мультиплексированная шина адреса-данных.

- •90. Режим Примой доступ к памяти работы микропроцессора

- •91. Способы адресации операндов. Особенности способов адресации

- •92. Формат типовой команды микропроцессора.

- •93. Команды пересылки

- •94. Команды сдвига. Команды сравнения и тестирования.

- •95.Команды битовых операций. Операции управления программой

- •96. Структурная схема, физический интерфейс и условное графическое изображение однокристального микроконтроллера (мк) к1816ве48

- •97. Структурная организация центрального процессора мк к1816ве48

- •98.Организация память программ и данных мк к1816ве48.

- •99. Организация системы ввода-вывода мк к1816ве48

- •100. Организация систем подсчета времени, прерываний и синхронизации мк к1816ве48.

- •101. Средства расширения памяти программ мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •102. Средства расширения памяти данных мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •103 . Средства расширенияввода-вывода мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

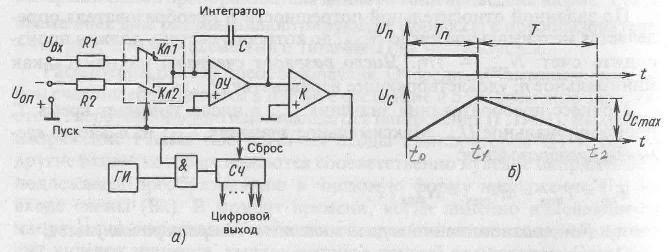

73. Ацп с двойным интегрированием

Схема АЦП приведена на рис. 7.9, а.

Рис. 7.9. Структурная схема АЦП с двойным интегрированием

Рассмотрим

работу преобразователя. В момент

(рис. 7.9, б) подачей импульса

(рис. 7.9, б) подачей импульса в цепь «Пуск» осуществляется запуск

схемы: сбрасывается в 0 счетчик Сч, первый

ключ Кл1 устанавливается в замкнутое

состояние, второй ключ Кл2 – в разомкнутое.

в цепь «Пуск» осуществляется запуск

схемы: сбрасывается в 0 счетчик Сч, первый

ключ Кл1 устанавливается в замкнутое

состояние, второй ключ Кл2 – в разомкнутое.

Предварительно

разряженный конденсатор

начинает заряжаться током от источника

входного напряжения

начинает заряжаться током от источника

входного напряжения .

Так как входное напряжение операционного

усилителя (ОУ) близко к нулю, практически

все напряжение

.

Так как входное напряжение операционного

усилителя (ОУ) близко к нулю, практически

все напряжение падает на резисторе

падает на резисторе и ток в цепи резистора

и ток в цепи резистора .

Этот ток замыкается через конденсатор

.

Этот ток замыкается через конденсатор .

Если за время длительности импульса

.

Если за время длительности импульса (

( )

значение напряжения

)

значение напряжения считать неизменным, конденсатор будет

заряжаться постоянным током и напряжение

на нем будет изменяться по линейному

закону, достигая к моменту

считать неизменным, конденсатор будет

заряжаться постоянным током и напряжение

на нем будет изменяться по линейному

закону, достигая к моменту значения

значения

. (7.15)

. (7.15)

В

момент окончания импульса на входе

«Пуск» (в момент

)

счетчик начинает счет импульсов,

поступающих в него из генератора

импульсной последовательности (ГИ)

через элемент И. В этот же момент ключ

Кл1 устанавливается в разомкнутое

состояние, ключ Кл2 – в замкнутое. В цепи

конденсатора возникает ток обратного

направления

)

счетчик начинает счет импульсов,

поступающих в него из генератора

импульсной последовательности (ГИ)

через элемент И. В этот же момент ключ

Кл1 устанавливается в разомкнутое

состояние, ключ Кл2 – в замкнутое. В цепи

конденсатора возникает ток обратного

направления .

Конденсатор разряжается постоянным

током

.

Конденсатор разряжается постоянным

током ,

и напряжение на нем снижается по линейному

закону. В момент

,

и напряжение на нем снижается по линейному

закону. В момент напряжение на конденсаторе

напряжение на конденсаторе и напряжение на выходе операционного

усилителя

и напряжение на выходе операционного

усилителя проходят нулевое значение, на выходе

компаратора К устанавливается уровень

логического 0, прекращается прохождение

импульсов ГИ через элемент И на вход

счетчика Сч. Образующееся к этому моменту

в Сч число

проходят нулевое значение, на выходе

компаратора К устанавливается уровень

логического 0, прекращается прохождение

импульсов ГИ через элемент И на вход

счетчика Сч. Образующееся к этому моменту

в Сч число есть значение

есть значение ,

представленное в цифровой форме.

,

представленное в цифровой форме.

Определим

значение

.

Время разряда конденсатора

.

Время разряда конденсатора

. (7.16)

. (7.16)

Подставляя

выражение для

,

получаем

,

получаем

. (7.17)

. (7.17)

Если

период следования импульсов ГИ равен

,

то количество импульсов

,

то количество импульсов ,

поступающих в счетчик за время

,

поступающих в счетчик за время ,

определится выражением

,

определится выражением

. (7.18)

. (7.18)

Как

видим,

пропорционально

пропорционально .

Величина

.

Величина

(7.19)

(7.19)

определяет

масштаб, в котором представляется

значение

.

.

74. Ацп параллельного преобразования (прямого преобразования)

Данный

тип АЦП реализует метод непосредственного

считывания и является на сегодняшний

день самым быстродействующим. Классический

принцип его работы поясняется рис. 5.10.

Устройство содержит

компараторов

компараторов ,

на объединенные инвертирующие входы

которых подается входной преобразуемый

сигнал. На неинвертирующие входы подаются

напряжения, численно равные уровням

квантования

,

на объединенные инвертирующие входы

которых подается входной преобразуемый

сигнал. На неинвертирующие входы подаются

напряжения, численно равные уровням

квантования .

В результате с выходов компараторов

снимается параллельный

.

В результате с выходов компараторов

снимается параллельный -разрядный

единичный код. Число единиц в нем равно

числу уровней квантования по величине

меньших значений

-разрядный

единичный код. Число единиц в нем равно

числу уровней квантования по величине

меньших значений .

.

Полученный

единичный код подается на вход

преобразователя кода (ПК), в котором он

преобразуется в двоичный с числом

разрядов

.

С выхода ПК двоичный код через логические

переключатели на элементах 2И подается

на вход статического регистра, с выхода

которого он и считывается. Перезапись

кода ПК в статический регистр происходит

по сигналу «Запись». Этот сигнал подается

в схему после того, как все переходные

процессы, связанные со срабатыванием

компараторов и получением двоичного

кода, завершены.

.

С выхода ПК двоичный код через логические

переключатели на элементах 2И подается

на вход статического регистра, с выхода

которого он и считывается. Перезапись

кода ПК в статический регистр происходит

по сигналу «Запись». Этот сигнал подается

в схему после того, как все переходные

процессы, связанные со срабатыванием

компараторов и получением двоичного

кода, завершены.

Рис. 7.10. Структурная схема АЦП параллельного преобразования

Для

получения напряжений, равных уровням

квантования в схеме использован делитель

напряжения на

одинаковых резисторах, подключенных к

выходу источника эталонного напряжения

одинаковых резисторах, подключенных к

выходу источника эталонного напряжения .

Формирование в данном АЦП выходного

кода одновременно по всем разрядам

предполагает получение максимально

возможного быстродействия. Его время

преобразования определяется только

структурой ПК и собственным быстродействием

используемой элементной базы.

.

Формирование в данном АЦП выходного

кода одновременно по всем разрядам

предполагает получение максимально

возможного быстродействия. Его время

преобразования определяется только

структурой ПК и собственным быстродействием

используемой элементной базы.