- •1. Основные параметры и характеристики логических элементов

- •2. Сравнительная оценка базовых логических элементов

- •3. Системы обозначений отечественных и зарубежных имс

- •4. Типы корпусов микросхем

- •5. Условные графические обозначения микросхем

- •6. Основы булевой алгебры

- •7. Аксиомы и законы булевой алгебры

- •8. Формы представления логических функций

- •9. Кнф, днф, сднф, скнф. Функционально полные системы логических функций

- •14.Метод минимизации Квайна и Мак-Класки.

- •15. Метод минимизации Квайна и Мак-Класки. Получение мкнф функции.

- •17 Комбинационныеустройства:Определение.Методика проектирования

- •18. Шифраторы

- •2.8. Дешифраторы

- •22. Преобразователи кодов

- •24. Мультиплексоры

- •25. Мультиплексорное дерево

- •26. Построение логических функций на мультифлексорах

- •27. Демультиплексоры

- •28. Сумматоры

- •30. Полусумматор

- •31. Многоразрядные двоичные сумматоры

- •33.Цифровые Компараторы

- •35 . Пороговые схемы, мажоритарные элементы

- •40.Реализация шифраторов, дешифраторов, мультиплексоров и демультиплексоров на плм.

- •41.Назначение и базовая структура пмл

- •42.Назначение и базовая структура бмк.

- •44. Триггеры: определение, общая структура кбя дбя, классификация по способу записи информации

- •46. Регистры

- •47. Функционирование регистров хранения. Схемы и условное графическое обозначение регистров хранения

- •48. Функционирование, схемы и условное графическое обозначение регистров сдвига

- •49. Счетчики

- •50. Последовательные счетчики

- •51. Параллельные счетчики.

- •52. Вычитающие и реверсивные синхронные двоичные счетчики

- •53. Синтез декадных синхронных счетчиков

- •54. Синтез синхронных двоичных счетчиков с переменным коэффициентом счета

- •55. Кольцевые счетчики

- •56. Определение генераторов кодов. Синтез генераторов кодов на основе счетчиков

- •57. Синтез генераторов кодов на основе сдвиговых регистров.

- •58. Определение делительной частоты. Синтез делителей частоты

- •60. Цифровые запоминающие устройства

- •61. Классификация запоминающих устройств по технологии выполнения и по способу обращения к массиву памяти. Основные параметры зу

- •62. Структура микросхем памяти с произвольной выборкой. Управляющие сигналы

- •63. Статические и динамические озу

- •64. Постоянные запоминающие устройства

- •65.Способы увеличения объема памяти запоминающих устройств

- •67. Основные характеристики цап и ацп

- •68. Цап с матрицей взвешенных коэффициентов

- •69. Цап с матрицей r-2r

- •70. Цап с весовым суммированием выходных сигналов

- •71. Области применения цап

- •72. Ацп времяимпульсного типа

- •73. Ацп с двойным интегрированием

- •74. Ацп параллельного преобразования (прямого преобразования)

- •75. Ацп последовательного счета (развертывающего типа)

- •76. Ацп следящего типа

- •77. Ацп последовательного приближения (поразрядного уравновешивания)

- •78. Классификация и области применения ацп

- •79. Схема выборки и хранения

- •80. Микропроцессор

- •81. Характеристики, достоинства и недостатки cisc-, risc-, vlim-

- •82. Характеристики, достоинства и недостатки Принстонской и Гарвардской архитектурой микропроцессоров.

- •84 Классификация микропроцессоров по функциональному признаку и количеству входящих в устройство бис.

- •85 Структура и состав микропроцессорных систем.

- •86. Системная шина. Шина адреса, шина данных, шина управления, их назначение и разрядность. Мультиплексированная шина адреса-данных.

- •90. Режим Примой доступ к памяти работы микропроцессора

- •91. Способы адресации операндов. Особенности способов адресации

- •92. Формат типовой команды микропроцессора.

- •93. Команды пересылки

- •94. Команды сдвига. Команды сравнения и тестирования.

- •95.Команды битовых операций. Операции управления программой

- •96. Структурная схема, физический интерфейс и условное графическое изображение однокристального микроконтроллера (мк) к1816ве48

- •97. Структурная организация центрального процессора мк к1816ве48

- •98.Организация память программ и данных мк к1816ве48.

- •99. Организация системы ввода-вывода мк к1816ве48

- •100. Организация систем подсчета времени, прерываний и синхронизации мк к1816ве48.

- •101. Средства расширения памяти программ мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •102. Средства расширения памяти данных мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •103 . Средства расширенияввода-вывода мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

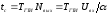

75. Ацп последовательного счета (развертывающего типа)

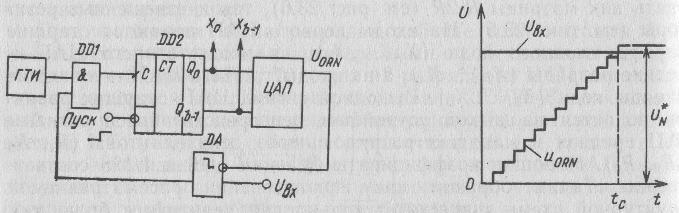

Принцип работы АЦП последовательного счета со счетчиком рассмотрим с использованием структурной схемы, показанной на рис. 5.11. Устройство содержит генератор тактовых импульсов (ГТИ), выход которого подключен к первому входу элемента 2И DD1. Выход элемента 2И соединен со счетным входом счетчика DD2, поразрядные выходы которого соединены с входами ЦАП. Выход ЦАП подключен к инвертирующему входу безгистерезисного компаратора DA, к неинвертирующему входу которого подключается источник входного напряжения, преобразуемого в код. Выход компаратора соединен со вторым входом элемента 2И DD1.

Рис. 7.11. Структурная схема АЦП последовательного счета

Работает

АЦП следующим образом. В исходном

состоянии на вход установки в нуль

счетчика DD2

подан активный логический сигнал.

Счетчик сброшен. Его выходной код равен

нулю. Равно нулю и выходное напряжение

ЦАП. Поэтому, если

,

то на выходе компаратора присутствует

сигнал логической 1 и тактовые импульсы

с выхода ГТИ через элемент 2ИDD1

поступают на вход C

счетчика. Однако, так как сигнал на входе

сброса R

равен 0, выходной код счетчика также

равен нулю.

,

то на выходе компаратора присутствует

сигнал логической 1 и тактовые импульсы

с выхода ГТИ через элемент 2ИDD1

поступают на вход C

счетчика. Однако, так как сигнал на входе

сброса R

равен 0, выходной код счетчика также

равен нулю.

Преобразование

начинается в момент снятия со входа R

активного логического сигнала (импульса

«Пуск»). В этом случае с приходом каждого

тактового импульса с выхода ГТИ счетчик

выполняет операцию инкремента. Его

выходной код начинает увеличиваться.

Соответственно увеличивается и выходное

напряжение ЦАП. Этот процесс продолжается

до тех пор, пока выходное напряжение

ЦАП не превысит величину

.

В этот момент компараторDA

сформирует на выходе сигнал логического

0. В результате на выходе элемента 2И DD1

также будет сформирован сигнал логического

нуля и увеличение выходного кода счетчика

прекратится. При этом значение выходного

кода счетчика будет прямо пропорционально

входному напряжению

.

В этот момент компараторDA

сформирует на выходе сигнал логического

0. В результате на выходе элемента 2И DD1

также будет сформирован сигнал логического

нуля и увеличение выходного кода счетчика

прекратится. При этом значение выходного

кода счетчика будет прямо пропорционально

входному напряжению

и обратно пропорционально абсолютной

разрешающей способности используемого

ЦАП

и обратно пропорционально абсолютной

разрешающей способности используемого

ЦАП

. (7.20)

. (7.20)

Так

как выходное напряжение ЦАП имеет форму

ступенчатой функции, то напряжение

,

найденное из (7.11), должно быть округлено

до ближайшего целого числа, соответствующего

номеру первого уровня

,

найденное из (7.11), должно быть округлено

до ближайшего целого числа, соответствующего

номеру первого уровня ,

превышающего значение

,

превышающего значение .

Для повторения цикла преобразования

необходимо импульсом «Пуск» счетчик

установить в нуль.

.

Для повторения цикла преобразования

необходимо импульсом «Пуск» счетчик

установить в нуль.

Очевидно,

что время преобразования в рассмотренном

АЦП прямо пропорционально его выходному

коду и периоду следования импульсов

ГТИ ( )

)

. (7.21)

. (7.21)

Рассмотренный режим работы называется циклическим, так как каждый раз импульс «Пуск» сбрасывает счетчик DD2 и поэтому счет (преобразование) всегда начинается с нуля.

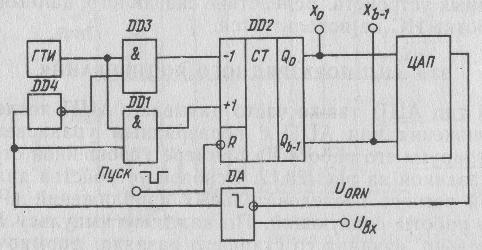

76. Ацп следящего типа

Если в АЦП использовать реверсивный счетчик, то можно реализовать нециклический режим работы, характеризующийся более высоким быстродействием. В этом случае на выходе счетчика постоянно присутствует код, пропорциональный текущему значению входного напряжения. Структурная схема АЦП, реализующего нециклический режим работы, показана на рис. 5.12.

Рис. 7.12. Структурная схема АЦП следящего типа

В отличие от АЦП, работающего в циклическом режиме, в схему дополнительно введены инвертор DD4 и еще один элемент 2И DD3.

Исходное

состояние схемы аналогично состоянию

циклического АЦП. Счетчик DD2

сброшен. Выходное напряжение ЦАП

и на вход «+1» счетчикаDD2

поступает последовательность выходных

импульсов ГТИ. При снятии активного

логического уровня с входа R

счетчика его выходной код начинает

увеличиваться. Увеличивается и выходное

напряжение ЦАП. Этот процесс протекает

до момента

и на вход «+1» счетчикаDD2

поступает последовательность выходных

импульсов ГТИ. При снятии активного

логического уровня с входа R

счетчика его выходной код начинает

увеличиваться. Увеличивается и выходное

напряжение ЦАП. Этот процесс протекает

до момента

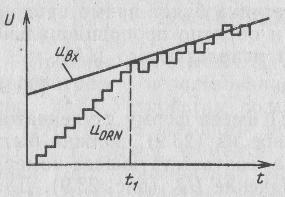

(рис. 5.13), в котором

(рис. 5.13), в котором .

Срабатывание компаратораDA

приводит к тому, что на выходе элемента

2И DD1

формируется пассивный для входа «+1»

счетчика DD2

сигнал. Одновременно инвертор DD4

формирует на нижнем входе элемента DD3

сигнал логической 1. В результате этого

на вход «–1» счетчика DD2

начинают поступать импульсы ГТИ. При

этом счетчик выполняет операцию

декремента и его выходной код начинает

уменьшаться. Уменьшается и напряжение

WFG.

В момент нарушения неравенства

.

Срабатывание компаратораDA

приводит к тому, что на выходе элемента

2И DD1

формируется пассивный для входа «+1»

счетчика DD2

сигнал. Одновременно инвертор DD4

формирует на нижнем входе элемента DD3

сигнал логической 1. В результате этого

на вход «–1» счетчика DD2

начинают поступать импульсы ГТИ. При

этом счетчик выполняет операцию

декремента и его выходной код начинает

уменьшаться. Уменьшается и напряжение

WFG.

В момент нарушения неравенства

происходит очередное переключение

компаратораDA

и счетчик начинает увеличивать свой

выходной код.

происходит очередное переключение

компаратораDA

и счетчик начинает увеличивать свой

выходной код.

Рис. 7.13. Временная диаграмма входного напряжения компаратора АЦП следящего типа

Таким

образом, с момента прихода импульса

«Пуск» до момента

АЦП последовательного счета и следящего

типа работают одинаково. Однако после

АЦП последовательного счета и следящего

типа работают одинаково. Однако после выходной код нециклического АЦП постоянно

следит за изменением входного напряжения,

что значительно снижает его время

преобразования.

выходной код нециклического АЦП постоянно

следит за изменением входного напряжения,

что значительно снижает его время

преобразования.

Общим

недостатком рассмотренных схем является

длительность интервала

,

в течение которого выходной код счетчика

должен достичь значения, эквивалентного

входному напряжению. Причем увеличение

точности требует увеличения разрядности

используемых счетчика и ЦАП и ведет к

падению быстродействия рассмотренных

устройств.

,

в течение которого выходной код счетчика

должен достичь значения, эквивалентного

входному напряжению. Причем увеличение

точности требует увеличения разрядности

используемых счетчика и ЦАП и ведет к

падению быстродействия рассмотренных

устройств.