- •1. Основные параметры и характеристики логических элементов

- •2. Сравнительная оценка базовых логических элементов

- •3. Системы обозначений отечественных и зарубежных имс

- •4. Типы корпусов микросхем

- •5. Условные графические обозначения микросхем

- •6. Основы булевой алгебры

- •7. Аксиомы и законы булевой алгебры

- •8. Формы представления логических функций

- •9. Кнф, днф, сднф, скнф. Функционально полные системы логических функций

- •14.Метод минимизации Квайна и Мак-Класки.

- •15. Метод минимизации Квайна и Мак-Класки. Получение мкнф функции.

- •17 Комбинационныеустройства:Определение.Методика проектирования

- •18. Шифраторы

- •2.8. Дешифраторы

- •22. Преобразователи кодов

- •24. Мультиплексоры

- •25. Мультиплексорное дерево

- •26. Построение логических функций на мультифлексорах

- •27. Демультиплексоры

- •28. Сумматоры

- •30. Полусумматор

- •31. Многоразрядные двоичные сумматоры

- •33.Цифровые Компараторы

- •35 . Пороговые схемы, мажоритарные элементы

- •40.Реализация шифраторов, дешифраторов, мультиплексоров и демультиплексоров на плм.

- •41.Назначение и базовая структура пмл

- •42.Назначение и базовая структура бмк.

- •44. Триггеры: определение, общая структура кбя дбя, классификация по способу записи информации

- •46. Регистры

- •47. Функционирование регистров хранения. Схемы и условное графическое обозначение регистров хранения

- •48. Функционирование, схемы и условное графическое обозначение регистров сдвига

- •49. Счетчики

- •50. Последовательные счетчики

- •51. Параллельные счетчики.

- •52. Вычитающие и реверсивные синхронные двоичные счетчики

- •53. Синтез декадных синхронных счетчиков

- •54. Синтез синхронных двоичных счетчиков с переменным коэффициентом счета

- •55. Кольцевые счетчики

- •56. Определение генераторов кодов. Синтез генераторов кодов на основе счетчиков

- •57. Синтез генераторов кодов на основе сдвиговых регистров.

- •58. Определение делительной частоты. Синтез делителей частоты

- •60. Цифровые запоминающие устройства

- •61. Классификация запоминающих устройств по технологии выполнения и по способу обращения к массиву памяти. Основные параметры зу

- •62. Структура микросхем памяти с произвольной выборкой. Управляющие сигналы

- •63. Статические и динамические озу

- •64. Постоянные запоминающие устройства

- •65.Способы увеличения объема памяти запоминающих устройств

- •67. Основные характеристики цап и ацп

- •68. Цап с матрицей взвешенных коэффициентов

- •69. Цап с матрицей r-2r

- •70. Цап с весовым суммированием выходных сигналов

- •71. Области применения цап

- •72. Ацп времяимпульсного типа

- •73. Ацп с двойным интегрированием

- •74. Ацп параллельного преобразования (прямого преобразования)

- •75. Ацп последовательного счета (развертывающего типа)

- •76. Ацп следящего типа

- •77. Ацп последовательного приближения (поразрядного уравновешивания)

- •78. Классификация и области применения ацп

- •79. Схема выборки и хранения

- •80. Микропроцессор

- •81. Характеристики, достоинства и недостатки cisc-, risc-, vlim-

- •82. Характеристики, достоинства и недостатки Принстонской и Гарвардской архитектурой микропроцессоров.

- •84 Классификация микропроцессоров по функциональному признаку и количеству входящих в устройство бис.

- •85 Структура и состав микропроцессорных систем.

- •86. Системная шина. Шина адреса, шина данных, шина управления, их назначение и разрядность. Мультиплексированная шина адреса-данных.

- •90. Режим Примой доступ к памяти работы микропроцессора

- •91. Способы адресации операндов. Особенности способов адресации

- •92. Формат типовой команды микропроцессора.

- •93. Команды пересылки

- •94. Команды сдвига. Команды сравнения и тестирования.

- •95.Команды битовых операций. Операции управления программой

- •96. Структурная схема, физический интерфейс и условное графическое изображение однокристального микроконтроллера (мк) к1816ве48

- •97. Структурная организация центрального процессора мк к1816ве48

- •98.Организация память программ и данных мк к1816ве48.

- •99. Организация системы ввода-вывода мк к1816ве48

- •100. Организация систем подсчета времени, прерываний и синхронизации мк к1816ве48.

- •101. Средства расширения памяти программ мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •102. Средства расширения памяти данных мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •103 . Средства расширенияввода-вывода мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

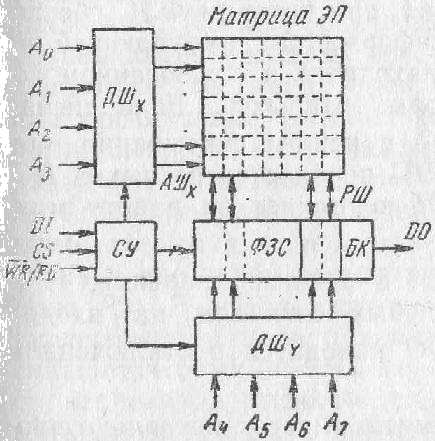

62. Структура микросхем памяти с произвольной выборкой. Управляющие сигналы

Типовая

структура микросхем памяти с произвольным

обращением показана на рис. 6.1. Накопитель

представляет собой прямоугольную

матрицу элементов памяти (ЭП), содержащую

строк и

строк и столбцов. Таким образом, емкость

накопителя

столбцов. Таким образом, емкость

накопителя .

Каждый ЭП подключен к адресным (АШ) и

разрядным (РШ) шинам. Выбор необходимого

ЭП осуществляется путем подачи

определенной комбинации адресных

переменных (

.

Каждый ЭП подключен к адресным (АШ) и

разрядным (РШ) шинам. Выбор необходимого

ЭП осуществляется путем подачи

определенной комбинации адресных

переменных ( ).

Адресные дешифраторы строк (ДШX)

и столбцов (ДШY)

формируют сигналы выборки на соответствующих

АШ, которые определяют строку и столбец

накопителя, в которых расположен

выбираемый ЭП. Таким образом,

).

Адресные дешифраторы строк (ДШX)

и столбцов (ДШY)

формируют сигналы выборки на соответствующих

АШ, которые определяют строку и столбец

накопителя, в которых расположен

выбираемый ЭП. Таким образом,

адресных входов позволяют выбрать один

из

адресных входов позволяют выбрать один

из элементов памяти.

элементов памяти.

Запись

или считывание информации в выбранном

ЭП осуществляется с помощью

формирователей сигналов записи-считывания

(ФЗС), каждый из которых подключается к

РШ одного из столбцов накопителя.

Выходные сигналы дешифратора ДШ,

поступают по АШ на ФЗС, разрешая работу

одного из них в режиме записи или

считывания. В режиме записи выбранных

ФЗС формирует на подключенный к нему

РШ сигнал, устанавливающий ЭП, расположенный

в строке, на которую подан сигнал выборки

с выхода ДШX,

в состояние 0 или 1 в зависимости от

потенциала, поступающего на вход данных

формирователей сигналов записи-считывания

(ФЗС), каждый из которых подключается к

РШ одного из столбцов накопителя.

Выходные сигналы дешифратора ДШ,

поступают по АШ на ФЗС, разрешая работу

одного из них в режиме записи или

считывания. В режиме записи выбранных

ФЗС формирует на подключенный к нему

РШ сигнал, устанавливающий ЭП, расположенный

в строке, на которую подан сигнал выборки

с выхода ДШX,

в состояние 0 или 1 в зависимости от

потенциала, поступающего на вход данных

(Data

Input).

В режиме считывания соответствующий

ФЗС воспринимает сигнал, поступающий

на РШ от выбранного ЭП. Этот сигнал,

указывающий состояние ЭП (0 или 1),

усиливается ФЗС и передается на выход

данных

(Data

Input).

В режиме считывания соответствующий

ФЗС воспринимает сигнал, поступающий

на РШ от выбранного ЭП. Этот сигнал,

указывающий состояние ЭП (0 или 1),

усиливается ФЗС и передается на выход

данных

(Data

Output)

через буферный каскад (БК), в качестве

которого обычно используются каскады

с открытым коллектором или с тремя

состояниями.

(Data

Output)

через буферный каскад (БК), в качестве

которого обычно используются каскады

с открытым коллектором или с тремя

состояниями.

Рис. 6.1. Общая структура микросхем памяти с произвольной выборкой

Схема

управления (СУ) определяет режим работы

схемы ОЗУ. По сигналу

разрешаются или запрещаются операции

записи или чтения. Сигнал

разрешаются или запрещаются операции

записи или чтения. Сигнал позволяет выбрать требуемую микросхему

памяти в ЗУ, состоящим из ряда микросхем.

Подача сигнала на вход

позволяет выбрать требуемую микросхему

памяти в ЗУ, состоящим из ряда микросхем.

Подача сигнала на вход при наличии сигнала

при наличии сигнала выбора микросхемы позволяет выбрать

режим записи, если

выбора микросхемы позволяет выбрать

режим записи, если ,

или считывания, если

,

или считывания, если .

При

.

При микросхема находится в режиме хранения,

т.е. состояние ЭП не меняется при любых

сигналах на входах

микросхема находится в режиме хранения,

т.е. состояние ЭП не меняется при любых

сигналах на входах ,

, ,

, .

Выход

.

Выход находится в отключенном состоянии. В

некоторых типах микросхем памяти имеется

несколько входов

находится в отключенном состоянии. В

некоторых типах микросхем памяти имеется

несколько входов :

: ,

, ,

…. При этом выбор микросхемы производится

при выполнении определенной логической

функции, например

,

…. При этом выбор микросхемы производится

при выполнении определенной логической

функции, например .

.

Для

уменьшения числа выводов обычно

используются комбинированные

(двунаправленные) выводы

,

которые при записи работают как входы

,

которые при записи работают как входы ,

а при считывании – как выходы

,

а при считывании – как выходы .

При этом часто вводится дополнительный

вход разрешения выдачи

.

При этом часто вводится дополнительный

вход разрешения выдачи (Output

Enable).

При сигнале

(Output

Enable).

При сигнале

выход

выход находится в отключенном состоянии, а

при

находится в отключенном состоянии, а

при производится выдача считываемой

информации.

производится выдача считываемой

информации.

63. Статические и динамические озу

Статические ОЗУ. Основой статического ОЗУ является накопитель или матрица памяти, состоящая из отдельных запоминающих (бистабильных) ячеек. Обычно в качестве этих ячеек используются различные типы триггеров. Двоичная информация, записанная в такую ячейку, может сохраняться в этой ячейке до тех пор, пока ее не заменят другой или не будет снято напряжение питания.

Статические ЗУ в 4–5 раз дороже динамических и приблизительно во столько же раз меньше по максимально достижимой информационной емкости. Их достоинством является высокое быстродействие, а типичной областью использования – схемы кэш-памяти, буферы FIFO, LIFO, память данных небольшой емкости для микроконтроллеров, быстродействующих коммуникационных устройств и т.п.

Динамические ОЗУ. В динамических ЗУ данные хранятся в виде зарядов емкостей МОП-структур и основой ЭП является просто конденсатор небольшой емкости. Заряженное состояние конденсатора считается состоянием логической единицы, разряженное – состоянием логического нуля. Такой ЭП значительно проще триггерного, содержащего 4 или 6 транзисторов, что позволяет разместить на кристалле намного больше ЭП (примерно в 4–5 раз) и обеспечивает динамическим ЗУ максимальную емкость. В то же время из-за токов утечки конденсатор со временем разряжается, и хранение данных требует их периодической регенерации (через каждые несколько миллисекунд).

Динамические ЗУ характеризуются наибольшей информационной емкостью, малым энергопотреблением и невысокой стоимостью, поэтому именно они используются как основная память ЭВМ.

Устройство типовой ячейки памяти динамического ОЗУ приведено на рис. 6.2.

Рис. 6.2. Элемент памяти динамического ОЗУ

Хранение

информации происходит в емкости

(затвор-исток) полевого транзистора, а

транзистор

(затвор-исток) полевого транзистора, а

транзистор выполняет роль ключа выборки. Режим

хранения обеспечивается периодической

регенерацией заряда емкости

выполняет роль ключа выборки. Режим

хранения обеспечивается периодической

регенерацией заряда емкости с частотой около сотки герц. В процессе

регенерации уменьшение заряда на емкости

компенсируется усилителем регенератором.

Динамические ОЗУ имеют малую потребляемую

мощность (50…500 мВт), так как для хранения

информации почти не потребляется

энергия, и все структуры работают в

импульсном (ключевом) режиме.

с частотой около сотки герц. В процессе

регенерации уменьшение заряда на емкости

компенсируется усилителем регенератором.

Динамические ОЗУ имеют малую потребляемую

мощность (50…500 мВт), так как для хранения

информации почти не потребляется

энергия, и все структуры работают в

импульсном (ключевом) режиме.

Особенностью

почти всех динамических ЗУ является

мультиплексирование шины адреса. Адрес

делится на два полуадреса, один из

которых представляет собою адрес строки,

а другой – адрес столбца матрица ЭП.

Оба полуадреса подаются на одни и те же

выводы корпуса микросхемы поочередно.

Подача адреса строки сопровождается

стробом

(Row

Address

Strobe),

а адреса столбца – стробом

(Row

Address

Strobe),

а адреса столбца – стробом

(Column

Address

Strobe).

При этом полуадреса заносятся в регистры

адреса строки и столбца соответственно.

Причиной мультиплексирования адресов

служит стремление уменьшить число

выводов корпуса микросхемы и тем самым

удешевить ее, а также то обстоятельство,

что полуадреса и сигналы

(Column

Address

Strobe).

При этом полуадреса заносятся в регистры

адреса строки и столбца соответственно.

Причиной мультиплексирования адресов

служит стремление уменьшить число

выводов корпуса микросхемы и тем самым

удешевить ее, а также то обстоятельство,

что полуадреса и сигналы

и

и в некоторых режимах и схемах используются

различно (например, в режимах построчной

регенерации адрес столбца вообще не

нужен). Сокращение числа внешних выводов

корпуса для динамических ЗУ особенно

актуально, т.е. они имеют максимальную

емкость и, следовательно, большую

разрядность адресов. Например, ЗУ с

организацией 16М×1 имеет 24-разрядный

адрес, а мультиплексирование сократит

число адресных линий на 12.

в некоторых режимах и схемах используются

различно (например, в режимах построчной

регенерации адрес столбца вообще не

нужен). Сокращение числа внешних выводов

корпуса для динамических ЗУ особенно

актуально, т.е. они имеют максимальную

емкость и, следовательно, большую

разрядность адресов. Например, ЗУ с

организацией 16М×1 имеет 24-разрядный

адрес, а мультиплексирование сократит

число адресных линий на 12.

На рис. 6.3. приведены примеры условных графических обозначений микросхем ОЗУ.

Рис. 9.3. Условные обозначения микросхем ОЗУ