- •“Избранные вопросы современной электроники”

- •Чтобы выдержать конкуренцию, срок разработки новых изделий необходимо сокращать.

- •СБИС программируемой логики:

- •Методика и средства проектирования цифровых устройств

- ••В результате разбиения в конечном счете получается структура. Переход от функции к структуре

- ••К этому описанию процесса проектирования следует добавить лишь, отражая возможности современной элементной базы,

- •Классификация цифровых ИС с точки зрения методов проектирования

- •Стандартные ИС

- •Специализированные ИС

- •Полупроводниковые средства для

- •Заказные схемы

- •Полузаказные схемы

- ••Стоимость проектирования БИС/СБИС велика и может достигать сотен миллионов долларов. Для дорогостоящих вариантов

- •Диаграмма областей целесообразного применения различных типов специализированных БИС/СБИС

- •Проектирование стандартных ИС массового производства, как и проектирование заказными методами вообще, - удел

- •Укрупненная

- •Классификация СБИС ПЛ

- •В соответствии с выбранным критерием СБИС ПЛ делят на СБИС, имеющие:

- •Архитектура простейшего

- •ПЗУ-универсальный логический преобразователь

- •Структура программируемой логической матрицы (ПЛМ-PLA)

- •Структура БИС программируемой матричной логики (ПМЛ –PAL)

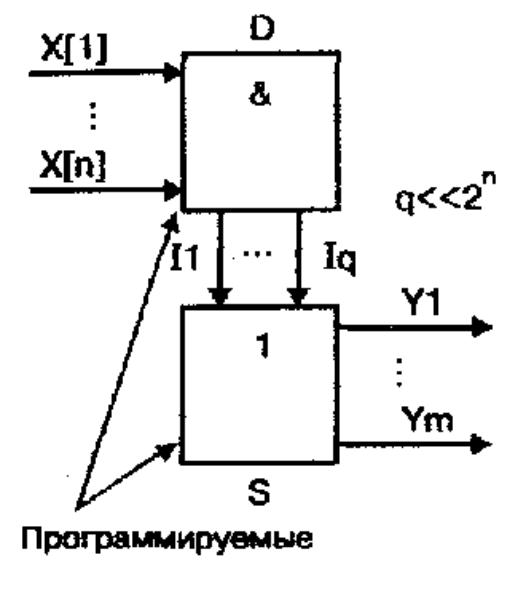

- •Структура простейшего функционального преобразователя СБИС ПЛУ (PLD)

- •Структура простейшего функционального преобразователя с архитектурой look-up-table

- •Архитектура простейшего функционального

- •Организация внутренней структуры и

- •Одноуровневые СБИС содержат простейшие функциональные преобразователи, организованные в виде матрицы или линейки, и

- •Наличие внутренней RAM памяти

- •Технология изготовления программируемых

- •Тип используемого программируемого элемента - электронного ключа, определяет возможности СБИС ПЛ по программированию,

- •Наиболее перспективны программируемые элементы, выполненные по

- •SRAM - технология обеспечивает меньшее энергопотребление и позволяет реконфигурировать СБИС ПЛ за десятки

- •Особое место занимает ряд семейств СБИС ПЛ, выпускаемых фирмой Actel и имеющих программируемые

- •СБИС программируемой логики фирмы ALTERA. Обзор семейств

- •Семейство Classic

- •Семейство МАХ (Multiple Array

- •Семейство МАХ (Multiple Array matrix)

- ••возможность задания режима пониженного энергопотребления (Turbo-off) как для всей СБИС в целом, так

- •Семейство FLEX (Flexible Logic

- ••работы в системах со смешанным напряжением питания (3.3 В, 5.0 В);

- •Семейство МАХ (Multiple Array matriX)

- ••задания режима пониженного энергопотребления (power-saving mode) как для всей СБИС в целом, так

- •Семейство FLEX (Flexible Logic Element matriX) 10K

- ••эмуляции внутренней шины с тремя состояниями;

- •Основными тенденциями развития выпускаемых фирмой Altera семейств СБИС ПЛ являются:

- •Структура обозначений СБИС ПЛ фирмы Altera

- •Семейство МАХ 7000. Общая характеристика

- •Обобщенная структура СБИС ПЛ семейства

- •Логические блоки организованы в виде матрицы, имеющей два столбца, разделенных программируемой матрицей соединений.

- •Глобальная шина управляющих сигналов

- •Программируемая матрица соединений

- •Логический блок

- •С каждого логического блока на блок ввода/вывода (и обратно) поступает от 6 до

- •Макроячейка

- •Блок ввода/вывода

- •Программирование

- •Программирование в составе системы (In System Programmability (ISP)) реализуется посредством стандартного четырехканального интерфейса

- •Для разработки цифровых устройств на СБИС PLD фирма Altera предоставляет пользователям функционально полный

- •кнопки быстрого вызова приложений

- •Описание приложений

- •Waveform

- •Timing

- •Терминология

- •имя проекта

- •Компилятор может автоматически обрабатывать следующие файлы проекта:

- ••схемные файлы OrCAD (.sch);

- •Примерами вспомогательных файлов являются:

- •Проект состоит из всех файлов иерархической структуры проекта, в том числе вспомогательных и

- •Приложение «Окно Иерархии

- •Средства создания проекта

- •Вставка символа (примитива или функции)

- •Средства системы

- •Графический редактор

- •имя проекта

- •Символьный редактор

- •Символьный редактор обладает следующими характеристиками: можно переопределить символ, представляющий файл проекта, создавать и

- •Текстовый редактор

- •Все перечисленные файлы проекта можно создавать в любом текстовом редакторе, однако данный редактор

- •Пользуясь данным текстовым редактором, можно создавать тестовые векторы (.vec), используемые для тестирования, отладки

- •Сигнальный редактор

- •Процесс симуляции проекта

- •Разработка описания проекта в сигнальном редакторе является альтернативой его созданию в графическом или

- •Поуровневый планировщик

- •В окне поуровневого планировщика могут быть представлены два типа изображения:

- •Приложение «Поуровневый Планировщик», просмотр и редактирование внешних выводов

- •Приложение «Поуровневый Планировщик», редактор внутренней структуры

- •Компиляция проекта

- •Компилятор применяет разнообразные способы увеличения эффективности проекта и минимизации использования ресурсов устройства.

- •Средства управления

- •Доступны следующие типы

- ••Pin assignment (Назначение контакта) назначает вход или выход одной логической функции конкретному контакту

- ••Connected pin assignment (Назначение соединенных контактов) задаёт внешнее соединение двух или более контактов

- ••Device assignment (Назначение устройства) назначает тип ПЛИС, на которой реализуется проект.

- ••Timing assignment (Назначение временных параметров) управляет логическим синтезом и подгонкой отдельных логических функций

- •Глобальные опции устройства для

- ••Global Project Logic Synthesis позволяет сделать глобальные установки для компилятора в части логического

- •Тестирование проекта

- •Для анализа регистровой логики на минимальное время задержки, минимальный период, и максимальную частоту

- •Программирование устройств

- •5.создание символьного файла 4-х битного счетчика pcount.sym;

- •10. создание

- •Аналоговые программируемые матрицы:

- •Разработан новый класс программируемых БИС, предназначенных для обработки аналоговых сигналов и обладающих уникальным

- •До сих пор наиболее сложной и трудоемкой для разработки остается аналоговая часть, которая

- •Разработчик может оперативно управлять откликом системы, изменяя, например, характеристики фильтра и его порядок;

- •Несмотря на существенные ограничения по точности и быстродействию, обусловленные технологией переключаемых конденсаторов, запрограммированные

- •Фирма Anadigm предоставляет в распоряжение разработчика полностью законченную систему, состоящую из

- •Программный пакет позволяет инженеру-разработчику легко и быстро конструировать сложные аналоговые схемы путем выбора,

- •Процесс создания схемы состоит из трех основных этапов:

- •Библиотека аналоговых моделей постоянно пополняется.

- •По окончании проектирования программный пакет AnadigmDesigner2 генерирует соответствующие кодовые файлы (Си-код), содержащие необходимую

Архитектура простейшего

функционального преобразователя

ПЗУ-универсальный логический преобразователь

Структура программируемой логической матрицы (ПЛМ-PLA)

Структура БИС программируемой матричной логики (ПМЛ –PAL)

Структура простейшего функционального преобразователя СБИС ПЛУ (PLD)

Структура простейшего функционального преобразователя с архитектурой look-up-table

Архитектура простейшего функционального

преобразователя Simple Logic Cell

Oснован на использовании комбинационных схем, обеспечивающих реализацию того или иного, минимального или неминимального базиса.

Организация внутренней структуры и

структуры матрицы соединений

Одноуровневые СБИС содержат простейшие функциональные преобразователи, организованные в виде матрицы или линейки, и единую для всей СБИС матрицу соединений функциональных преобразователей, разделенную узлами коммутации.

Одноуровневые СБИС ПЛ, имеющие сегментированную матрицу соединений, в англоязычной литературе обычно называют Field

Programmable Gate Arrays (FPGA).

В многоуровневых, в частности двухуровневых, СБИС ПЛ число функциональных преобразователей в логических блоках обычно невелико и расположены они компактно, поэтому локальные матрицы соединений являются непрерывными.