Исследование регистров (120

..pdfМосковский государственный технический университет имени Н.Э. Баумана

В.М. Буянкин, В.М. Гридин

ИССЛЕДОВАНИЕ РЕГИСТРОВ

Методические указания к выполнению лабораторной работы № 45

по курсу «Электротехника и электроника в управлении»

Москва Издательство МГТУ им. Н.Э. Баумана

2011

УДК 621.3 ББК 31.2

Б90

Рецензент А.В. Смирнов

Буянкин В.М.

Б90 Исследование регистров: метод. указания к выполнению лабораторной работы № 45 по курсу «Электротехника и электроникавуправлении» / В.М. Буянкин, В.М. Гридин. – М. : Изд-во МГТУ им. Н.Э. Баумана, 2011. – 18, [2] с. : ил.

Методические указания содержат основные теоретические сведения, необходимые для понимания работы регистров, и знакомят с основными способами кодирования информации цифровыми сигналами, а также с алгоритмами сложения и вычитания чисел.

Для студентов 3- и 4-го курсов факультета МТ, изучающих дисциплину «Электротехника и электроника в управлении».

Рекомендовано Учебно-методической комиссиейНУК ФН МГТУ им. Н.Э. Баумана.

УДК 621.3 ББК 31.2

МГТУ им. Н.Э. Баумана, 2011

Цель работы – изучение способов кодирования информации цифровыми сигналами, а также алгоритмов сложения и вычитания чисел с использованием многоразрядных сумматоров.

ОСНОВНЫЕ ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

При выполнении различных операций в цифровых системах числа обычно представляют в двоичной системе счисления. При

этом целое десятичное число А10 можно представить в виде n-разрядного двоичного числа А2:

n 1 |

|

А2 a j 2 j , |

(1) |

j 0

где a j 0 или 1 – цифра в j-м разряде двоичного числа.

Введением отрицательных степеней числа 2 представляют

дробные числа.

Цифровые системы оперируют действительными целыми и дробными числами, которые могут иметь две формы: с плавающей и фиксированной запятой.

При использовании плавающей запятой число складывается из двух частей: мантиссы m, содержащей значащие цифры, и порядка p, показывающего степень, в которую нужно возвести основание системы счисления q, чтобы полученное при этом число, умноженное на мантиссу, давало истинное значение представляемого числа:

А mq p . |

(2) |

q |

|

3

Вслучае фиксированной запятой число представляют в виде единого целого, причем положение запятой в разрядной сетке жестко фиксировано.

Цифровые системы с плавающей запятой сложнее, чем системы с фиксированной запятой, так как в первом случае требуется выполнение операций как над мантиссами, так и над порядками. Однако диапазон представляемых чисел при одинаковом числе разрядов в системах с плавающей запятой значительно шире.

Для представления знака числа используют дополнительный знаковый разряд z, обычно располагаемый перед числовыми. Для положительных чисел значение знакового разряда z = 0, для отрицательных z = 1. Для чисел с плавающей запятой вводят отдельные знаковые разряды для мантиссы и для порядка числа.

Вдальнейшем способы выполнения арифметических операций сложения и вычитания будем рассматривать только для целых двоичных чисел. Каждое целое двоичное число со знаком будем

представлять в n-разрядной сетке. Например, для n = 6 разрядная сетка показана на рис. 1, где старший разряд отведен под знак числа, а остальные разряды заняты значащими цифрами.

Арифметические операции над двоичными числами могут проводиться по тем же правилам, что и над десятичными. Однако чтобы упростить цифровые системы, для вы-

полнения сложения, вычитания, умножения и деления применяют алгоритмы, не используемые в обычной десятичной арифметике.

Рассмотрим правила выполнения операций с двоичными числами.

Для того чтобы выполнить сложение двух чисел, записанных в двоичной системе счисления, достаточно знать простейшую таблицу разрядного сложения:

4

Операцию вычитания в цифровых системах реализуют с помощью операции сложения, представляя вычитаемое в одном из специальных кодов. Разновидностью их является обратный код

числа А2 , который получают заменой всех нулей на единицу и

наоборот. Если представить вычитаемое, включая его знаковый разряд, в обратном коде, то можно получить разность путем арифметического сложения уменьшаемого (в обычном двоичном коде) и вычитаемого (в обратном коде) вместе со знаковыми разрядами. Если в знаковом разряде образуется перенос, то единицу прибавляют к разряду суммы. Такое прибавление единицы называют циклическим переносом. Знак результата определяется получившимся значением знакового разряда.

Для выполнения операций сложения и вычитания в цифровой системе удобно представлять отрицательные числа в обратном коде, а положительные – в обычном (прямом) коде. Вычитание заменяют сложением с переводом вычитаемого в обратный код, если это число положительное, и в обычный прямой код (т. е. перевод

В2 в обратный код), если число отрицательное. Если результат операции отрицательный (zS 1), то он представлен в обратном

коде, а если положительный (zS 0) – в обычном двоичном.

Рассмотрим примеры на сложение и вычитание чисел со знаком. Примеры:

1)

2)

5

При переводе чисел из обратного кода в прямой, можно пользоваться таблицей соответствия (табл. 1).

Таблица 1

Десятичное |

|

Прямой код |

Обратный код |

Дополнительный |

||||||

число |

|

|

код |

|

||||||

|

|

|

|

|

|

|

|

|

||

А10 |

а2 |

|

а1 |

а0 |

b2 |

b1 |

b0 |

c2 |

c1 |

c0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

2 |

0 |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

3 |

0 |

|

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

4 |

1 |

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

5 |

1 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

6 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

7 |

1 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

Недостатком обратного кода является образование циклического переноса, приводящего к повторению операции сложения, из-за которого существенно увеличивается время выполнения действия. Во многих случаях предпочтительней использовать дополнитель-

ный код числа А2 , образуемый из обратного прибавления единицы

к младшему разряду (табл. 1). При использовании дополнительного кода отпадает необходимость в циклическом переносе, и перенос, который может возникать в знаковом разряде числа, не учитывается. В дополнительном коде представляются все отрицательные числа. Вычитание заменяют сложением с переводом вычитаемого в дополнительный код, если число положительное, или переводом из дополнительного кода в обычный, если вычитаемое – отрицатель-

ное. Если знаковый разряд результата zS 1, то полученное число – отрицательное и представлено в дополнительном коде; если zS 0,

то результат положительный и представлен в обычном коде. Примеры:

1)

6

2)

Сложение и вычитание двоичных чисел с применением дополнительного кода выполнить проще и быстрее, хотя преобразование чисел в дополнительный код несколько сложнее, чем в обратный.

Основная операция при выполнении арифметических действий в современных цифровых системах – сложение, поэтому главным блоком операционных устройств обычно является сумматор, используемый также для вычитания, умножения, деления и ряда дру-

гих операций. |

|

|

|

|

Многоразрядные числа суммируют |

|

|||

их поразрядным сложением с переносом |

|

|||

между разрядами. Основным узлом мно- |

|

|||

горазрядных сумматоров является ком- |

|

|||

бинационный одноразрядный сумматор |

|

|||

(рис. 2), который выполняет ариф- |

|

|||

метическое |

сложение |

одноразрядных |

|

|

двоичных |

чисел Аi , Bi |

и перенос из |

|

|

|

Рис. 2. Одноразрядный |

|||

младшего разряда Pi 1, |

образуя на вы- |

|

сумматор |

|

ходах значение суммы |

Si и переноса в |

|

|

|

старший разряд Pi . |

|

|

|

|

На основе одноразрядных построены многоразрядные сумматоры. На рис. 3, а показана схема, поясняющая принцип действия четырехразрядного параллельного сумматора с последовательным переносом. Числа-слагаемые обозначены А1, А2, А3, А4 и В1, В2, В3, В4. Число одноразрядных сумматоров здесь равно числу разрядов. Выход переноса Р каждого сумматора соединен со входом последующего, суммирующего более старшие разряды. Сложение Аi и Вi происходит во всех разрядах одновременно, а перенос Р поступает с окончанием операции сложения в предыдущем разряде. Параллельный сумматор относится к классу комбинационных логических схем.

7

Для выполнения операции суммирования на входы сумматора подаются четырехразрядные числа со знаком (рис. 3, б). При этом отрицательные числа поступают в дополнительном коде. Само преобразование в дополнительный код выполняют до операции суммирования специальными схемами – кодопреобразователями. На выхо-

де параллельного сумматора формируется сумма и ее знак (zS ).

Рис. 3. Четырехразрядный сумматор

Четырехразрядный сумматор можно применять и в качестве вычитателя. При формировании разности чисел А и В, S = А – В, число А является уменьшаемым, а В – вычитаемым. Сумматор при выполнении вычитания должен сложить числа А и (–В). Таким образом, для выполнения операции необходимо вычитаемое подать

8

на вход сумматора в дополнительном коде. Для этого все разряды числа В (включая и знаковый zВ) пропускаются через инверторы

(рис. 4), а на вход переноса Р0 для формирования дополнительного кода В добавляется единица.

Рис. 4. Сумматор с элементами ИЛИ

Операции сложения и вычитания можно совместить в одном узле, если инверторы заменить элементами «исключающее ИЛИ». Эти элементы в зависимости от уровня напряжения на управляю-

щем входе работают как повторители (Uупр 0) или инверторы

(Uупр 0) (рис. 5).

Рис. 5. Сумматор с исключающим ИЛИ

9

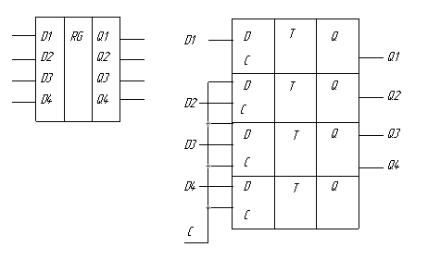

Для фиксации данных на входах и выходах сумматоров обычно используют регистры. Регистр – это устройство, предназначенное для приема, хранения и выдачи n-разрядного слова. Если код имеет n разрядов, то регистр должен иметь n запоминающих элементов для хранения этого кода. В качестве запоминающих элементов регистров обычно применяют D-триггеры (рис. 6). По импульсу С = 1 происходит запись информации в регистр.

Рис. 6. Регистр с D-триггерами

ЗАДАНИЯ И ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

Ознакомиться с лабораторной установкой. Выяснить назначение управляющих ключей и галетных переключателей.

Получить разрешение преподавателя на проведение работы.

ЛАБОРАТОРНАЯ УСТАНОВКА № 1

Лабораторная установка № 1 состоит из стандартной кассеты со схемой исследуемого устройства и универсального стенда ЛОЭ-2 (рис. 7). Кассета содержит сумматор SM, регистры RG1, RG2, кодопреобразователь на схемах «исключающее ИЛИ» и светодиоды на выходе сумматора.

10