Исследование триггеров (120

..pdfМосковский государственный технический университет имени Н. Э. Баумана

В. Н. Атаманов

ИССЛЕДОВАНИЕ ТРИГГЕРОВ

Методические указания к лабораторной работе № 43 по курсу «Электротехника и электроника»

Москва Издательство МГТУ им. Н. Э. Баумана

2011

УДК 621.3 ББК 31.2

А92

Рецензент А. А. Мальцев

Атаманов В. Н.

А92 Исследование триггеров : метод. указания к лабораторной работе № 43 по курсу «Электротехника и электроника» / В. Н. Атаманов. — М. : Изд-во МГТУ им. Н. Э. Баумана, 2011. — 19, [1] с. : ил.

Содержат теоретические сведения, необходимые для изучения основных схем асинхронных и синхронных триггеров в статическом режиме. Знакомят с функциональными возможностями триггеров, разными способами хранения информации в них. Рассматривают логику функционирования триггеров с раздельной установкой состояния 1 и 0 (RS-триггеры); счетным входом (T -триггеры); приемом информации по одному входу (D-триг- геры); универсальные триггеры с раздельной установкой состояния 0 и 1 (JK-триггеры).

Для студентов 3-го и 4-го курсов факультета МТ, изучающих дисциплину «Электротехника и электроника в управлении».

Рекомендовано Учебно-методической комиссией НУК ФН.

УДК 621.3 ББК 31.2

Учебное издание

Атаманов Валерий Николаевич

ИССЛЕДОВАНИЕ ТРИГГЕРОВ

Редактор В. М. Царев Корректор Л. С. Горбенко

Компьютерная верстка М. А. Голуба

Подписано в печать 11.01.2011. Усл. печ. л. 1,16. Формат 60×84/16. Тираж 800 экз. Изд. № 19. Заказ

Издательство МГТУ им. Н. Э. Баумана. Типография МГТУ им. Н. Э. Баумана. 105005, Москва, 2-я Бауманская ул., 5.

c МГТУ им. Н. Э. Баумана, 2011

Цель работы — ознакомление с основными схемами триггеров, изучение принципа действия асинхронных и синхронных триггеров в статическом режиме.

Теоретические сведения

Триггером называют импульсное устройство релейного типа с двумя устойчивыми состояниями. Он является одним из распространенных импульсных устройств в цифровой электронике. В частности, может использоваться для хранения двоичной информации (1 и 0), при построении цифровых автоматов с памятью

(счетчики, регистры и др.).

←−

Триггер имеет два выхода — прямой Q и инверсивный Q. О состоянии триггера судят по сигналу на прямом выходе. По способу записи информации различают триггеры асинхронные и синхронные (тактируемые). В асинхронных запись информации осуществляется одновременно с поступлением сигнала на информационные входы, в синхронных — при подаче синхроимпульса.

По логике функционирования триггеры могут быть с раздельной установкой состояния 1 и 0 (RS-триггеры); счетным входом (T -триггеры); приемом информации по одному входу (D-триггеры); универсальные с раздельной установкой состояния 0 и 1 (JK-триг- геры). Существуют и другие типы триггеров, которые в данной работе не рассматриваются.

По уравнению входного сигнала триггеры разделяют на триггеры с прямыми входами — запись информации дается уровнем 1 — и с инверсными входами — запись дется уровнем 0. Кроме того, синхронные триггеры бывают однотактными и двухтактными. В однотактных запись проводится по переднему фронту сигнала записи, а в двухтактных — по заднему, т. е. в момент окончания действия сигнала. Достоинством синхронных триггеров является повышенная помехозащищенность.

Применительно к схемам триггеров различают следующие наименования (функциональные назначения) входов:

S — для раздельного перевода триггера в состояние 1;

3

R — для раздельной установки триггера в состояние 0;

D — информационный для установки триггера в состояние 1 или 0;

J — для установки универсального JK-триггера в состояние 1; K — для установки универсального JK-триггера в состояние 0; C — исполнительный управляющий (командный) для приема

информации (вход синхронизации); T — счетный.

Закон функционирования триггера часто задают таблицей переходов (истинности), которая отражает процесс перехода триггера из одного устойчивого состояния в другое.

Рассмотрим законы функционирования наиболее распространенных устройств.

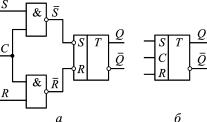

Асинхронный RS-триггер. На рис. 1 приведены схемы и условные обозначения RS-триггеров с прямыми (рис. 1, а) и инверсивными (рис. 1, б) входами. Они построены на двух логических элементах: ИЛИ—НЕ, и И—НЕ. Вход каждого элемента подключен к одному из выходов другого, что обеспечивает триггеру два устойчивых состояния.

Рис. 1. Схемы и условные обозначения асинхронных RS-триггеров:

а — с прямыми входами; б — с инверсивными входами

Рассмотрим таблицу переходов для RS-триггера с прямыми входами (табл. 1). В таблице QT и QT — уровни, которые были на выходах триггера до подачи на его входы так называемых сигналов активных уровней. Активным называют логический уровень сигнала, действующего на входе логического элемента и однозначно определяющего логический уровень выходного сигнала (независимо от уровней, действующих на остальных входах). Для элементов ИЛИ—НЕ за активный принимают высокий уровень, а для эле-

4

ментов И—НЕ — низкий. Уровни сигналов, подача которых на один из входов не приводит к изменению логического уровня на входе элемента, называют пассивными. Уровни QT+1 и QT+1 обозначают логические уровни на выходах триггера после подачи информации на его входы.

Таблица 1

|

|

|

|

|

T |

QT+1 |

|

|

T+1 |

S |

R |

QT |

|

Q |

|

Q |

|||

0 |

1 |

0 |

|

1 |

0 |

|

1 |

||

|

|

|

|

|

|

|

|

||

1 |

0 |

0 |

|

1 |

1 |

|

0 |

||

|

|

|

|

|

|

|

|

||

0 |

0 |

0 |

|

1 |

0 |

|

1 |

||

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

1 |

1 |

|

0 |

0 |

|

1 |

||

|

|

|

|

|

|

|

|

||

1 |

0 |

1 |

|

0 |

1 |

|

0 |

||

|

|

|

|

|

|

|

|

||

0 |

0 |

1 |

|

0 |

1 |

|

0 |

||

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Для триггера с прямыми входами QT+1 = 1 при S = 1 и R = 0; QT+1 = 0 при S = 0 и R = 1; QT+1 = QT при S = 0 и R = 0. При R = S = 1 состояние триггера будет неопределенным, так как во время действия информационных сигналов логические уровни на выходах триггера одинаковы (QT+1 = QT+1 = 0), а после окончания их действия триггер может равновероятно принять любое из устойчивых состояний, поэтому такая комбинация является запрещенной. В общем случае запрещенная комбинация входных сигналов — одновременная подача активных уровней на все информационные входы.

Режим S = 1, R = 0 называют режимом записи 1 (так как QT+1 = = 1); S = 0 и R = 1 — режимом записи 0, или режимом очистки. Режим S = 0, R = 0 называется режимом хранения информации, так как информация на выходе остается неизменной. Для триггера с инверсивными входами режим записи логической единицы реализуется при S = 0, R = 1; режим записи логического нуля — при S = 1, R = 0. При S = R = 1 обеспечивается хранение информации. Комбинация S = R = 0 является запрещенной.

5

Следует отметить, что самостоятельно RS-триггеры в устройствах цифровой техники используют ограниченно из-за низкой помехоустойчивости.

Синхронный RS-триггер. Схема и условное обозначение синхронного RS-триггера приведены на рис. 2. Переключения триггера возможны только при наличии синхроимпульса. Синхронный RS-триггер обладает повышенной помехозащищенностью, так как его переключения возможны только в течение времени действия синхроимпульса.

Рис. 2. Синхронный RS-триггер:

а — схема; б — условное обозначение

Синхронный, или тактируемый D-триггер. Имеет информационный вход D и вход C синхронизации. Одна из возможных структурных схем D-триггера и его условное обозначение показаны на рис. 3. Если уровень сигнала C = 0, то состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе D. При подаче на вход синхронизации уровня C = 1 информация на прямом выходе будет повторять подаваемую на вход D. Таким образом, при C = 0 QT+1 = QT, а при C = 1 QT+1 = D. Здесь QT — логический уровень на прямом выходе до подачи импульса синхронизации, а QT+1 — логический уровень на этом выходе после подачи импульса синхронизации.

На рис. 4 изображены временные диаграммы тактируемого D-триггера. В таком триггере происходит задержка сигнала на выходе по отношению к сигналу, подаваемому на вход, на время, не превышающее паузы между синхроимпульсами. Для устойчивой работы триггера необходимо, чтобы в течение синхроимпульса информация на входе D была неизменной.

6

Рис. 3. D-триггер:

а — схема; б — условное обозначение

Рис. 4. Временные диаграммы тактируемого D-триггера

Тактируемые D-триггеры, подобно другим синхронным триггерам, могут быть с потенциальным и динамическим управлением. У первых информация записывается в течение времени, при котором уровень сигнала C = 1. В триггерах с динамическим управлением информация записывается только при перепаде напряжения на входе синхронизации. Динамические входы изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы (рис. 5, а), то триггер срабатывает по фронту входного импульса, если от нее (рис. 5, б) — по срезу импульса.

Рис. 5. Условные изображения тактируемых D-триггеров:

а — с потенциальным управлением; б — с динамическим управлением

7

Счетный T -триггер (его также называют триггером со счетным входом). Триггер имеет один управляющий вход T и два выхода: Q и Q. Информация на любом выходе такого триггера меняет свой знак на противоположный при каждом положительном (или отрицательном) перепаде напряжения на входе. Счетный T -триггер может быть создан на базе тактируемого D-триггера или тактируемых RS-триггеров.

Условное обозначение счетного T -триггера, его структурная схема и временные диаграммы показаны на рис. 6. Как видно из диаграммы, переключение триггера происходит при положительном перепаде тактирующего импульса, частота сигнала на выходе T -триггера в два раза ниже частоты сигнала на входе, поэтому его можно использовать как делитель частоты с коэффициентом деления, равным двум. Счетный T -триггер, переключающийся при отрицательном перепаде напряжения на входе, может быть построен на основе двух последовательно соединенных RS-триггеров, первый из которых называют ведущим, а второй — ведомым. Условное обозначение, структурная схема и временные диаграммы такого триггера показаны на рис. 7. Представленную структуру называют также MS-триггером, или двухступенчатым триггером. При действии на входе фронта синхроимпульса информация записывается в ведущий триггер и при действии среза появляется на выходе ведомого триггера, т. е. на выходе двухступенчатого RS-триггера.

Универсальный JK-триггер. В сериях выпускаемых микросхем существуют также универсальные JK-триггеры. При соответствующем включении входов JK-триггер может выполнять функции триггера любого другого типа.

Рис. 6. Счетный T -триггер:

а — условное обозначение; б — схема; в — временная диаграмма

8

Рис. 7. M S-триггер:

а — условное обозначение; б — схема; в — временные диаграммы

Условное обозначение JK-триггера, схема его включения в качестве T -триггера и в качестве D-триггера представлены на рис. 8.

Рис. 8. Универсальный JK-триггер:

а — условное обозначение; б — схема включения в качестве T -триггера; в — схема включения в качестве D-триггера

Рис. 9. Графическое обозначение некоторых типов триггеров в сериях микросхем

Графическое обозначение некоторых типов триггеров в сериях микросхем приведены на рис. 9. Входы R и S в JK-тригге- рах и D-триггерах предназначены для предварительной установки и очистки.

9

Описание лабораторого стенда

Лабораторный стенд содержит источники питания, контрольные точки, измерительные приборы и разъем для присоединения исследуемого электронного устройства. Исследуемые устройства размещены в кассетах, на лицевых панелях которых изображены принципиальные электрические схемы. Набор триггерных схем, исследуемых в данной работе, представлен на двух кассетах «Триггеры 1» и «Триггеры 2». Электрическая схема «Триггеры 1» показана на рис. 10.

Рис. 10. Электрическая схема «Триггеры 1»

Нумерация переключаемых контактов на рис. 10 соответствует нумерации контактов переключателей, нанесенной на панели лабораторного стенда.

Переключатели VD1 (контакты 1, 2), VD2 (контакты 3, 4), VD3 (контакты 5, 6) служат для установки логического нуля или логической единицы на соответствующих входах A, B, C триггеров.

10