пособие Вычислительная техника

.pdf

управляемых уровнем. По такту С1 содержимое основного регистра переписывается в дополнительный, а по такту С2 возвращается в основной, но уже в соседние разряды, что соответствует сдвигу слова. По затратам оборудования и быстродействию этот вариант близок к однотактному регистру с двухступенчатыми триггерами.

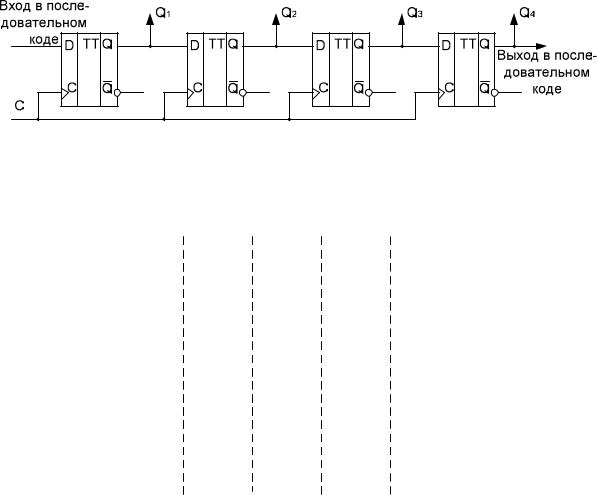

Рис. 7.2. Последовательный регистр хранения данных

C |

|

t1 |

|

|

t2 |

|

|

t3 |

|

|

t4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Q1 |

0 |

|

1 |

|

1 |

|

0 |

1 |

||||

|

|

|

|

|

|

|

|

|

||||

|

0 |

|

0 |

|

|

|

|

|

||||

Q2 |

|

|

1 |

|

1 |

0 |

||||||

|

|

|

|

|

|

|

|

|

||||

Q3 |

0 |

|

0 |

|

0 |

|

1 |

1 |

||||

|

|

|

|

|

|

|

|

|

||||

Q4 |

0 |

|

0 |

|

0 |

|

0 |

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 7.3. Временная диаграмма, иллюстрирующая процесс записи информации в последовательный регистр хранения данных

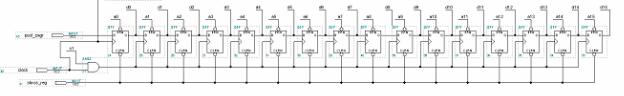

Комбинационные устройства позволяют в зависимости от задачи использовать различный тип записи: различают регистры с последовательным вводом и выводом, параллельным вводом и выводом, параллельным вводом и последовательным выводом, а также с последовательным вводом и параллельным выводом. На рисунке 7.4 представлен пример шестнадцатиразрядного сдвигающего регистра с параллельным выводом данных.

61

Рис. 7.4. Шестнадцатиразрядный сдвигающий регистр

спараллельным выводом данных

Всовременных микропроцессорных системах основное назначение регистров можно разбить на следующие группы:

1) аккумулирующие – используется для хранения промежуточных результатов арифметических и логических операций и инструкций ввода-вывода;

2) флаговые – хранят признаки результатов арифметических и логических операций;

3) общего назначения – хранят операнды арифметических и логических выражений, индексы и адреса;

4) индексные – хранят индексы исходных и целевых элементов массива;

5) указательные – хранят указатели на специальные области памяти (указатель текущей операции, указатель базы);

6) сегментные – хранят адреса и селекторы сегментов памяти; 7) управляющие – хранят информацию, управляющую состоя-

нием процессора, а также адреса системных таблиц.

7.2. Счётчики импульсов

Счётчики импульсов – комбинационное цифровое устройство, осуществляющее счёт поступающих на его вход импульсов. Результат счёта формируется счётчиком в заданном коде. Простейшим одноразрядным счётчиком импульсов является JK-триггер, T-триггер или D-триггер, работающий в счётном режиме. Количество импульсов, которое может подсчитать устройство, определяется выражением:

N 2n 1,

где n – число триггеров в счётчике.

Один триггер считает до одного, два последовательно соединённых триггера считают до трёх, n триггеров – до 2n 1 импульсов. Работа основана на счёте входных импульсов по модулю 2: каждый импульс переключает триггер в противоположное состояние. Результат счёта может храниться в памяти счётчика или быть считанным другим устройством цифровой техники.

62

По логике действия и функциональному назначению счётчики импульсов подразделяют на цифровые счётчики и счётчики-делители. Первые обычно называют просто счётчиками, а вторые – делителями. Счётчики также бывают суммирующие, когда счёт идёт на увеличение, и вычитающие – счёт на уменьшение. Если счётчик может переключаться в процессе работы с суммирования на вычитание и наоборот, то он называется реверсивным.

На рисунке 7.5 приведён пример счётчика импульса и графики, поясняющие работу устройства.

Рис. 7.5. Схема счётчика с последовательным переносом на Т-триггерах и графики, поясняющие принцип его работы

Изучая графики, нетрудно заметить, что каждый старший разряд счётчика отличается от младшего удвоенным числом импульсов счёта. Так, период импульсов на выходе первого триггера в 2 раза больше периода входных импульсов, на выходе второго триггера – в 4 раза, на выходе третьего триггера – в 8 раз. Для пояснения работы устройства примем в качестве исходного состояния нулевой уровень на всех выходах триггеров (Q0 – Q2), т.е. цифровой код 000. При этом старшим разрядом является выход Q2. Для перевода всех триггеров в режим работы входы R-триггеров объединены и на них подаётся необходимый уровень напряжения. На счётный вход поступают импульсы, которые увеличивают цифровой код на единицу, т.е. после

63

прихода первого импульса первый триггер переключается в состояние 1 (код 100), после прихода второго импульса второй триггер переключается в состояние 1, а первый – в состояние 0 (код 010), потом третий и т.д. В результате подобное устройство может досчитать до 7 (код 111), поскольку 23 – 1 = 7. Когда на всех выходах триггеров установились единицы, говорят, что счётчик переполнен. После прихода следующего импульса счётчик обнулится и начнётся всё с начала. На графиках изменение состояний триггеров происходит с некоторой задержкой t. На третьем разряде задержка уже утроенная. Увеличивающаяся с увеличением числа разрядов задержка является недостатком счётчиков с последовательным переносом, что, несмотря на простоту, ограничивает их применение в устройствах с небольшим числом разрядов.

На рисунке 7.6 приведён пример счётчика с параллельным переносом. Такие счётчики используются для повышения быстродействия, для этого применяют способ одновременного формирования сигнала переноса для всех разрядов. Достигается это введением элементов «И», через которые счётные импульсы поступают сразу на входы всех разрядов счётчика.

Рис. 7.6. Счётчик с параллельным переносом и графики, поясняющие его работу

64

На вход первого триггера, принцип работы которого аналогичен работе схемы, представленной на рисунке 7.5, поступают счётные импульсы. На вход второго триггера тактовый импульс пройдёт только тогда, когда на выходе первого триггера будет уровень логической единицы, а на вход третьего – когда на выходах первых двух будет единичный уровень, и т.д. Задержка срабатывания на третьем триггере такая же, как и на первом. Такой счётчик называется счётчиком с параллельным переносом. Как видно из схемы, с увеличением числа разрядов увеличивается число логических элементов «И», причём чем выше разряд, тем больше входов у элемента. Это является недостатком таких счётчиков.

Описанные выше счётчики однонаправленные и считают на увеличение, однако на практике часто необходимо менять направление счёта в процессе работы. Счётчики, которые в процессе работы могут менять направление счёта, называются реверсивными. Пример реверсивного счётчика приведён на рисунке 7.7.

Рис. 7.7. Реверсивный счётчик

Для счётных импульсов предусмотрены два входа: «Логическая единица/нуль» – верхний вход необходим для увеличения, нижний – для уменьшения. Логическая схема является двухпозиционным переключателем, управляемым прямым или инверсным выходом предыдущего триггера. При логической единице на прямом выходе счётчик отсчитывает импульсы с верхней шины «Логическая единица/нуль» (если они, конечно, поступают), при логической единице на инверсном выходе – с нижней шины «Логическая единица/нуль». Выходные элементы «И» формируют сигналы переноса. На выходе >7 сигнал формируется при коде 111 и наличии тактового импульса на верхней шине «Логическая единица/нуль», на выходе <0 сигнал формируется при коде 000 и наличии тактового импульса на нижней шине «Логическая единица/нуль».

65

Счётчики-делители считают входные импульсы до некоторого задаваемого коэффициентом счёта состояния, а затем формируют сигнал сброса триггеров в нулевое состояние. После сброса счёт входных импульсов до заданного коэффициента начинается заново.

Пример графического обозначения устройства счёта импульсов приведён на рисунке 7.8.

Рис. 7.8. Четырёхразрядный двоичный счётчик

Маркировка СТ2 означает, что счётчик является двоичным, если он десятичный, то ставится СТ10, если двоично-десятичный – СТ2/10. Входы D0 – D3 называются информационными входами и служат для записи в счётчик какого-либо двоичного состояния. Это состояние отобразится на его выходах, и от него будет производиться начало отсчёта. Другими словами, это входы предварительной установки. Вход V служит для разрешения записи кода по входам D0 – D3. Этот вход может обозначаться и другими буквами. Предварительная запись в счётчик производится при подаче сигнала разрешения записи в момент прихода импульса на тактовый вход С. Вход R служит для обнуления счётчика, т.е. при подаче импульса на этот вход на всех выходах счётчика устанавливаются логический нуль. Вход PI называется входом переноса. Выход P называется выходом переноса. На этом выходе формируется сигнал при переполнении счётчика (когда на всех выходах устанавливается логическая единица). Этот сигнал можно подать на вход переноса следующего счётчика. Тогда при переполнении первого счётчика второй будет переключаться в следующее состояние. Выходы 1, 2, 4, 8 являются выходами устройства. На них формируется двоичный код, соответствующий числу поступивших на вход счётчика импульсов.

Два объединённых R-входа и четыре раздельных выхода микросхемы позволяют без дополнительных логических элементов строить делители частоты с различными коэффициентами деления – от 2 до 10. Эта особенность схемы позволяет использовать её и как двоичный счётчик, и как счётчик-делитель.

66

7.3. Аналого-цифровые и цифроаналоговые преобразователи

Аналого-цифровой преобразователь (АЦП, англ. Analog-to-digi- tal converter, ADC) – устройство, преобразующее входной аналоговый сигнал в дискретный код (цифровой сигнал). Обратное преобразование осуществляется при помощи ЦАП (цифроаналогового преобразователя, DAC).

Некоторые неэлектронные устройства с цифровым выходом следует также относить к АЦП, например, некоторые типы преобразователей угол-код, простейшим одноразрядным двоичным АЦП является также компаратор.

Одним из самых важных параметров преобразователей является разрешение. Разрешение АЦП – минимальное изменение величины аналогового сигнала, которое может быть преобразовано в данные. Данный параметр АЦП связан с его разрядностью. В случае единичного измерения без учёта шумов разрешение напрямую определяется разрядностью АЦП.

Разрядность АЦП характеризует количество дискретных значений, которые преобразователь может выдать на выходе. В двоичных АЦП разрядность измеряется в битах, в троичных – в тритах. Например, двоичный восьмиразрядный АЦП способен выдать 256 дискретных значений (0…255), поскольку 28=256, троичный восьмиразрядный АЦП способен выдать 6561 дискретное значение, поскольку

38=6561.

Разрешение по напряжению равно разности напряжений, соответствующих максимальному и минимальному выходному коду, делённой на количество выходных дискретных значений.

На практике разрешение АЦП ограничено отношением «сигнал/шум» входного воздействия. При большой интенсивности шумов на входе АЦП различение соседних уровней входного сигнала становится невозможным, т.е. ухудшается разрешение. При этом реально достижимое разрешение описывается эффективной разрядностью

(effective number of bits – ENOB), которая меньше, чем реальная раз-

рядность АЦП. При преобразовании зашумлённого сигнала младшие разряды выходного кода практически бесполезны, так как содержат шум. Для достижения заявленной разрядности отношение «сигнал/шум» входного сигнала должно быть примерно 6 дБ на каждый бит разрядности.

67

При преобразовании сигналов возникают ошибки, основными из которых являются шумы квантования, нелинейность, апертурные погрешности, ошибки в выборе частоты дискретизации и др.

Ошибки квантования являются следствием ограниченного разрешения АЦП. Этот недостаток не может быть устранён ни при каком типе аналого-цифрового преобразования. Абсолютная величина ошибки квантования при каждом отсчёте находится в пределах от нуля до половины минимального разряда квантования.

Как правило, амплитуда входного сигнала намного больше, чем минимальный разряд квантования. В этом случае ошибка квантования не коррелирована с сигналом и имеет равномерное распределение. Её среднеквадратичное значение совпадает со среднеквадратичным от-

клонением распределения, которое равно 1 LSB 0.289LSB. В слу-

12

12

чае восьмибитного АЦП это составит 0,113 % от полного диапазона сигнала.

Ошибки, связанные с нелинейностью, которые являются следст-

вием физического несовершенства АЦП. Причиной возникновения служит передаточная характеристика, отличающаяся от линейной. Ошибки могут быть уменьшены путём автоматической калибровки и юстировки.

Важным параметром, описывающим нелинейность, является интегральная (INL) и дифференциальная (DNL) нелинейность.

Ошибки, связанные с апертурной погрешностью (джиттер).

Данная погрешность связана с невозможностью фиксации значений через равные промежутки времени. Пусть мы оцифровываем гармонический сигнал:

x(t) A sin(2 f0t).

В идеальном случае отсчёты берутся через равные промежутки времени. Однако в реальности эти моменты подвержены флуктуациям из-за дрожания фронта синхросигнала (clock jitter). Полагая, что неопределённость момента времени взятия отсчёта порядка t, получаем, что ошибка, обусловленная этим явлением, может быть оценена как Eдж x(t) t 2A f0 t. Из выражения видно, что ошибка относи-

тельно невелика на низких частотах, однако на больших частотах она может существенно возрасти.

Можно установить следующие требования к дрожанию фронта сигнала синхронизации:

t |

1 |

, |

|

||

2q f0 |

||

где q – разрядность АЦП.

68

В таблице приведены значения разрядности АЦП и максимальной рабочей частоты входного сигнала.

Связь максимальной частоты входного сигнала и разрядности АЦП

Разрядность АЦП |

|

Максимальная частота входного сигнала |

|

|||||||||

44,1 кГц |

192 кГц |

1 МГц |

10 МГц |

100 МГц |

||||||||

|

||||||||||||

8 |

28,2 |

нс |

6,48 |

нс |

1,24 |

нс |

124 |

пс |

12,4 пс |

|||

10 |

7,05 |

нс |

1,62 |

нс |

311 |

пс |

31,1 |

пс |

3,11 пс |

|||

12 |

1,76 |

нс |

405 |

пс |

77,7 |

пс |

7,77 |

пс |

777 |

фс |

||

14 |

441 |

пс |

101 |

пс |

19,4 |

пс |

1,94 |

пс |

194 |

фс |

||

16 |

110 |

пс |

25,3 |

пс |

4,86 |

пс |

486 |

фс |

48,6 |

фс |

||

18 |

27,5 |

пс |

6,32 |

пс |

1,21 |

пс |

121 |

фс |

12,1 |

фс |

||

24 |

430 фс |

98,8 фс |

19,0 фс |

1,9 |

фс |

190 ас |

||||||

Из таблицы видна связь частоты входного сигнала с разрядностью АЦП. Показано применение АЦП определённой разрядности с учётом ограничений, накладываемых дрожанием фронта синхронизации (clock jitter). Любой высокоскоростной АЦП крайне чувствителен к качеству оцифровывающей тактовой частоты. Любой шум, искажения или дрожание фазы тактовой частоты смешиваются с полезным сигналом и поступают на цифровой выход.

Аналоговый сигнал является непрерывной функцией времени, в АЦП он преобразуется в последовательность цифровых значений. Следовательно, необходимо определить частоту выборки цифровых значений из аналогового сигнала. Частота, с которой производятся цифровые значения, получила название частота дискретизации АЦП.

Непрерывно меняющийся сигнал с ограниченной спектральной полосой оцифровывается (т.е. значения сигнала измеряются через интервал времени T – период дискретизации), и исходный сигнал может быть точно восстановлен из дискретных во времени значений путём интерполяции. Точность восстановления ограничена ошибкой квантования. Однако в соответствии с теоремой Котельникова – Шеннона точное восстановление возможно, только если частота дискретизации выше, чем удвоенная максимальная частота в спектре сигнала.

Ошибки, связанные с наложением спектров (алиасинг). Если из-

вестно, что входной сигнал меняется достаточно медленно изменяющейся функцией относительно частоты дискретизации, то можно предположить, что промежуточные значения между выборками находятся где-то между значениями этих выборок. Если же входной

69

сигнал меняется быстро, то никаких предположений о промежуточных значениях входного сигнала сделать нельзя и невозможно однозначно восстановить форму исходного сигнала. В таком случае на выходе преобразователя будет присутствовать ложный сигнал. Ложные частотные компоненты сигнала (отсутствующие в спектре исходного сигнала) получили название alias (ложная частота, побочная низкочастотная составляющая). Частота ложных компонентов зависит от разницы между частотой сигнала и частотой дискретизации. Например, гармонический сигнал с частотой 2 кГц, дискретизованный с частотой 1,5 кГц, был бы воспроизведён как гармоника с частотой 500 Гц. Эта проблема получила название наложение частот (aliasing).

Для предотвращения наложения спектров сигнал, подаваемый на вход АЦП, должен быть пропущен через фильтр нижних частот для подавления спектральных компонентов, частота которых превышает половину частоты дискретизации. Этот фильтр получил название антиалиасинговый (anti-aliasing) фильтр, его применение чрезвычайно важно при построении реальных АЦП. Наложение спектров может быть полезным, например, при преобразовании частоты вниз при оцифровке узкополосного высокочастотного сигнала. Для этого, однако, входные аналоговые каскады АЦП должны иметь значительно более высокие параметры, чем это требуется для стандартного использования АЦП на основной гармонике. Также для этого необходимо обеспечить эффективную фильтрацию внеполосных частот до АЦП, так как после оцифровки нет никакой возможности идентифицировать и(или) отфильтровать большинство из них.

Добавление псевдослучайных сигналов (dither). Улучшение ха-

рактеристик АЦП за счёт подмешивания псевдослучайного сигнала заключается в добавлении ко входному аналоговому сигналу случайного шума (белого шума) небольшой амплитуды. Амплитуда шума, как правило, выбирается на уровне половины минимального разряда квантования. Эффект от такого добавления заключается в том, что состояние минимального разряда случайным образом переходит между состояниями 0 и 1 при очень малом входном сигнале. Для сигнала с подмешанным шумом вместо простого округления сигнала до ближайшего разряда происходит случайное округление вверх или вниз, причём среднее время, в течение которого сигнал округлён к тому или иному уровню, зависит от того, насколько сигнал близок к этому уровню. Таким образом, оцифрованный сигнал содержит информацию об амплитуде сигнала с разрешающей способностью лучше, чем

70