пособие Вычислительная техника

.pdf

На этих временных диаграммах обозначение Q΄ соответствует сигналу на выходе первого триггера. Так как на вход синхронизации второго триггера тактовый сигнал поступает через инвертор, то когда первый триггер находится в режиме хранения, второй триггер пропускает сигнал на выход схемы. И наоборот, когда первый триггер пропускает сигнал с входа схемы на свой выход, второй триггер находится в режиме хранения.

Обратите внимание на то, что сигнал на выходе всей схемы в целом не зависит от сигнала на входе Q-схемы. Если первый триггер пропускает сигнал данных со своего входа на выход, то второй триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, т.е. сигнал на выходе схемы тоже не может измениться.

JK-триггер. Таблица истинности JK-триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, схема триггера изменена таким образом, что при подаче двух единиц JK-триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C-импульсов JK-триггер изменяет своё состояние на противоположное.

С |

K |

J |

Q(t) |

Q(t 1) |

Пояснения |

|

0 |

× |

× |

0 |

0 |

|

|

0 |

× |

× |

1 |

1 |

Режим хранения |

|

1 |

0 |

0 |

0 |

0 |

||

|

||||||

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

Режим установки единицы |

|

1 |

0 |

1 |

1 |

1 |

J=1 |

|

1 |

1 |

0 |

0 |

0 |

Режим записи нуля K=1 |

|

1 |

1 |

0 |

1 |

0 |

||

|

||||||

1 |

1 |

1 |

0 |

1 |

K=J=1 счётный режим |

|

1 |

1 |

1 |

1 |

0 |

||

|

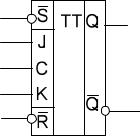

Один из вариантов схемы JK-триггера приведён на рисунке 5.12.

Рис 5.12. Схема JK-триггера

41

Для реализации счётного режима в схеме, приведённой на рисунке 5.12, введена перекрёстная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря этой обратной связи на входах R и S никогда не может возникнуть запрещённая комбинация.

Приводить временные диаграммы работы JK-триггера не имеет смысла, они совпадают с приведёнными ранее диаграммами RS- и T-триггера. Условно-графическое обозначение JK-триггера приведено на рисунке 5.13.

Рис. 5.13. Условно-графическое обозначение JK-триггера

Синхронизирующие входы триггера могут быть статическими и динамическими. Статический вход не теряет своего управляющего действия, пока на нём присутствует тактовый импульс. В присутствии тактового импульса эти триггеры будут менять своё состояние при каждой смене комбинаций логических потенциалов на входах S и R. Динамический синхровход воздействует на состояние выходов триггера в момент своего появления (передним фронтом) или окончания (задним фронтом).

Тактируемый (синхронный) триггер обычно имеет дополнительные асинхронные входы, по которым он вне зависимости от сигнала на тактовом входе переключается в состояние 1 (по входу S) или 0 (по входу R). Такие входы называют нетактируемыми, или асинхронными.

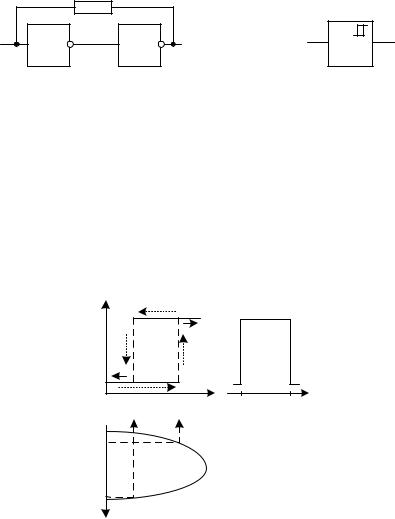

Триггер Шмитта. Этот триггер особенный в семействе триггеров: он имеет один вход, один выход и не обладает свойствами запоминающего элемента. Триггер содержит два инвертора, охваченных положительной обратной связью, за счёт чего выход схемы может изменять своё состояние лавинообразно. Схема триггера Шмитта представлена на рисунке 5.14.

42

Рис. 5.14. Схема триггера Шмитта и условное графическое обозначение

На выходе инвертора потенциал с логическим нулём изменяется на логическую единицу при большем входном напряжении, чем при изменении с логической единицы на логический нуль. Поэтому схема (рис. 5.14) обладает гистерезисом (рис. 5.15). Это позволяет использовать её в качестве формирователя прямоугольных импульсов из входного напряжения, в частности из гармонического.

U2 |

|

|

|

|

|

|

t |

Uп2 |

Uп1 |

t1 |

t2 |

t1 |

|

|

|

t2 t

Рис. 5.15. Амплитудо-временные характеристики с петлёй гистерезиса

Фазовая траектория (статическая характеристика) триггера Шмитта представляет собой прямоугольную петлю гистерезиса. Она и позволяет использовать триггер в качестве формирователя прямоугольных импульсов из входного напряжения, в частности из синусоидального. Неоднозначность статической характеристики позволяет утверждать, что триггер Шмитта, как и другие триггеры, обладает свойством памяти: его состояние в зоне неоднозначности определяется предысторией – ранее действовавшим входным сигналом.

5.3. Явление метастабильности

Сигнал на входе триггера может принимать только два состояния: логический нуль и логическая единица. Однако синхроимпульс может прийти в любой момент времени, в том числе и в момент смены состояния сигнала на входе триггера.

43

Если синхросигнал попадёт точно на момент перехода входным сигналом порогового уровня, то триггер на некоторое время может попасть в неустойчивое метастабильное состояние, при котором напряжение на его выходе будет находиться между уровнем логического нуля и логической единицы. Это может привести к нарушению правильной работы цифрового устройства.

Состояние метастабильности триггера подобно неустойчивому состоянию шарика, находящегося на вершине конического холма. Такая ситуация иллюстрируется рисунком 5.16. Обычно триггер не может долго находиться в состоянии метастабильности и быстро возвращается в одно из стабильных состояний. Время нахождения в метастабильном состоянии зависит от уровня шумов схемы и использованной технологии изготовления микросхем.

а) |

б) |

Рис. 5.16. Иллюстрация явления метастабильности:

а – в случае воздействия импульсного шума; б – переход в стабильное состояние

Метастабильное состояние не всегда приводит к неправильной работе цифрового устройства. Если время ожидания устройства после прихода импульса синхронизации достаточно велико, то триггер может успеть перейти в устойчивое состояние, и мы даже ничего не заметим. То есть если мы будем учитывать время метастабильности tmet, то метастабильность никак не скажется на работе остальной цифровой схемы.

Если же это время будет неприемлемым для работы схемы, то можно поставить два триггера последовательно, использовать триггер Шмитта или промежуточный буфер. Это снизит вероятность возникновения метастабильного состояния.

44

Вопросы для самопроверки

1.Постройте RS- и JK-триггеры.

2.На примере покажите наличие запрещённого состояния в RSтриггере.

3.Покажите на примере, как происходит деление частоты T-триггером.

Вопросы для самоконтроля

1.Что такое запрещённое состояние в RS-триггере?

2.Принцип работы D- и Т-триггера, где используются эти цифровые устройства.

3.Принцип работы JK-триггера. Почему в данном устройстве отсутствует запрещённое состояние?

4.Объясните появление петли гистерезиса в амплитудо-времен- ных характеристиках в триггере Шмитта.

5.Объясните принцип метастабильности.

45

6. ИЗУЧЕНИЕ КОМБИНАЦИОННЫХ ЦИФРОВЫХ УСТРОЙСТВ

Цель главы: изучение комбинационных цифровых устройств – шифраторов, дешифраторов, мультиплексоров, демультиплексоров и преобразователей кодов. Составление таблиц истинности и их построение на основе простых логических функций.

6.1. Шифраторы и дешифраторы

Шифратор (кодер) (англ. encoder) – логическое устройство, выполняющее преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код.

Двоичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного кода в двоичный. При подаче сигнала на один из n-входов на выходе появляется двоичный код номера активного входа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все – то неполным. Число входов и выходов в полном шифраторе связано соотношением:

n = 2m ,

где n – число входов шифратора;

m – число выходных двоичных разрядов.

Достаточно часто перед разработчиками цифровой аппаратуры встаёт задача преобразования кода. Требуется изменить восьмеричный, шестнадцатеричный или десятичный линейный код на двоичный. Приведём пример преобразования восьмеричного кода в двоичный.

Составим таблицу истинности такого устройства:

|

|

|

Входы |

|

|

|

|

Выходы |

|

|||

x0 |

x1 |

x2 |

x3 |

x4 |

x5 |

x6 |

x7 |

y0 |

|

y1 |

|

y2 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

1 |

|

1 |

46

Запишем для каждого выхода y0 - y2 сочетания, при которых появляются единицы:

y0 x1 x3 x5 x7 ; y1 x2 x3 x6 x7 ; y2 x4 x5 x6 x7 .

Результирующая схема восьмерично-двоичного кодера приведена на рисунке 6.1.

Рис. 6.1. Структурная схема восьмеричного шифратора

В случае если ячейки или таблицы не несут полезной информации, и не важно, будет ли записан нуль или будет записана единица, такие элементы таблицы можно пометить символом 'X'.

|

|

|

Входы |

|

|

|

|

Выходы |

|

||

x0 |

x1 |

x2 |

x3 |

x4 |

x5 |

x6 |

x7 |

y0 |

y1 |

|

y2 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

X |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

X |

X |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

X |

X |

X |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

X |

X |

X |

X |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

X |

X |

X |

X |

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

X |

X |

X |

X |

X |

X |

1 |

0 |

0 |

1 |

|

1 |

X |

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

|

1 |

47

Наличие в строках неопределённых значений в ряде случаев позволяет значительно упростить схему восьмеричного кодера. Пример условно-графическое обозначения восьмеричного шифратора представлен на рисунке 6.2.

Рис. 6.2. Условно-графическое обозначение восьмеричного шифратора

Дешифраторы (декодер) – это комбинационное цифровое устройство, преобразующее код, подаваемый на входы, в сигнал на одном из выходов. На выходе дешифратора появляется логическая единица, на остальных – логические нули, когда на входных шинах устанавливается двоичный код определённого числа или символа. Число входов дешифратора равно количеству разрядов поступающих двоичных, троичных или k-ичных чисел. Число выходов равно полному количеству различных двоичных, троичных или k-ичных чисел этой разрядности.

Из логических элементов, являющихся дешифраторами, можно строить дешифраторы на большое число входов. Каскадное подключение таких схем позволит наращивать число дифференцируемых переменных.

Рассмотрим пример построения декодера из двоичного кода в восьмеричный. Восьмеричный код обычно отображается одним битом на одну цифру. Таблица истинности такого декодера приведена ниже.

|

Входы |

|

|

|

|

Выходы |

|

|

|

|

x0 |

x1 |

x2 |

y0 |

y1 |

y2 |

y3 |

y4 |

y5 |

y6 |

y7 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

48

Запишем для каждого выхода y0 - y2 сочетания, при которых по-

являются единицы:

y0 0; y1 x2; y2 x1; y3 x1 x2 ; y4 x0; y5 x0 x2 ; y6 x0 x1;

y7 x0 x1 x2 .

Результирующая схема двоично-восьмеричного декодера приведена на рисунке 6.3.

Рис. 6.3. Структурная схема дешифратора

Как видно на этой схеме, для реализации каждой строки таблицы истинности потребовались блоки «2И» и «3И». Логические элементы «ИЛИ» не потребовались, так как в таблице истинности на каждом выходе присутствует только одна единица.

49

Дешифраторы выпускаются в виде отдельных микросхем или используются в составе других микросхем. В настоящее время десятичные или восьмеричные дешифраторы используются в основном как составная часть других микросхем, таких как мультиплексоры, демультиплексоры, ПЗУ или ОЗУ.

Условно-графическое обозначение микросхемы дешифратора на принципиальных схемах приведено на рисунке 6.4. На этом рисунке приведено обозначение двоично-восьмеричного дешифратора, полная внутренняя принципиальная схема которого изображена на рисун-

ке 6.3.

Рис. 6.4. Условно-графическое обозначение двоично-десятичного дешифратора

Точно таким же образом можно получить принципиальную схему и для любого другого декодера (дешифратора). Наиболее распространены схемы восьмеричных и шестнадцатеричных дешифраторов. Для индикации такие дешифраторы в настоящее время практически не используются. В основном данные цифровые устройства используются как составная часть более сложных модулей.

6.2. Мультиплексоры и демультиплексоры

Мультиплексоры

Мультиплексор является устройством, которое осуществляет коммутацию одного из нескольких информационных входных сигналов с входов (X0, X1,..., Xk ) на выход Y в соответствии с заданным ко-

дом на входах управления. В простейшем случае такую коммутацию можно осуществить при помощи ключей (рис. 6.5).

50