пособие Вычислительная техника

.pdf

Таблица 4.1

Пример минимизации полученных выражений

Простые |

|

|

|

Конституенты единицы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

импли- |

X1X2 X3X4 |

X1X2 X3 |

|

4 |

X1X2 |

|

3X4 |

X1 |

|

2 |

|

3X4 |

|

|

1 |

|

2 |

|

3X4 |

|

|

1 |

|

2 |

|

3 |

|

4 |

||||||||

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

|||||||||||||||||||||||||||

|

канты |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

X1X2 X3 |

× |

× |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

X1X2 X4 |

× |

|

× |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

X1 |

|

|

3 X4 |

|

|

× |

|

× |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

2 |

|

|

3 X4 |

|

|

|

|

|

|

|

× |

|

× |

|

|

|

|

|

|

|

|

|

|

||||||||||||

X |

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

1 |

|

|

2 |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

× |

|

× |

|

|

|

|||||||||||

X |

X |

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

Как уже отмечалось, простая импликанта поглощает некоторую конституенту единицы, если является её собственной частью. Соответствующая клетка импликантной матрицы на пересечении строки (с рассматриваемой простой импликантой) и столбца (с конституентой единицы) отмечается крестиком (табл. 4.1). Минимальные ДНФ строятся по импликантной матрице следующим образом:

1.Ищутся столбцы импликантной матрицы, имеющие только один крестик. Соответствующие этим крестикам простые импликанты называются базисными и составляют так называемое ядро булевой функции. Ядро обязательно входит в минимальную ДНФ.

2.Рассматриваются различные варианты выбора совокупности простых импликант, которые накроют крестиками остальные столбцы импликантной матрицы, и выбираются варианты с минимальным суммарным числом букв в такой совокупности импликант.

Таким образом, минимальная ДНФ будет иметь вид:

F(X1,X2,X3,X4 ) X1X2 X3 X1X3X4 X1X2 X3.

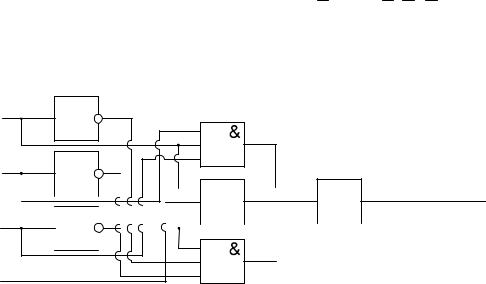

Используя полученные при минимизации выражения, построим устройство, реализующее приведённую таблицу истинности (рис.).

X1

X2

F(X1,X2,X3, X4) X3

F(X1,X2,X3, X4) X3

X4

Комбинационно-цифровое устройство

31

В заключение отметим, что совершенные нормальные формы не являются самым простым способом задания переключательных функций. Как правило, они допускают преобразование с помощью правил булевой алгебры к более простому виду. Способам построения простейших представлений переключательных функций посвящён один из следующих разделов курса.

Вопросы для самопроверки

1. Используя таблицу истинности (табл. 4.2), минимизировать полученное выражение при помощи СДНФ.

|

|

|

|

|

|

|

Таблица 4.2 |

|

|

|

Таблица заданий для самостоятельной работы |

||||||

X1 |

X2 |

X3 |

F1(X1,X2 , X3 ) |

F2 (X1,X2 ,X3 ) |

F3 (X1, X2, X3) |

F4(X1,X2,X3) |

F5 (X1, X2 ,X3 ) |

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

2.В пакете программ САПР построить полученную схему устройства.

3.На примере показать принцип его работы.

Вопросы для самоконтроля

1.Что такое совершенная дизъюнктивная нормальная форма?

2.Что такое совершенная конъюнктивная нормальная форма?

3.Приведите пример операции склеивания и поглощения.

4.Этапы преобразования функции методом Куайна?

5.Как выбираются простые импликанты?

32

5. ИЗУЧЕНИЕ КОМБИНАЦИОННЫХ ЦИФРОВЫХ УСТРОЙСТВ. ТРИГГЕРЫ

Цель главы: изучение комбинационных цифровых устройств – триггеров. Составление таблиц истинности и их построение на основе простых логических функций.

Триггер (триггерная система) – один из базовых (основных) элементов цифровой техники. Под триггером будем понимать устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде. При двух последовательных переключениях триггера на выходе формируется один импульс, т.е. триггер можно использовать как делитель частоты переключающих сигналов с коэффициентом, равным двум.

При изготовлении триггеров применяются преимущественно полупроводниковые приборы (обычно биполярные и полевые транзисторы), в прошлом – электромагнитные реле, электронные лампы. В настоящее время логические схемы, в том числе с использованием триггеров, создают в интегрированных средах разработки под различные программируемые логические интегральные схемы (ПЛИС). Используются в основном в вычислительной технике для организации компонентов вычислительных систем: регистров, счётчиков, процессоров, памяти.

33

Триггеры можно разделить на две группы: нетактируемые и тактируемые. Нетактируемый (асинхронный) триггер может менять своё состояние переключающими сигналами в любое время. Тактируемый (синхронный) триггер переключается синхронно с поступлением специального тактирующего импульса. Структурная схема представлена на рисунке 5.1.

|

Триггеры |

Тактируемые |

Нетактируемые |

RSC - триггер |

RC - триггер |

D - триггер |

Асинхронный Т - триггер |

Синхронный Т - триггер |

|

JK - триггер |

|

Рис. 5.1. Классификация триггеров

По способу представления выходной информации триггеры подразделяются на две большие группы – динамические и статические.

Динамический триггер представляет собой систему, одно из состояний которой (единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определённой частоты, а другое – отсутствием выходных импульсов (нулевое). Смена состояний производится внешними (тактовыми) импульсами.

К статическим триггерам относят устройства, каждое состояние которых характеризуется неизменными уровнями выходного напряжения (выходными потенциалами): высоким – близким к напряжению питания – и низким – около нуля. Статические триггеры по способу представления выходной информации часто называют потенциальными.

34

5.1. Нетактируемые триггеры

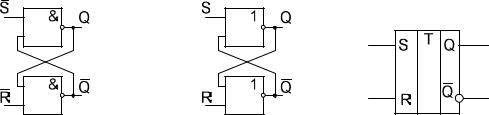

RS-триггер, или SR-триггер – триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. Структурная схема представлена на рисунке 5.2.

а) |

б) |

в) |

Рис. 5.2. Структурные схемы RS-триггеров:

а– асинхронный RS-триггер на элементах «2И–НЕ;

б– асинхронный RS-триггер на логических элементах «2ИЛИ-НЕ»;

в– условное графическое обозначение асинхронного RS-триггера

При подаче единицы на вход S (от англ. Set – установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от англ. Reset – сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, в некоторых случаях является запрещённым, при такой комбинации RS-триггер переходит в третье состояние QQ=00. Одновременное снятие двух «1» практически невозможно. При снятии одной из «1» RS-триггер переходит в состояние, определяемое оставшейся «1». Таким образом, RS-триггер имеет три состояния, из которых два устойчивых (при снятии сигналов управления RS-триггер остаётся в установленном состоянии) и одно неустойчивое (при снятии сигналов управления RS-триггер не остаётся в установленном состоянии, а переходит в одно из двух устойчивых состояний). Таблица истинности RS-триггера приведена ниже.

|

|

Q(t) |

|

|

|

Q(t 1) |

|

|

|

S |

R |

|

Q(t) |

Q(t 1) |

|||||

0 |

0 |

0 |

|

1 |

0 |

1 |

|||

0 |

0 |

1 |

|

0 |

1 |

0 |

|||

0 |

1 |

0 |

|

1 |

0 |

1 |

|||

0 |

1 |

1 |

|

0 |

0 |

1 |

|||

1 |

0 |

0 |

|

1 |

1 |

0 |

|||

1 |

0 |

1 |

|

0 |

1 |

0 |

|||

1 |

1 |

0 |

|

1 |

0 |

0 |

|||

1 |

1 |

1 |

|

0 |

0 |

0 |

|||

35

Т-триггер – это счётный триггер. Т-триггер имеет один вход (вспомогательные входы принудительной установки «0» и «1» не рассматриваются), куда подают счётные импульсы. После подачи каждого импульса состояние Т-триггера меняется на обратное (инверсное) предыдущему состоянию. Условное графическое обозначение Т-триг- гера представлено на рисунке 5.3.

или

Рис. 5.3. Условное графическое обозначение Т-триггера

Т-триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному D-триггеру. То, что триггер работает по фронту, отображается на условно-графическом обозначении треугольником, изображённым на выводе входа синхронизации. То, что внутри этого триггера находится два триггера, отображается в среднем поле условно-графического изображения двойной буквой T.

Использование двух триггеров позволяет избежать самовозбуждения схемы, так как счётные триггеры строятся при помощи схем с обратной связью. Иногда при изображении динамического входа указывают, по какому фронту триггер (или триггеры) изменяет своё состояние. В этом случае используется обозначение входа, как это показано на рисунке 5.4.

а) б)

Рис. 5.4. Обозначение динамических входов

На рисунке 5.4а обозначен динамический вход, работающий по переднему (нарастающему) фронту сигнала. На рисунке 5.4б обозначен динамический вход, работающий по заднему (спадающему) фронту сигнала.

36

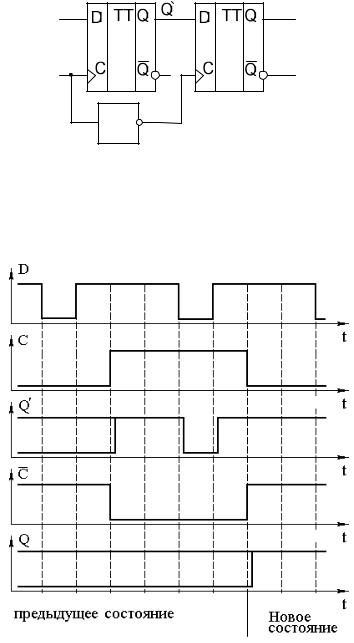

Рассмотрим пример синтеза Т-триггера из динамического D-триггера. Для того чтобы превратить D-триггер в счётный, необходимо ввести цепь обратной связи с инверсного выхода этого триггера на вход, как показано на рисунке 5.5.

Рис. 5.5. Схема T-триггера, построенная на основе D-триггера

Временная диаграмма T-триггера приведена на рисунке 5.6. При построении этой временной диаграммы был использован триггер, работающий по заднему фронту синхронизирующего сигнала.

Рис. 5.6. Временные диаграммы T-триггера

Т-триггеры используются при построении схем различных счётчиков, поэтому в составе БИС различного назначения обычно есть готовые модули этих триггеров. Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т-вход подают единицу, а на С – сигнал с частотой, которая будет поделена на 2.

5.2. Тактируемые триггеры

На входы логического элемента или устройства сигналы не всегда поступают одновременно, так как перед этим они могут проходить через разное число элементов, не обладающих к тому же одинаковой задержкой. Это явление описывают как состязания или гонки

37

сигналов. В результате в течение некоторого времени на входах создаётся непредвиденная ситуация: новые значения одних сигналов сочетаются с предыдущими значениями других, что может привести к ложному срабатыванию элемента (устройства). Последствия гонок можно устранить временным стробированием, когда на элемент, кроме информационных сигналов, подаются тактирующие (синхронизирующие) импульсы, к моменту прихода которых информационные сигналы заведомо успевают установиться на входах.

Тактируемый триггер, кроме информационных входов, имеет синхронизирующий (тактирующий, тактовый) вход; сигналы на информационных входах воздействуют на такой триггер только с поступлением сигнала на синхронизирующий вход.

D-триггер. В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение как нуля, так и единицы. Для его передачи достаточно одного провода. Сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке 5.7.

Рис. 5.7. Схема D-триггера

Такой триггер получил название D-триггера. Название происходит от английского слова delay – задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Условно-графическое обозначение D-триггера на принципиальных схемах приведено на рисунке 5.8.

Рис. 5.8. Условно-графическое обозначение D-триггера (защёлки)

38

Таблица истинности для D-триггера приведена ниже. Как видно из этой таблицы, этот триггер способен запоминать по синхросигналу и хранить один бит информации.

С |

D |

Q(t) |

Q(t 1) |

Пояснения |

|

|

|

|

|

|

|

0 |

× |

0 |

0 |

Режим хранения |

|

|

|

|

|

||

0 |

× |

1 |

1 |

||

|

|||||

|

|

|

|

|

|

1 |

0 |

× |

0 |

Режим записи |

|

|

|

|

|

||

1 |

1 |

× |

1 |

||

|

|||||

|

|

|

|

|

D-триггеры называются триггерами, работающими по уровню. Ещё одно название таких триггеров, пришедшее из иностранной литературы, – триггеры-защёлки. Легче всего объяснить появление этого названия по временной диаграмме, приведённой на рисунке 5.9.

Рис. 5.9. Временная диаграмма D-триггера

По этой временной диаграмме видно, что триггер-защёлка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера.

Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий. Входные данные как бы «защёлкиваются» в этот момент, отсюда и название – триггер-защёлка.

Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение, были разработаны триггеры, работающие по фронту.

39

Фронт сигнала синхронизации, в отличие от высокого (или низкого) уровня, не может длиться продолжительное время. В идеале длительность фронта равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту, не нужно предъявлять требования к длительности тактового сигнала.

Триггер, запоминающий входную информацию по фронту, может быть построен из двух триггеров, работающих по потенциалу. Сигнал синхронизации будем подавать на эти триггеры в противофазе. Схема такого триггера приведена на рисунке 5.10.

Рис. 5.10. Схема D-триггера, работающего по фронту

Временные диаграммы приведены на рисунке 5.11.

Рис. 5.11. Временные диаграммы D-триггера

40