begin process(C_int, CLR) begin

if CLR = '1' then read_s <= '0';

elsif falling_edge(C_int) then if read_s = '1' then

read_s <= '0'; else

read_s <= not nreadd; end if;

end if;

end process; C_out <= read_s; outt <= result;

end;

При помощи сигнала CLR производится асинхронный сброс. Если на CLR

подается пассивный уровень сигнала происходит проверка на значение сигнала read_s. Сигнал выходной синхронизации становится таким же, как и read_s а на выход outt подается сигнал result из предыдущего блока.

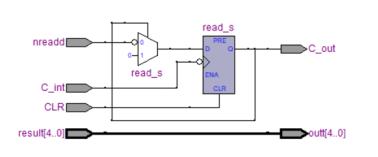

На рисунке 5.8 представлена схема из RTL viewer.

Рисунок 5.8 – Схема из RTL viewer 31

Заключение

В процессе выполнения работы была построена схема вычислительного блока, выполняющего преобразование двоичного кода в код МТК-2, логическую операцию А ∩ В и арифметическую операцию А-В, а также описана на VHDL.

Оба варианта были промоделированы согласно плану моделирования.

32