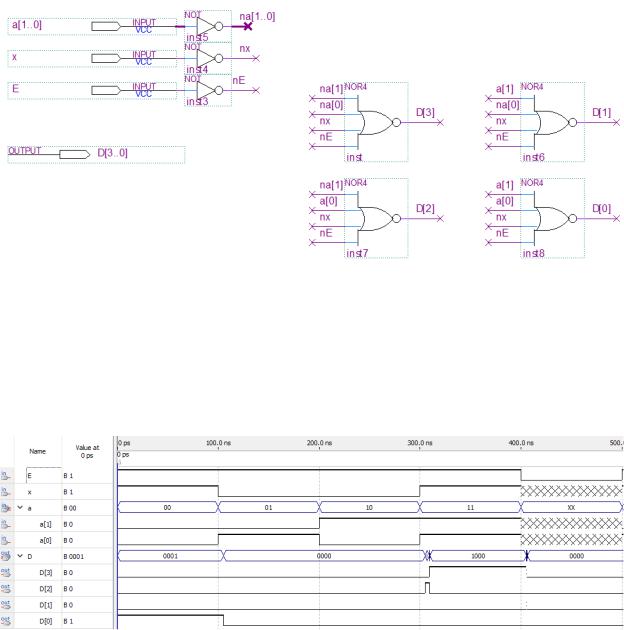

Рисунок 2.3.1 – Функциональная схема

E, x, a[1..0] – являются входами, D[3..0] – выходами, дающими результат схемы.

2.4 МОДЕЛИРОВАНИЕ

На рисунке 2.4.1 представлено моделирование схемы в режиме Timing.

Рисунок 2.4.1 – моделирование в режиме Timing

Так как моделирование в режиме Timing приближено к реальности и отображает задержки переключателя, из-за чего результат немного искажается от идеального. Сравнивания рисунок 2.4.1 и таблицу истинности 2.1.1, можно сделать вывод, что результаты совпадают.

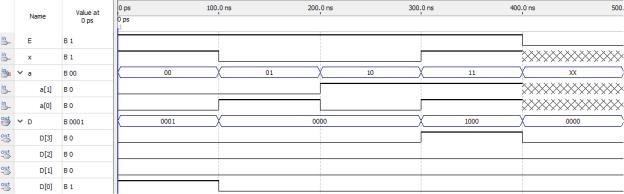

На рисунке 2.4.2 представлено моделирование схемы в режиме Functional.

11

Рисунок 2.4.2 моделирование в режиме Functional

Один временной интервал равняется 100 наносекунд. Если сравнивать моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

2.5 КОД НА HDL

Ниже представлен код схемы на SystemVerilog HDL: module MDX_1_8sv(

input logic [1:0] a, input logic x,

output logic [3:0] D); always @ (*)

begin case (a)

2'b00: D = x; 2'b01: D = x; 2'b10: D = x; 2'b11: D = x; default: ; endcase

end endmodule

x, a[1..0] – является входами, D[3..0] – выходом, выдающими результат схемы.

2.6 СХЕМА ДЛЯ КОДА HDL

На рисунке 2.6.1 представлена схема для кода HDL в RTL viewer.

12

Рисунок 2.6.1 – схема из RTL viewer для кода HDL

2.7 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ HDL

На рисунке 2.7.1 представлено моделирование кода в режиме Timing.

Рисунок 2.7.1 – моделирование схемы в режиме Timing

Из рисунка можно увидеть, что есть полная схожесть с таблицей истинности, а также с моделированием по схеме.

2.8 ТАБЛИЦА ИСТИННОСТИ МАСШТАБИРУЕМОГО УСТРОЙСТВА

В таблице 2.8.1 приведена таблица истинности для масштабируемого демультиплексора1-8(1 входов и 8 выхода).

13

Таблица 2.8.1 – таблица истинности масштабируемого демультиплексора1-8

|

|

Входы |

|

|

|

|

|

Выходы |

|

|

|

||

E |

a2 |

a1 |

|

a0 |

x |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

1 |

0 |

0 |

|

0 |

b0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b0 |

1 |

0 |

0 |

|

1 |

b1 |

0 |

0 |

0 |

0 |

0 |

0 |

b1 |

0 |

1 |

0 |

1 |

|

0 |

b2 |

0 |

0 |

0 |

0 |

0 |

b2 |

0 |

0 |

1 |

0 |

1 |

|

1 |

b3 |

0 |

0 |

0 |

0 |

b3 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

b4 |

0 |

0 |

0 |

b4 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

1 |

b5 |

0 |

0 |

b5 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

b6 |

0 |

b6 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

b7 |

b7 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

x |

x |

|

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

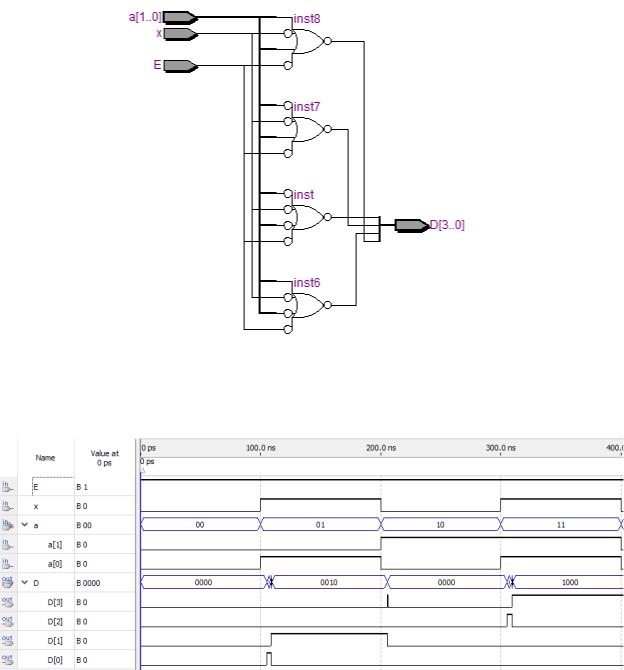

2.9 ФУНКЦИОНАЛЬНАЯ СХЕМА МАСШТАБИРУЕМОГО УСТРОЙСТВА

На рисунке 2.9.1 представлена функциональная схема масштабируемого устройства DMX.

Рисунок 2.9.1 – функциональная схема масштабируемого устройства E, x, a[2..0] – являются входами, D[7..0] – являются выходами, дающими

результат схемы.

2.10 МОДЕЛИРОВАНИЕ МАСШТАБИРУЕМОГО УСТРОЙСТВА

На рисунке 2.10.1 представлено моделирование схемы в режиме Timing.

14

Рисунок 2.10.1 – моделирование в режиме Timing

Так как моделирование в режиме Timing приближено к реальности и отображает задержки переключателя, из-за чего результат немного искажается от идеального. Сравнивания рисунок 2.10.1 и таблицу истинности 2.8.1, можно сделать вывод, что результаты совпадают.

На рисунке 2.10.2 представлено моделирование схемы в режиме Functional.

Рисунок 2.10.2 моделирование в режиме Functional

Один временной интервал равняется 100 наносекунд. Если сравнивать моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

2.11 КОД НА HDL МАСШТАБИРУЕМОГО УСТРОЙСТВА

Ниже представлен код схемы на VHDL: module DMX_1_8sv(

input logic [2:0] a, input logic x,

output logic [7:0] D); wire logic [1:0] out_D; always @ (*)

begin case (a[2])

1'b0: out_D = x; 1'b1: out_D = x; default: ; endcase

15

end

DMX_1_4 low (a[1:0], out_D, D[3:0]); DMX_1_4 high (a[1:0], out_D, D[7:4]); endmodule

x, a[2..0] – является входами,D[7..0] – выходами, выдающими результат схемы.

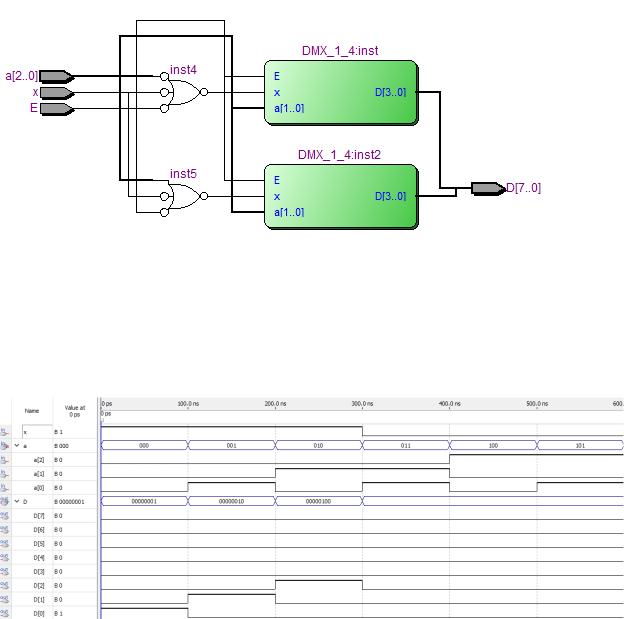

2.12 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL МАСШТАБИРУЕМОГО УСТРОЙСТВА

На рисунке 2.12.1 представлена схема из RTL viewer для кода HDL масштабируемого устройства.

Рисунок 2.12.1 – схема из RTL Viewer для кода HDL

2.13 МОДЕЛИРОВАНИЕ МАСШТАБИРУЕМОГО УСТРОЙСТВА, ОПИСАННОГО КОДОМ HDL

На рисунке 2.13.1 представлено моделирование масштабируемого устройства, описанного кодом HDL.

Рисунок 2.13.1 – моделирование масштабируемого устройства

16

3.РЕАЛИЗАЦИЯ ФУНКЦИИ НА ОСНОВЕ МУЛЬТИПЛЕКСОРА

3.1ТАБЛИЦА ИСТИННОСТИ

Втаблице 3.1.1 приведена таблица истинности для функции на основе мультиплексора.

Таблица 3.1.1 – таблица истинности

|

Входы |

|

|

Выход |

|

x |

y |

|

z |

w |

F |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

3.2ФОРМУЛА

=

3.3ФУНКЦИОНАЛЬНАЯ СХЕМА

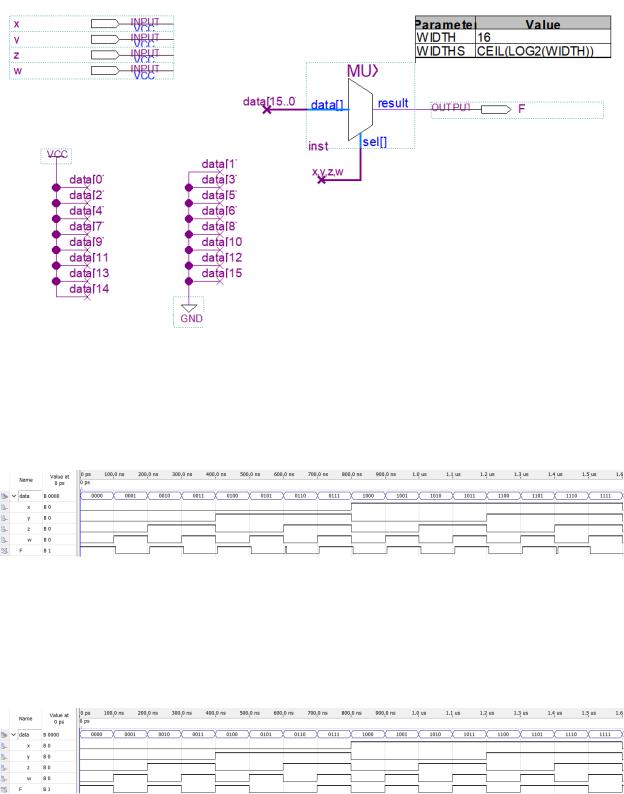

На рисунке 3.3.1 представлена функциональная схема.

17

Рисунок 3.3.1 – Функциональная схема

x,y,z,w – являются входами, F – выходом, дающим результат схемы.

3.4 МОДЕЛИРОВАНИЕ

На рисунке 3.4.1 представлено моделирование схемы в режиме Timing.

Рисунок 3.4.1 – моделирование в режиме Timing

Так как моделирование в режиме Timing приближено к реальности и отображает задержки переключателя, из-за чего результат немного искажается от идеального. Сравнивания рисунок 3.4.1 и таблицу истинности 3.1.1, можно сделать вывод, что результаты совпадают.

На рисунке 3.4.2 представлено моделирование схемы в режиме Functional.

Рисунок 3.4.2 моделирование в режиме Functional

Один временной интервал равняется 100 наносекунд. Если сравнивать моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

18

4.РЕАЛИЗАЦИЯ ФУНКЦИИ НА ОСНОВЕ ДЕШИФРАТОРА

4.1ТАБЛИЦА ИСТИННОСТИ

Втаблице 4.1.1 приведена таблица истинности для функции на основе дешифратора.

Таблица 4.1.1 – таблица истинности

|

Входы |

|

|

Выход |

|

x |

y |

|

z |

w |

F |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

4.2ФОРМУЛА

=

4.3ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 4.3.1 представлена функциональная схема.

19

Рисунок 4.3.1 – Функциональная схема

x,y,z,w – являются входами, F – выходом, дающим результат схемы.

4.4 МОДЕЛИРОВАНИЕ

На рисунке 4.4.1 представлено моделирование схемы в режиме Timing.

Рисунок 4.4.1 – моделирование в режиме Timing

Так как моделирование в режиме Timing приближено к реальности и отображает задержки переключателя, из-за чего результат немного искажается от идеального. Сравнивания рисунок 4.4.1 и таблицу истинности 4.1.1, можно сделать вывод, что результаты совпадают.

На рисунке 3.4.2 представлено моделирование схемы в режиме Functional.

Рисунок 4.4.2 моделирование в режиме Functional

Один временной интервал равняется 100 наносекунд. Если сравнивать моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

20