Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение

высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ

УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ РЕГИСТРОВ

Отчет по лабораторной работе №6 по дисциплине «Электроника и схемотехника 2»

Вариант №18

__.__.2022

Руководитель

_______

__.__.2022

Томск 2022

Введение

Цель работы – изучить регистры, их принципы построения и работы.

Постановка задачи. Составить таблицы функционирования для заданных схем. Собрать схемы заданных регистров. Промоделировать все схемы, а

также привести код на HDL и промоделировать.

1.РЕГИСТР ТИПА SISO

1.1ТАБЛИЦА ИСТИННОСТИ

Втаблице 1.1.1 приведена таблица функционирования асинхронного вычитающего счётчика на основе D триггера.

Таблица 1.1.1 – таблица функционирования

№ |

|

Входы |

|

|

Выходы |

|

сигнала |

a |

|

R |

L |

|

Q9 |

1 |

a1 |

|

0 |

0 |

|

0 |

2 |

a2 |

|

0 |

0 |

|

0 |

3 |

a3 |

|

0 |

0 |

|

0 |

4 |

a4 |

|

0 |

0 |

|

0 |

5 |

a5 |

|

0 |

0 |

|

0 |

6 |

a6 |

|

0 |

0 |

|

0 |

7 |

a7 |

|

0 |

0 |

|

0 |

8 |

a8 |

|

0 |

0 |

|

0 |

9 |

a9 |

|

0 |

0 |

|

0 |

10 |

a10 |

|

0 |

0 |

|

a1 |

11 |

a11 |

|

0 |

0 |

|

a2 |

12 |

a12 |

|

0 |

0 |

|

a3 |

13 |

a13 |

|

1 |

0 |

|

0 |

14 |

a14 |

|

0 |

1 |

|

b9 |

15 |

a15 |

|

0 |

0 |

|

x |

1.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

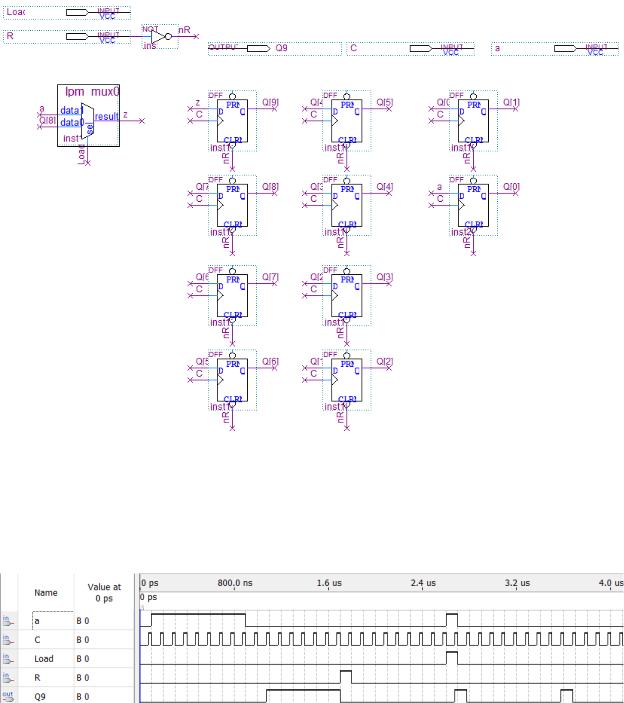

На рисунке 1.2.1 приведена функциональная схема для регистра типа SISO.

Рисунок 1.2.1 – функциональная схема

1.3 МОДЕЛИРОВАНИЕ

На рисунке 1.3.1 представлено моделирование в режиме Functional.

Рисунок 1.3.1 – моделирование схемы в режиме Funtional

Один временной интервал равен 100 наносекунд. Если сравнить моделирование с таблицей истинности, то они совпадают.

На рисунке 1.3.2 представлено моделирование в режиме Timing.

Рисунок 1.3.2 – моделирование в режиме Timing

Так как моделирование в режиме Timing приближено к реальности и

отображает задержки переключения, из-за чего результат немного искажается

от идеального.

1.4 КОД НА HDL

Ниже представлен код на VHDL:

library ieee;

use ieee.std_logic_1164.all; entity SISO_v is

port (

C, R: in std_logic; Load, a: in std_logic; Q9: out std_logic); end;

architecture synth of SISO_v is

signal z: std_logic_vector (9 downto 0); begin

process (C, R) begin

if R = '1' then z <= (others => '0'); elsif rising_edge(C) then

if Load = '1' then z(9) <= a; else z <= z(8 downto 0) & a; end if;

end if;

end process; Q9 <= z(9); end;

1.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисунке 1.5.1 приведена схема из RTL Viewer для кода HDL.

Рисунок 1.5.1 – схема из RTL Viewer

1.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ

HDL

На рисунке 1.6.1 представлено моделирование в режиме Timing для кода

HDL.

Рисунок 1.6.1 – моделирование устройства, описанного кодом HDL

Сравнивая результат моделирования и таблицу истинности, можно сделать выводы о том, что они совпадают.

2.РЕГИСТР ТИПА SIPO

2.1ТАБЛИЦА ИСТИННОСТИ

Втаблице 2.1.1 приведена таблица функционирования асинхронного вычитающего счётчика на основе D триггера.

Таблица 2.1.1 – таблица функционирования

№ |

Входы |

|

|

|

|

Выходы |

|

|

|

|

|

|||

сигнала |

a |

R |

Q11 |

Q10 |

Q9 |

Q8 |

Q7 |

Q6 |

Q5 |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

1 |

a1 |

0 |

a1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

2 |

a2 |

0 |

a2 |

a1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

3 |

a3 |

0 |

a3 |

a2 |

a1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

4 |

a4 |

0 |

a4 |

a3 |

a2 |

a1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

5 |

a5 |

0 |

a5 |

a4 |

a3 |

a2 |

a1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

6 |

a6 |

0 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

0 |

0 |

0 |

0 |

0 |

0 |

7 |

a7 |

0 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

0 |

0 |

0 |

0 |

0 |

8 |

a8 |

0 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

0 |

0 |

0 |

0 |

9 |

a9 |

0 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

0 |

0 |

0 |

10 |

a10 |

0 |

a10 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

0 |

0 |

11 |

a11 |

0 |

a11 |

a10 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

0 |

12 |

a12 |

0 |

a12 |

a11 |

a10 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

a1 |

13 |

a13 |

0 |

a13 |

a12 |

a11 |

a10 |

a9 |

a8 |

a7 |

a6 |

a5 |

a4 |

a3 |

a2 |

14 |

a14 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

2.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 2.2.1 приведена функциональная схема для регистра типа SIPO.

Рисунок 2.2.1 – функциональная схема

2.3 МОДЕЛИРОВАНИЕ

На рисунке 2.3.1 представлено моделирование в режиме Functional.

Рисунок 2.3.1 – моделирование схемы в режиме Funtional

Один временной интервал равен 100 наносекунд. Если сравнить моделирование с таблицей истинности, то они совпадают.

На рисунке 2.3.2 представлено моделирование в режиме Timing.

Рисунок 2.3.2 – моделирование в режиме Timing

Так как моделирование в режиме Timing приближено к реальности и

отображает задержки переключения, из-за чего результат немного искажается

от идеального.

2.4 КОД НА HDL

Ниже представлен код на VHDL:

library ieee;

use ieee.std_logic_1164.all; entity SIPO_v is

port (

C, R, a: in std_logic;

Q: out std_logic_vector (11 downto 0)); end;

architecture synth of SIPO_v is

signal z: std_logic_vector (11 downto 0); begin

Q <= z;

process (C) begin

if rising_edge(C) then

if R = '1' then z <= (others => '0'); else z <= a & z (11 downto 1); end if;

end if;

end process; end;

2.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисунке 2.5.1 приведена схема из RTL Viewer для кода HDL.

Рисунок 2.5.1 – схема из RTL Viewer

2.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ

HDL

На рисунке 2.6.1 представлено моделирование в режиме Timing для кода

HDL.

Рисунок 2.6.1 – моделирование устройства, описанного кодом HDL

Сравнивая результат моделирования и таблицу истинности, можно сделать выводы о том, что они совпадают.