Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ЛОГИЧЕЕСКИЕ ЭЛЕМЕНТЫ

Отчет по лабораторной работе №1 по дисциплине «Электроника и схемотехника 2»

Вариант №18

Студент гр.

__.__

Руководитель

__.__.2022

Томск 2022

Введение

Цель работы – изучить основные инструменты САПР QuartusII и научиться моделировать в ней работу схем на основе простых логических элементов.

Постановка задачи. Собрать на холсте и продемонстрировать работу схем 2И, 2ИЛИ, 2искл.ИЛИ, 2И-НЕ, 2ИЛИ-НЕ и схему по варианту в двух режимах. Описать логические элементы на SystemVerilog HDL и промоделировать их в двух режимах. Составить таблицу истинности для логических элементов и сверить ее с результатами моделирования.

Схема по варианту: = , где «*» - логическое И, « » - логическое исключающее ИЛИ.

2

1. УСТРОЙСТВО 2И

1.1ТАБЛИЦА ИСТИННОСТИ

Данное устройство дает на выходе логический сигнал 1 только тогда, когда на обоих входах логический сигнал 1.

Таблица 1.1.1 – таблица истинности 2И

a |

b |

a*b |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1.2 ФОРМУЛА

Формула этой логической операции выглядит следующим образом:

=

1.3 ФУНКЦИОНАЛЬНАЯ СХЕМА

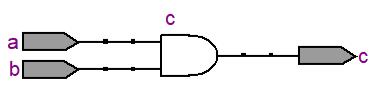

На рисунке 1.3.1 представлена функциональная схема 2И.

Рисунок 1.3.1 – Функциональная схема 2И

a,b являются входами, а c – выходом, выдающим результат схемы 2И.

1.4 КОД НА SYSTEMVERIILOG HDL

Ниже приведен код схемы 2И: module and_2(

input a, b, output c); assign c = a&b; endmodule

a,b являются входами, а c – выходом, выдающим результат схемы 2И.

1.5 МОДЕЛИРОВАНИЕ

На рисунке 1.5.1 представлено моделирование схемы 2И в режиме Timing.

3

Рисунок 1.5.1 – моделирование в режиме Timing

Так как моделирование в режиме timing приближено к реальности и отображает задержки переключения, из-за чего результат немного искажается от идеального.

На рисунке 1.5.2 представлено моделирование схемы 2И в режиме

Functional.

Рисунок 1.5.2 – моделирование в режиме Functional

Один временной интервал равен 100 наносекунд. Если сравнить моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

4

2.УСТРОЙСТВО 2ИЛИ

2.1ТАБЛИЦА ИСТИННОСТИ

Данное устройство дает на выходе логический сигнал 0 только тогда, когда на обоих входах логический сигнал 0.

Таблица 2.1.1 – таблица истинности 2ИЛИ

a |

b |

а+b |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

2.2 ФОРМУЛА

Формула этой логической операции выглядит следующим образом:

=

2.3 ФУНКЦИОНАЛЬНАЯ СХЕМА

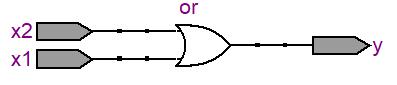

На рисунке 2.3.1 представлена функциональная схема 2ИЛИ.

Рисунок 2.3.1 – Функциональная схема 2ИЛИ

x1,x2 являются входами, а y – выходом, выдающим результат схемы 2ИЛИ.

2.4 КОД НА SYSTEMVERIILOG HDL

Ниже приведен код схемы 2ИЛИ: module or_2(

input x1,x2, output y);

assign y = x1 | x2; endmodule

x1,x2 являются входами, а y – выходом, выдающим результат схемы 2ИЛИ.

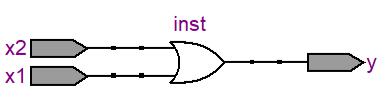

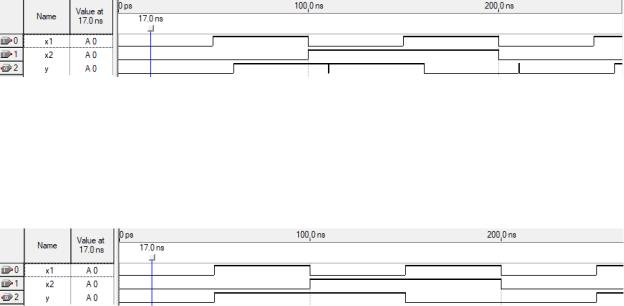

2.5 МОДЕЛИРОВАНИЕ

На рисунке 2.5.1 представлено моделирование схемы 2ИЛИ в режиме

Timing.

5

Рисунок 2.5.1 – моделирование в режиме Timing

Так как моделирование в режиме timing приближено к реальности и отображает задержки переключения, из-за чего результат немного искажается от идеального.

На рисунке 2.5.2 представлено моделирование схемы 2ИЛИ в режиме

Functional.

Рисунок 2.5.2 – моделирование в режиме Functional

Один временной интервал равен 100 наносекунд. Если сравнить моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

6

3. УСТРОЙСТВО 2ИСКЛ.ИЛИ

3.1 ТАБЛИЦА ИСТИННОСТИ

Данное устройство дает на выходе логический сигнал 0 только тогда, когда на обоих входах логический сигнал 0 или на обоих 1.

Таблица 3.1.1 – таблица истинности 2искл.ИЛИ

a |

b |

а b |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

3.2 ФОРМУЛА

Формула этой логической операции выглядит следующим образом:

=

3.3 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 3.3.1 представлена функциональная схема 2искл.ИЛИ.

Рисунок 3.3.1 – Функциональная схема 2искл.ИЛИ

x1,x2 являются входами, а y – выходом, выдающим результат схемы 2искл.ИЛИ.

3.4 КОД НА SYSTEMVERIILOG HDL

Ниже приведен код схемы 2искл.ИЛИ: module x_orsv (

input x1, x2, output y);

assign y = x1 ^ x2; endmodule

x1,x2 являются входами, а y – выходом, выдающим результат схемы 2искл.ИЛИ.

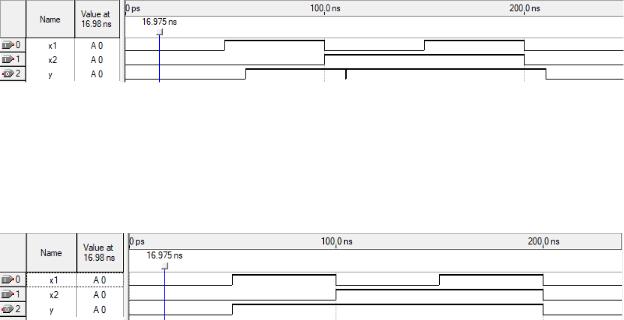

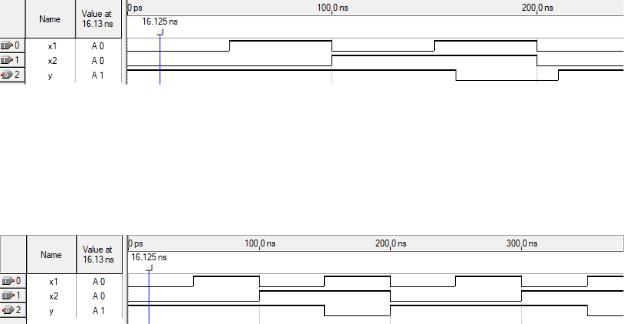

3.5 МОДЕЛИРОВАНИЕ

На рисунке 3.5.1 представлено моделирование схемы 2искл.ИЛИ в режиме

Timing.

7

Рисунок 3.5.1 – моделирование в режиме Timing

Так как моделирование в режиме timing приближено к реальности и отображает задержки переключения, из-за чего результат немного искажается от идеального.

На рисунке 3.5.2 представлено моделирование схемы 2искл.ИЛИ в режиме

Functional.

Рисунок 3.5.2 – моделирование в режиме Functional

Один временной интервал равен 100 наносекунд. Если сравнить моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

8

4.УСТРОЙСТВО 2И-НЕ

4.1ТАБЛИЦА ИСТИННОСТИ

Данное устройство дает на выходе логический сигнал 0 только тогда, когда на обоих входах логический сигнал 1.

Таблица 4.1.1 – таблица истинности 2И-НЕ.

a |

b |

|

|

|

|

|

|

||

0 |

0 |

|

1 |

|

0 |

1 |

|

1 |

|

1 |

0 |

|

1 |

|

1 |

1 |

|

0 |

|

4.2 ФОРМУЛА

Формула этой логической операции выглядит следующим образом:

=

4.3 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 4.3.1 представлена функциональная схема 2И-НЕ.

Рисунок 4.3.1 – Функциональная схема 2И-НЕ

x1,x2 являются входами, а y – выходом, выдающим результат схемы 2ИНЕ.

4.4 КОД НА SYSTEMVERIILOG HDL

Ниже приведен код схемы 2И-НЕ: module notand(

input x1,x2, output y);

assign y = ~(x1 & x2); endmodule

x1,x2 являются входами, а y – выходом, выдающим результат схемы 2ИНЕ.

4.5 МОДЕЛИРОВАНИЕ

На рисунке 4.5.1 представлено моделирование схемы 2И-НЕ в режиме

Timing.

9

Рисунок 4.5.1 – моделирование в режиме Timing

Так как моделирование в режиме timing приближено к реальности и отображает задержки переключения, из-за чего результат немного искажается от идеального.

На рисунке 4.5.2 представлено моделирование схемы 2И-НЕ в режиме

Functional.

Рисунок 4.5.2 – моделирование в режиме Functional

Один временной интервал равен 100 наносекунд. Если сравнить моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

10