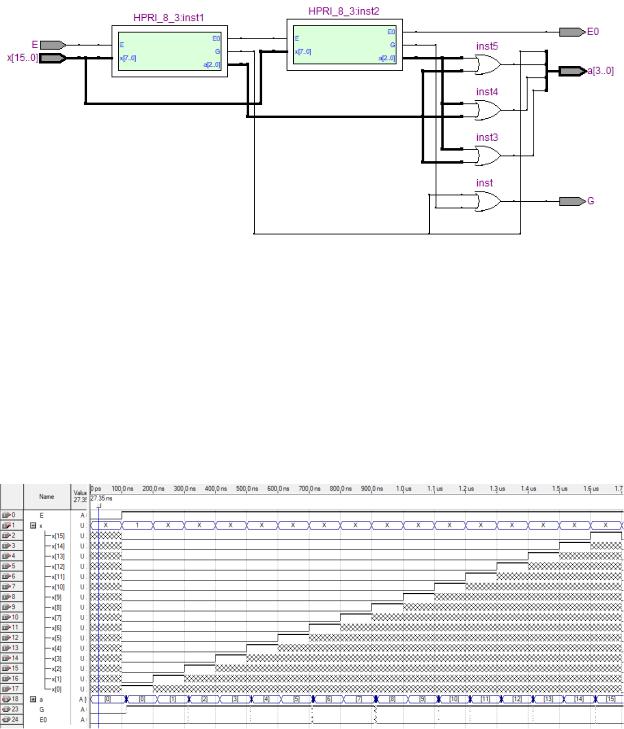

Рисунок 3.9.1 – функциональная схема масштабируемого устройства

HPRI

E, x[15..0] – являются входами, E0, a[3..0], G – являются выходами, дающими результат схемы.

3.10 МОДЕЛИРОВАНИЕ МАСШТАБИРУЕМОГО УСТРОЙСТВА

На рисунке 3.10.1 представлено моделирование схемы в режиме Timing.

Рисунок 3.10.1 – моделирование в режиме Timing

Так как моделирование в режиме Timing приближено к реальности и отображает задержки переключателя, из-за чего результат немного искажается от идеального. Сравнивания рисунок 3.10.1 и таблицу истинности 3.8.1, можно сделать вывод, что результаты совпадают.

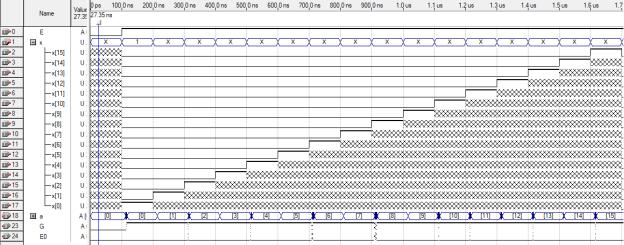

На рисунке 3.10.2 представлено моделирование схемы в режиме Functional.

21

Рисунок 3.10.2 моделирование в режиме Functional

Один временной интервал равняется 100 наносекунд. Если сравнивать моделирование в режиме Functional, то оно полностью совпадает с таблицей истинности.

3.11 КОД НА HDL МАСШТАБИРУЕМОГО УСТРОЙСТВА

Ниже представлен код схемы на VHDL: library ieee;

use ieee.std_logic_1164.all; entity HPRI_16_4sv is

port (

x: in STD_LOGIC_VECTOR (7 downto 0); E: in STD_LOGIC;

G: out STD_LOGIC; E0:out STD_LOGIC;

a: out STD_LOGIC_VECTOR (3 downto 0) );

end;

architecture sync of HPRI_16_4sv is component HPRI_8_31 is

port (

x: in STD_LOGIC_VECTOR (7 downto 0); E: in STD_LOGIC;

a: out STD_LOGIC_VECTOR (3 downto 0); G: out STD_LOGIC;

E0:out STD_LOGIC );

end component;

signal G0, G1, E00:std_logic;

signal a0, a1:std_logic_vector(3 downto 0); begin

22

HPRI1:HPRI_8_31

port map(x(15 downto 8), E, a1, G1, E00); HPRI0:HPRI_8_31

port map(x(7 downto 0), E00, a0, G0, E0); G <= G0 or G1;

a(3) <= G1;

a(2) <= a0(2) or a1(2);

a(1) <= a0(1) or a1(1);

a(0) <= a0(0) or a1(0); end;

E, x[15..0] – является входами,E0, G, a[3..0] – выходами, выдающими результат схемы.

3.12 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL МАСШТАБИРУЕМОГО УСТРОЙСТВА

На рисунке 3.12.1 представлена схема из RTL viewer для кода HDL масштабируемого устройства.

Рисунок 3.12.1 – схема из RTL Viewer для кода HDL

3.13 МОДЕЛИРОВАНИЕ МАСШТАБИРУЕМОГО УСТРОЙСТВА, ОПИСАННОГО КОДОМ HDL

На рисунке 3.13.1 представлено моделирование масштабируемого устройства, описанного кодом HDL.

23

Рисунок 3.13.1 – моделирование масштабируемого устройства

24

Заключение

Врезультате выполнения лабораторной работы были получены навыки создания шифраторов и дешифраторов на разных базисах, а также навыки решения задач по увеличению размерности.

Впроцессе выполнения работы были построены:

-Шифратор на базисе И-НЕ

-Дешифратор на базисе ИЛИ-НЕ

-Приоритетный шифратор на базисе И, ИЛИ, НЕ

Также была выполнена задача по увеличению размерности приоритетного шифратора с 8 входов до 16.

25