3. ДЕЛИТЕЛЬ ЧАСТОТЫ

3.1 РАСЧЕТЫ

Ниже приведены расчеты для построения схемы:

Tвх = 20нс

Fвых = 1724138Гц

Tвых = 1/Fвых = 580нс

M = Tвых/Tвх = 29

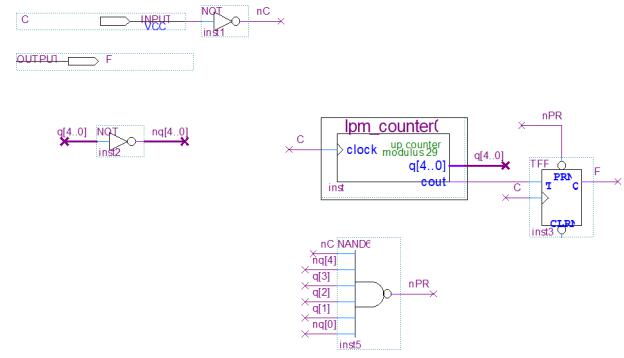

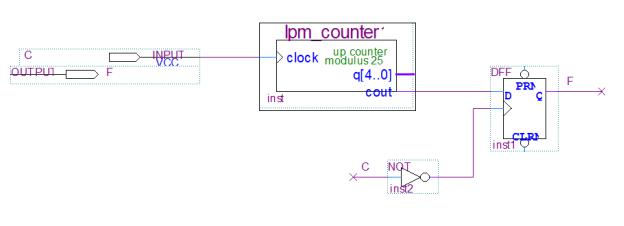

3.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 3.2.1 приведена функциональная схема для делителя чистоты.

Рисунок 3.2.1 – функциональная схема

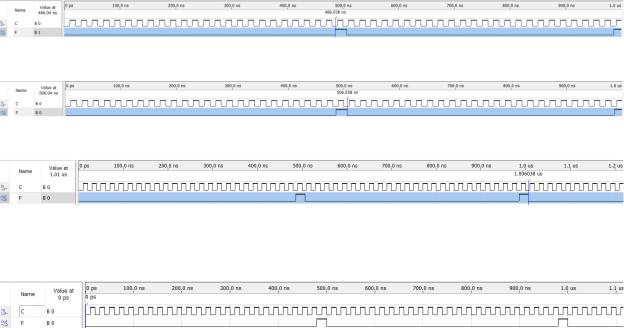

3.3 МОДЕЛИРОВАНИЕ

На рисунках 3.4.1-3.3 представлены разные переходы в режиме Timing.

Рисунок 3.4.1 – переход из 1 в 0

Рисунок 3.4.2 – переход из 0 в 1

Рисунок 3.4.3 – переход из 1 в 0(окончание периода)

На рисунке 3.4.5 представлено моделирование в режиме Functional.

Рисунок 3.4.5 – моделирование в режиме Funtional

Ниже приведена проверка интервалов и периода:

866.187 – 575.906 = 290.281

1155.906 – 866.187 = 289.719

290.281+289.719 = 580

3.4 КОД НА HDL

Ниже представлен код на SystemVeriLog HDL:

module del_sv ( input C,

output F); logic [4:0] q;

logic nPR, cout, m;

assign nPR = ~(~C & ~q[4] & q[3] & q[2] & q[1] & ~q[0]); assign m = q[4] & q[3] & q[2] & ~q[1] & ~q[0];

always_ff @ (posedge ~C) begin if (m) begin

q <= 5'd0; cout <= 1'b0;

end

else begin

q <= q + 1'b1;

if (q[4] & q[3] & ~q[2] & q[1] & q[0]) cout <= 1'b1; end

end

always_ff @ (posedge C, negedge nPR) begin if (~nPR) F <= 1'b1;

else if (cout) F <= ~F; end

endmodule

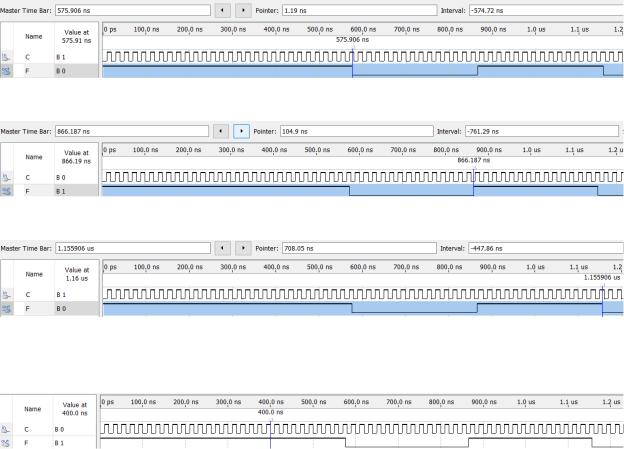

3.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисунке 3.5.1 приведена схема из RTL Viewer для кода HDL.

Рисунок 3.5.1 – схема из RTL Viewer

3.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ

HDL

На рисунках 3.6.1 – 3.6.3 представлено моделирование в режиме Timing для

кода HDL.

Рисунок 3.6.1 – переход из 1 в 0

Рисунок 3.6.2 – переход из 0 в 1

Рисунок 3.6.3 – переход из 1 в 0(окончание периода)

На рисунке 3.6.4 представлено моделирование в режиме Functional.

Рисунок 3.6.4 – моделирование в режиме Functional

4. ФОРМИРОВАТЕЛЬ ЗАДЕРЖКИ

4.1 РАСЧЕТЫ

Ниже приведены расчеты для построения схемы:

Fвх = 50МГц

Tвх = 1/Fвх = 20 нс tз = 480мс

t0вых = 480мс

t1вых = 50мс

M1 = tвых/Tвх = 1

M0 = tз/Tвх = 24

M = M0 + M1 = 25

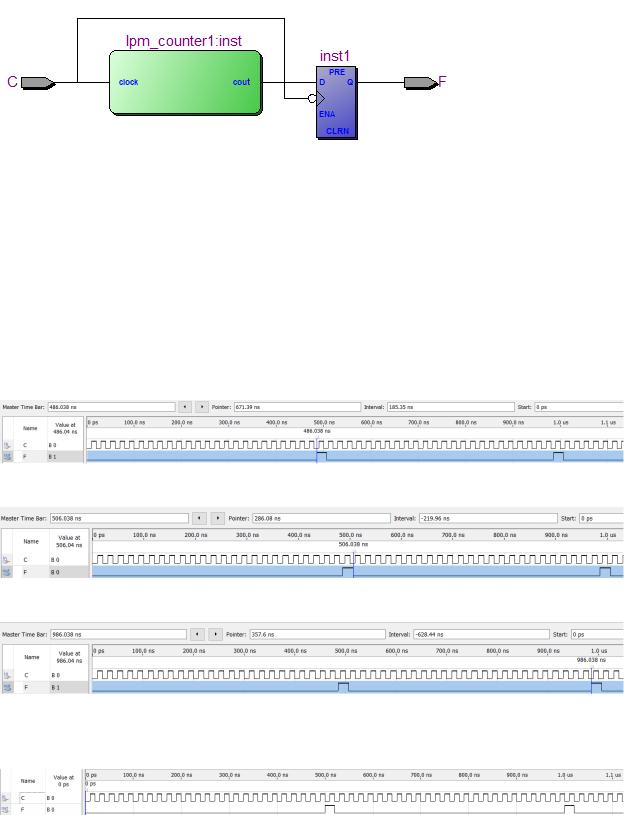

4.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

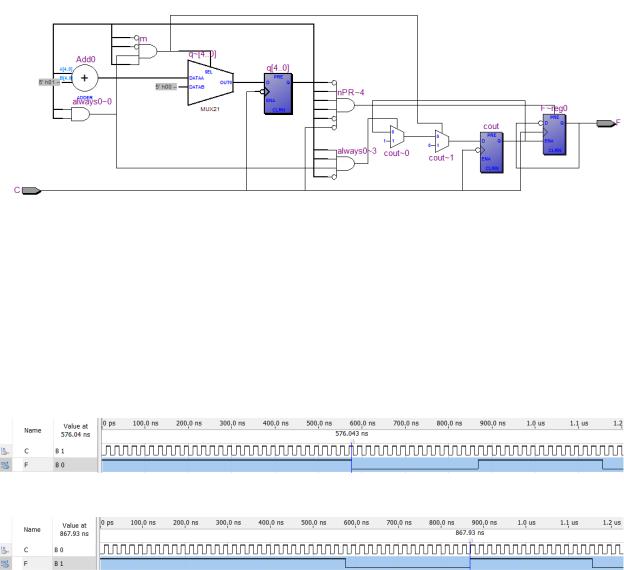

На рисунке 4.2.1 приведена функциональная схема для формирователя задержки.

Рисунок 4.2.1 – функциональная схема

4.3 МОДЕЛИРОВАНИЕ

На рисунках 4.3.1-4.3.3 представлены разные переходы в режиме Timing.

Рисунок 4.4.1 – переход из 0 в 1

Рисунок 4.4.2 – переход из 1 в 0

Рисунок 4.4.3 – переход из 0 в 1(окончание периода)

На рисунке 4.4.4 представлено моделирование в режиме Functional.

Рисунок 4.4.4 – моделирование в режиме Functional

Ниже приведена проверка интервалов и периода:

506.038 – 486.038 = 20

986.038 – 506.038 = 480

1006.038 - 986.038 = 20

4.4 КОД НА HDL

Ниже представлен код на SystemVeriLog HDL:

module delay_sv ( input C,

output F); logic [4:0] q; logic cout, m;

assign m = q[4] & q[3] & ~q[2] & ~q[1] & ~q[0]; assign cout = m;

always_ff @ (posedge ~C) begin if (m)

q <= 5'd0; else

q <= q + 1'b1; end

always_ff @ (posedge ~C) begin F <= cout;

end endmodule

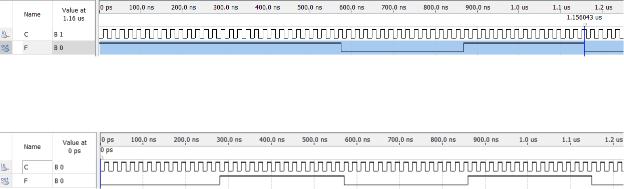

4.5 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисунке 4.5.1 приведена схема из RTL Viewer для кода HDL.

Рисунок 4.5.1 – схема из RTL Viewer

4.6 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ

HDL

На рисунках 4.6.1 – 4.6.3 представлено моделирование в режиме Timing для кода HDL.

Рисунок 4.6.1 – переход из 0 в 1

Рисунок 4.6.2 – переход из 1 в 0

Рисунок 4.6.3 – переход из 0 в 1(окончание периода)

На рисунке 4.6.4 представлено моделирование в режиме Functional.

Рисунок 4.6.4 – моделирование в режиме Functional

Заключение

В результате выполнения лабораторной работы были изучены двоичные

счетчики, их принципы построения и работы, а также выполнены следующие

задачи:

-Составлены таблицы истинности для счетчиков, выполнены расчеты для делителя частоты и формирователя задержки.

-Собраны схемы на холстах и промоделированы эти схемы

-написан код для каждой из схем и так промоделированы