Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение

высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ

УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ ТРИГГЕРОВ

Отчет по лабораторной работе №4 по дисциплине «Электроника и схемотехника 2»

Вариант №18

__.__.2022

Руководитель

_______

__.__.2022

Томск 2022

Введение

Цель работы – изучить основные типы триггеров, их принципы построения и работы.

Постановка задачи. Составить таблицы функционирования для схем согласно варианту. Собрать схемы заданных триггеров и промоделировать работу. Также исследовать минимальный порог длительности активного уровня управляющего сигнала.

2

1. СТАТИЧЕСКИЙ ДВУХСТУПЕНЧАТЫЙ RS ТРИГГЕР В

БАЗИСЕ ИЛИ-НЕ

1.1ТАБЛИЦА ИСТИННОСТИ

Втаблице 1.1.1 приведена таблица функционирования статического двухступенчатого RS триггера.

Таблица 1.1.1 – таблица функционирования

Входы |

|

Выходы |

|

Переход |

Режим |

|||

|

|

|

|

|

|

|

||

R |

S |

C |

Q1(t) |

Q1(t+1) |

Q(t) |

Q(t+1) |

|

|

|

|

|

|

|

|

|

|

|

x |

0 |

1 |

0 |

0 |

0 |

0 |

0→0 |

Установка в 0 |

|

|

|

|

|

|

|

|

|

x |

x |

0 |

0 |

0 |

0 |

0 |

0→0 |

Хранение |

|

|

|

|

|

|

|

|

|

1 |

x |

1 |

1 |

1 |

1 |

1 |

1→1 |

Установка в 1 |

|

|

|

|

|

|

|

|

|

x |

x |

0 |

1 |

1 |

1 |

1 |

1→1 |

Хранение |

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0→1 |

Установка в 1 |

|

|

|

|

|

|

|

|

|

x |

x |

0 |

1 |

1 |

0 |

1 |

0→1 |

Установка в 1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1→0 |

Установка в 0 |

|

|

|

|

|

|

|

|

|

x |

x |

0 |

0 |

0 |

1 |

0 |

1→0 |

Установка в 0 |

|

|

|

|

|

|

|

|

|

1.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

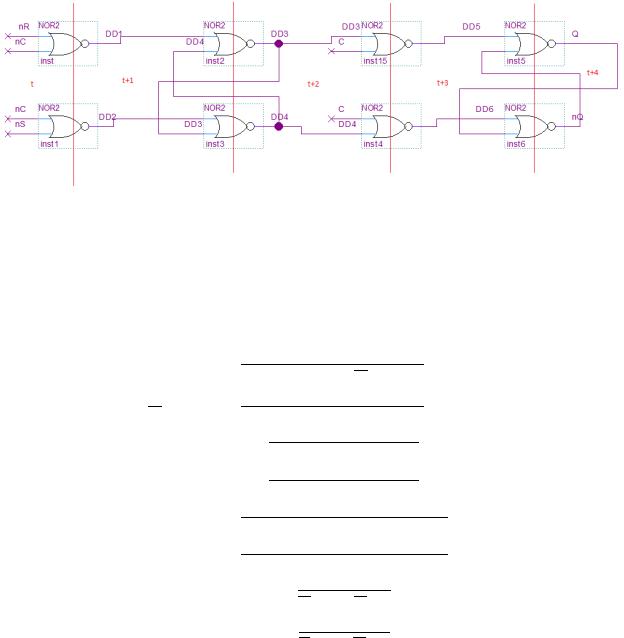

На рисунке 1.2.1 приведена функциональная схема для статического двухступенчатого RS триггера с обозначением временных окон.

На данной схеме DD3 = Q1, DD4 = nQ1.

3

Рисунок 1.2.1 – функциональная схема

1.3 ФОРМУЛА

Ниже приведены формулы по схеме с учётом временной составляющей в базисе ИЛИ-НЕ:

( + 4) = 5( + 3) ( + 3)( + 4) = 6( + 3) ( + 3)5( + 3) = 3( + 2) ( )6( + 3) = 4( + 2) ( )

3( + 2) = 1( + 1) 4( + 1)4( + 2) = 2( + 1) 3( + 1)

1( + 1) = ( ) ( )2( + 1) = ( ) ( )

1.4 МОДЕЛИРОВАНИЕ

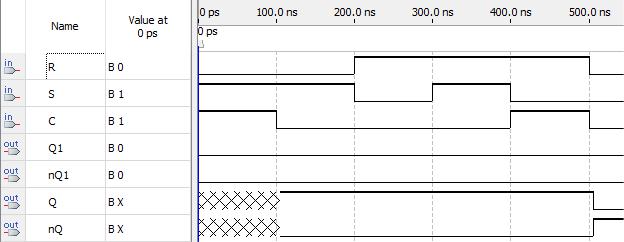

На рисунке 1.4.1 представлено моделирование в нужных режимах:

установка в 0, хранение, установка в 1.

4

Рисунок 1.4.1 – моделирование схемы в режиме Funtional

На рисунке 1.4.1 можно увидеть 3 режима работы триггера. Интервал равен

10 наносекундам. С 0 до 10 наносекунд идёт режим установки в 1, его можно также увидеть в таблице 1.1.1. С 10 до 40 представлен режим хранения. При С=0 никакие изменения не наблюдаются, как и в таблице 1.1.1. С 40 до 50

режим установки в 0 с переходом 1→0.

На рисунках 1.4.2 и 1.4.3 можно увидеть минимальный порог длительности активного уровня управляющего сигнала.

Рисунок 1.4.2 – Плохая работа триггера

Рисунок 1.4.3 – хорошая работа триггера Интервал был взят в 100 пикосекунд. И как видно из рисунков 800

пикосекунд недостаточно для нормальной работы триггера.

5

1.5 КОД НА HDL

Ниже представлен код на VHDL:

library ieee;

use ieee.std_logic_1164.all; entity RS_trigger_V is port(

R:in std_logic;

S:in std_logic;

C:in std_logic;

Q:buffer std_logic; nQ: buffer std_logic; Q1: buffer std_logic; nQ1: buffer std_logic); end;

architecture sync of RS_trigger_V is

signal DD1, DD2, DD5, DD6, nC, DD3, DD4: std_logic; begin

process (all) begin nC <= not (C);

Q <= not (DD5 or nQ); nQ <= not (DD6 or Q); DD5 <= not (DD3 or C); DD6 <= not (DD4 or C);

DD3 <= not (DD1 or DD4); DD4 <= not (DD2 or DD3); DD1 <= not (not (R) or not (C)); DD2 <= not (not (S) or not (C)); end process;

end;

1.6СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисунке 1.6.1 приведена схема из RTL Viewer для кода HDL.

Рисунок 1.6.1 – схема из RTL Viewer 6

1.7 МОДЕЛИРОВАНИЕ УСТРОЙСТВА, ОПИСАННОГО КОДОМ

HDL

На рисунке 1.7.1 представлено моделирование в режиме Timing для кода

HDL.

Рисунок 1.7.1 – моделирование устройства, описанного кодом HDL

7

2.ДИНАМИЧЕСКИЙ T ТРИГГЕР В БАЗИСЕ И-НЕ

2.1ТАБЛИЦА ИСТИННОСТИ

Втаблице 2.1.1 приведена таблица функционирования динамического T-

триггера.

Таблица 2.1.1 – таблица функционирования

Входы |

|

Выходы |

Режим |

|

|

|

|

|

|

C |

Q(t) |

|

Q(t+1) |

|

|

|

|

|

|

0 |

0 |

|

0 |

Хранение |

|

|

|

|

|

0 |

1 |

|

1 |

Хранение |

|

|

|

|

|

1 |

0 |

|

1 |

Счётный из 0 в 1 |

|

|

|

|

|

1 |

1 |

|

0 |

Счётный из 1 в 0 |

|

|

|

|

|

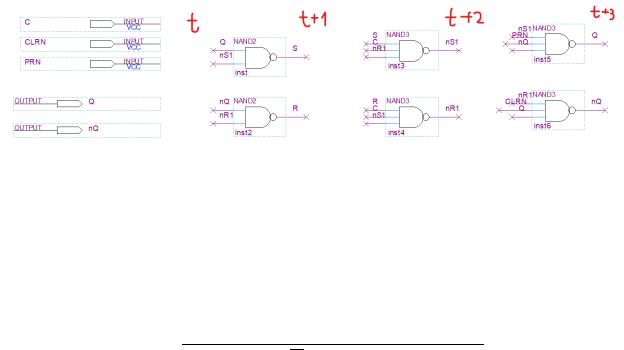

2.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 2.2.1 приведена функциональная схема для динамического T-

триггера с обозначением временных окон.

Рисунок 2.2.1 – функциональная схема

2.3 ФОРМУЛА

Ниже приведены формулы по схеме с учётом временной составляющей в базисе И-НЕ:

( + 3) = 1( + 2) ∩ ( + 2) ∩ ( + 2)

8

( + 3) = 1( + 2) ∩ ( + 2) ∩ ( + 2)1( + 2) = ( + 1) ∩ ( + 1) ∩ 1( + 1)1( + 2) = ( + 1) ∩ ( + 1) ∩ 1( + 1)

( + 1) = ( ) ∩ 1( )( + 1) = ( ) ∩ 1( )

2.4 МОДЕЛИРОВАНИЕ

На рисунке 2.4.1 представлено моделирование в режиме Functional.

Рисунок 2.4.1 – моделирование схемы в режиме Funtional

Интервал равен 100 наносекундам. Результат моделирования совпадает с таблицей истинности.

На рисунках 2.4.2 и 2.4.3 можно увидеть минимальный порог длительности активного уровня управляющего сигнала.

Рисунок 2.4.2 – Плохая работа триггера

9

Рисунок 2.4.3 – хорошая работа триггера

Интервал был взят в 100 пикосекунд. И как видно из рисунков 800

пикосекунд недостаточно для нормальной работы триггера.

2.5 КОД НА HDL

Ниже представлен код на VHDL:

library ieee;

use ieee.std_logic_1164.all; entity d_T_v is

port (

C:in std_logic; CLRN:in std_logic; PRN:in std_logic; Q:buffer std_logic; nQ:buffer std_logic); end;

architecture synth of d_T_v is signal S, nS1, R, nR1: std_logic; begin

process (all) begin

Q <= not (PRN and nS1 and nQ); nQ <= not (CLRN and nR1 and Q); S <= not (Q and nS1);

R <= not (nQ and nR1);

nS1 <= not (S and C and nR1); nR1 <= not (R and C and nS1); end process;

end;

2.6 СХЕМА ИЗ RTL VIEWER ДЛЯ КОДА HDL

На рисунке 2.6.1 приведена схема из RTL Viewer для кода HDL. 10