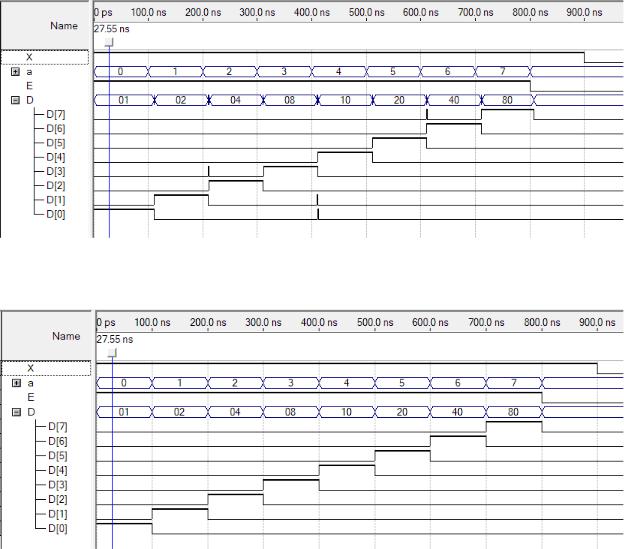

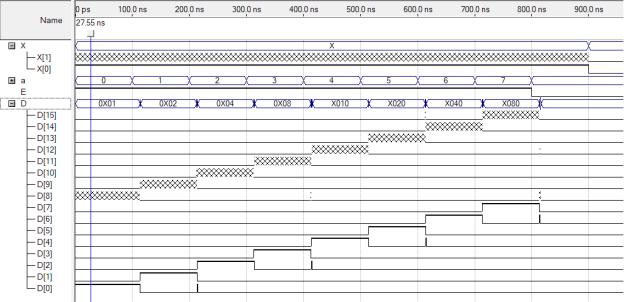

Рисунок 2.2 – Моделирование в режиме Timing

На рисунке 2.3 представлено моделирование демультиплексора 1-8 в

режиме Functional.

Рисунок 2.3 – Моделирование в режиме Functional

По результатам моделирования результат работы собранной схемы соответствует таблице истинности.

2.5 ОПИСАНИЕ С ПОМОЩЬЮ HDL

По варианту используется VHDL.

Ниже приведен код описывающий устройство демультиплексора 1-8: library ieee;

use ieee.std_logic_1164.all;

use IEEE.std_logic_unsigned.all; use IEEE.numeric_std.all;

entity DMX1_8 is port ( X: in std_logic;

a: in std_logic_vector (2 downto 0); E: in std_logic;

D: out std_logic_vector (7 downto 0)); end;

11

architecture sync of DMX1_8 is begin

process (all) begin if E = '1' then

D <= "00000000"; case a is

when "000" => D(0) <= X; when "001" => D(1) <= X; when "010" => D(2) <= X; when "011" => D(3) <= X; when "100" => D(4) <= X; when "101" => D(5) <= X; when "110" => D(6) <= X; when "111" => D(7) <= X;

end case;

else D <= "00000000"; end if;

end process; end;

На рисунке 2.4 представлена схема из RTL Viewer для кода выше.

12

Рисунок 2.4 – RTL Viewer представление

На рисунке 2.5 представлено моделирование в режиме Timing.

13

Рисунок 2.5 – Моделирование в режиме Timing

На рисунке 2.6 представлено моделирование в режиме Functional.

Рисунок 2.6 – Моделирование в режиме Functional

2.6 МАСШТАБИРОВАНИЕ ДЕМУЛЬТИПЛЕКСОРА

По варианту необходимо реализовать работу демультиплексора 2-16 на основе демультиплексора 1-8.

Таблица истинности для демультиплексора 2-16 представлена в таблице 2.2. Таблица 2.2 - демультиплексора 2-16

|

|

Входы |

|

|

|

|

|

|

|

|

|

|

Выходы |

|

|

|

|

|

|

|||||

|

|

|

a |

a |

a |

|

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

D |

||

2 |

1 |

|

2 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

1 |

9 |

|

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

5 |

4 |

3 |

2 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

b |

b |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b |

|||

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

2 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

b |

b |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

b |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b |

0 |

||

2 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

2 |

|

2 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

1 |

|

b |

b |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

b |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

b |

0 |

0 |

|

3 |

3 |

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

3 |

|

|

2 |

1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

b |

b |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

b |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b |

0 |

0 |

0 |

4 |

4 |

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

4 |

|

|

|

2 |

1 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

|

|

|

b |

b |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

b |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b |

0 |

0 |

0 |

0 |

5 |

5 |

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

5 |

|

|

|

|

2 |

1 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

|

|

|

|

b |

b |

1 |

0 |

1 |

1 |

0 |

0 |

b |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b |

0 |

0 |

0 |

0 |

0 |

6 |

6 |

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

6 |

|

|

|

|

|

2 |

1 |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

b |

b |

1 |

1 |

0 |

1 |

0 |

b |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b |

0 |

0 |

0 |

0 |

0 |

0 |

7 |

7 |

|

|

|

|

|

7 |

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

2 |

1 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

b |

b |

1 |

1 |

1 |

1 |

b |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

b |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

8 |

8 |

|

|

|

|

8 |

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

|

2 |

1 |

|

|

|

|

1 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

x |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

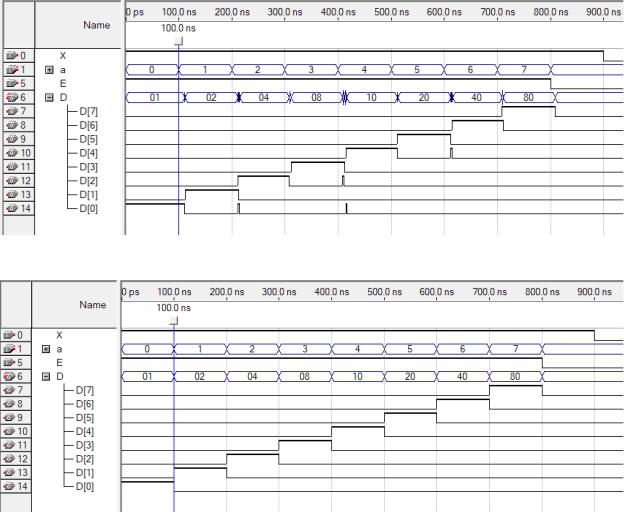

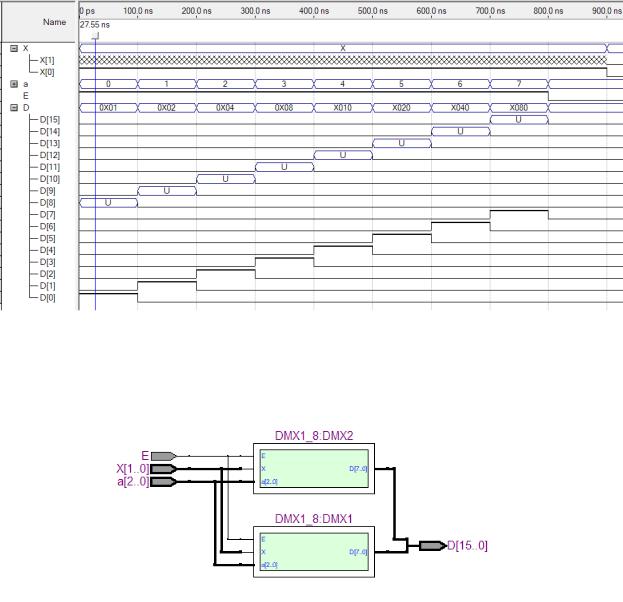

В соответствии таблицей истинности на основе демультиплексора 1-8 была разработана схема демультиплексора 2-16. Функциональная схема масштабированного демультиплексора 2-16 приведена на рисунке 2.7

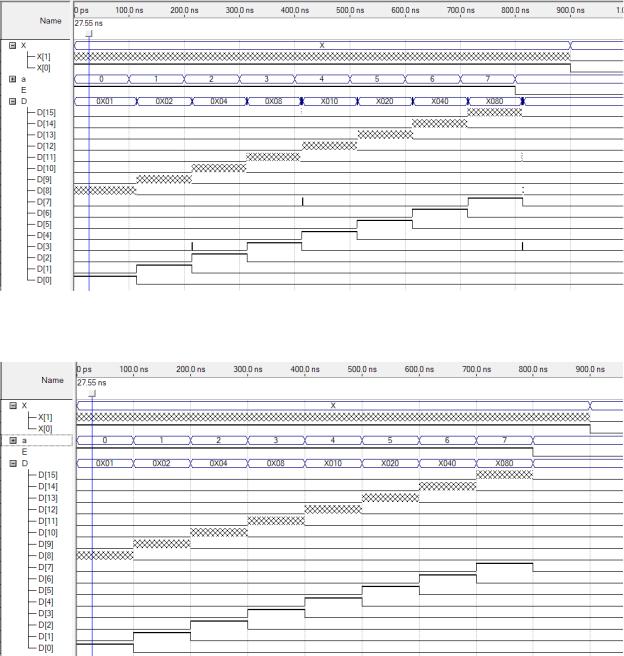

Рисунок 2.7 – Функциональная схема демультиплексора 2-16 На рисунке 2.8 представлено моделирование демультиплексора 2-16 в

режиме Timing.

15

Рисунок 2.8 – Моделирование в режиме Timing

На рисунке 2.9 представлено моделирование демультиплексора 2-16 в

режиме Functional.

Рисунок 2.9 – Моделирование в режиме Functional

По результатам моделирования видно, что работа схемы соответствует таблице истинности 2.2.

С помощью VHDL также была описана схема демультиплексора 2-16 с использованием масштабирования. За основу взят демультиплексор 1-8, описанный в пункте 2.5.

library ieee;

use ieee.std_logic_1164.all;

use IEEE.std_logic_unsigned.all; use IEEE.numeric_std.all;

entity DMX2_16 is

port ( X: in std_logic_vector (1 downto 0); a: in std_logic_vector (2 downto 0);

16

E: in std_logic;

D:out std_logic_vector (15 downto 0)); end;

architecture sync of DMX2_16 is component DMX1_8

port (X: in std_logic;

a: in std_logic_vector (2 downto 0);

E:in std_logic;

D: out std_logic_vector (7 downto 0)); end component;

begin

DMX1: DMX1_8

port map(X(0), a(2 downto 0), E, D(7 downto 0)); DMX2: DMX1_8

port map(X(1), a(2 downto 0), E, D(15 downto 8)); end;

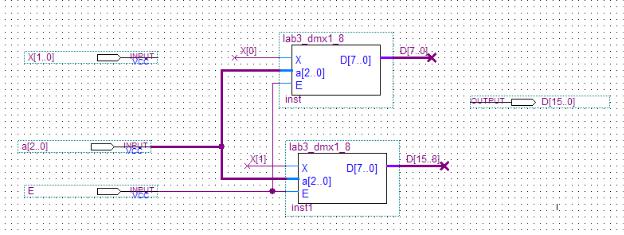

Результат моделирования демультиплексора 2-16 описанный с помощью VHDL в режиме Timing представлен на рисунке 2.10.

Рисунок 2.10 – Моделирование в режиме Timing

На рисунке 2.11 представлен результат моделирования в режиме

Functional.

17

Рисунок 2.11 – Моделирование в режиме Functional

По результатам моделирования видно, что работа схемы соответствует таблице истинности 2.2.

На рисунке 2.12 представлена схема из RTL Viewer для кода, описывающего демультиплексора 2-16.

Рисунок 2.12 – RTL Viewer представление

18

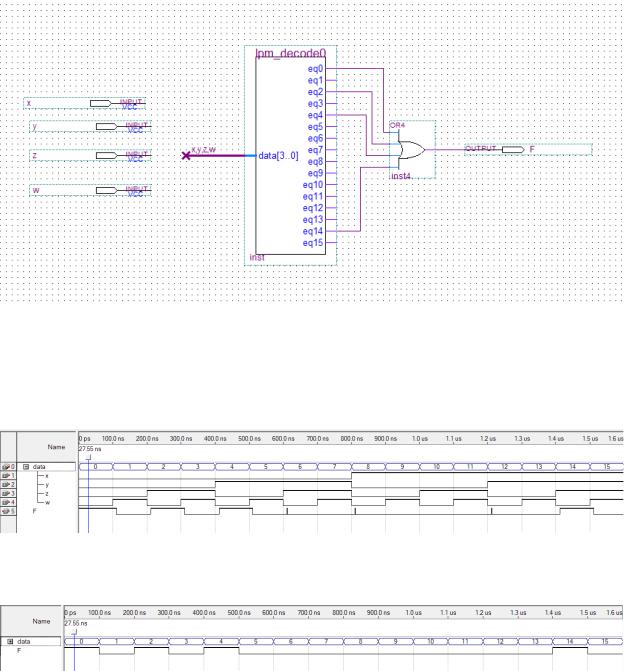

3. РЕАЛИЗАЦИЯ ФУНКЦИИ НА ОСНОВЕ ДЕШИФРАТОРА

3.1 ТАБЛИЦА ИСТИННОСТИ

По варианту необходимо реализовать функцию с помощью мультиплексора и дешифратора следующую функцию:

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

=

Таблица 3.1 отражает таблицу истинности для заданной функции. Таблица 3.1 – Таблица истинности для функции .

|

Входы |

|

|

Выходы |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

|

|

|

|

|

|

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

3.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

Дешифратор выдает унитарный код, то есть одну единицу на выходе. Тогда пусть набор , , , будет составлять входы дешифратора, означающие позицию выхода активного сигнала на выходе. Из таблицы истинности 3.1 узнаем какие позиции на дешифраторе необходимо учитывать, чтобы с использованием логического устройства ИЛИ, устройство с помощью дешифратора выдавала правильный результат по формуле.

На рисунке 3.1 представлена функциональная схема дешифратора, реализующего функцию .

19

Рисунок 3.1 – Функциональная схема устройства

3.3 РЕЗУЛЬТАТ МОДЕЛИРОВАНИЯ СХЕМЫ

На рисунке 3.2 представлено моделирование устройства в режиме

Timing.

Рисунок 3.2 – Моделирование в режиме Timing

На рисунке 3.3 представлено моделирование устройства в режиме

Functional.

Рисунок 3.3 – Моделирование в режиме Functional

По результатам моделирования результат работы собранной схемы соответствует таблице истинности устройства .

20