Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

РАЗРАБОТКА ВЫЧИСЛИТЕЛЬНОГО БЛОКА

Отчет по лабораторной работе №8 по дисциплине «Электроника и схемотехника 2»

Вариант №19

Студент гр.

Руководитель

Томск 2022

Введение

Цель работы – научиться совместно применять устройства средней степени интеграции.

Постановка задачи:

1. Разработать обобщенную функциональную схему устройства.

2. Описать составные части схемы.

3. Составить таблицы функционирования оперативного блока.

4. Промоделировать работу схемы в двух режимах.

5. Описать устройство с помощью System Verilog.

Вариант – 19.

1 ВЫЧИСЛИТЕЛЬНЫЙ БЛОК

1.1 ОБОБЩЕННАЯ ФУНКЦИОНАЛЬНАЯ СХЕМА

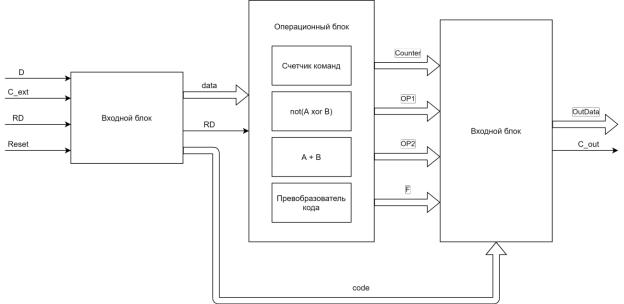

На рисунке 1 представлена обобщённая функциональная схема устройства.

Рисунок 1 – Обобщённая функциональная схема

1.2 ТАБЛИЦЫ ФУНКЦИОНИРОВАНИЯ

Ниже представлена таблица 1, показывает функционирование схемы кодирования двоичного числа в в Commodore GCR-код. Схема работает при КОП-01.

Таблица 1 – Таблица функционирования.

|

|

Входы |

|

|

|

Выходы |

|

|

||

x3 |

x2 |

|

x1 |

x0 |

y4 |

y3 |

y2 |

|

y1 |

y0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

|

0 |

1 |

|

1 |

|

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

0 |

|

1 |

|

0 |

1 |

|

1 |

1 |

1 |

0 |

1 |

|

1 |

|

1 |

|

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

1 |

|

1 |

|

1 |

0 |

|

1 |

1 |

1 |

1 |

0 |

|

1 |

|

1 |

|

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

|

0 |

|

1 |

|

1 |

1 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

|

Ниже представлена таблица 2, которая показывает функционирование |

|||||||||||

|

|

|

|

|

|

|

|

̅̅̅̅̅̅̅̅ |

|

|

|

|

схемы выполняющие логическую операцию . |

|

|

|

|

||||||||

Таблица 2 – Таблица функционирования схемы |

|

|

|

|

||||||||

|

|

|

|

|

Входы |

|

|

|

Выходы |

|

||

А2 |

|

А1 |

|

А0 |

|

В2 |

В1 |

В0 |

Q2 |

Q1 |

|

Q0 |

|

1 |

|

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

|

1 |

|

1 |

1 |

|

0 |

0 |

1 |

0 |

0 |

|

1 |

|

1 |

|

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

0 |

|

1 |

|

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

|

1 |

|

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

0 |

|

1 |

|

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

|

1 |

|

1 |

1 |

|

1 |

1 |

0 |

1 |

1 |

|

0 |

|

1 |

|

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

|

1 |

|

0 |

|

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

|

0 |

|

0 |

|

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

|

0 |

|

0 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

0 |

|

0 |

|

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

|

0 |

|

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

|

0 |

|

0 |

|

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

|

0 |

|

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

|

0 |

|

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

|

1 |

|

0 |

|

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

|

0 |

|

0 |

|

0 |

1 |

|

1 |

1 |

1 |

0 |

0 |

|

1 |

|

0 |

|

1 |

0 |

|

1 |

1 |

1 |

0 |

1 |

|

0 |

|

0 |

|

1 |

1 |

|

1 |

1 |

1 |

0 |

1 |

|

1 |

|

1 |

|

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

|

0 |

|

1 |

|

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

|

1 |

|

1 |

|

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

0 |

|

1 |

|

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

|

1 |

|

1 |

|

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

|

1 |

|

1 |

0 |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

|

1 |

|

0 |

1 |

|

0 |

0 |

0 |

0 |

1 |

|

0 |

|

1 |

|

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

|

1 |

|

0 |

|

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

|

0 |

|

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

1 |

|

0 |

|

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

0 |

|

0 |

|

0 |

|

|

1 |

1 |

1 |

|

||

|

|

Ниже представлена таблица 3 отражающая функционирование |

|||||||||||||||||||

сумматора. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Таблица 3 – Таблица функционирования сумматора |

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

A + B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

|

Выходы |

|

|

|

|

|

||||

|

D5 |

|

|

D4 |

|

|

D3 |

D2 |

D1 |

D0 |

Q4 |

|

Q3 |

|

Q2 |

Q1 |

|

||||

|

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

0 |

|

|

0 |

|

0 |

0 |

|

||||

|

0 |

|

0 |

|

0 |

0 |

0 |

1 |

|

0 |

|

|

0 |

|

0 |

1 |

|

||||

|

0 |

|

0 |

|

0 |

0 |

1 |

0 |

|

0 |

|

|

0 |

|

1 |

0 |

|

||||

|

0 |

|

0 |

|

0 |

0 |

1 |

1 |

|

0 |

|

|

0 |

|

1 |

1 |

|

||||

|

0 |

|

0 |

|

0 |

1 |

0 |

0 |

|

0 |

|

|

1 |

|

0 |

0 |

|

||||

|

0 |

|

0 |

|

0 |

1 |

0 |

1 |

|

0 |

|

|

1 |

|

0 |

1 |

|

||||

|

0 |

|

0 |

|

0 |

1 |

1 |

0 |

|

0 |

|

|

1 |

|

1 |

0 |

|

||||

|

0 |

|

0 |

|

0 |

1 |

1 |

1 |

|

0 |

|

|

1 |

|

1 |

1 |

|

||||

|

0 |

|

0 |

|

1 |

0 |

0 |

0 |

|

0 |

|

|

0 |

|

0 |

1 |

|

||||

|

0 |

|

0 |

|

1 |

0 |

0 |

1 |

|

0 |

|

|

0 |

|

1 |

0 |

|

||||

|

0 |

|

0 |

|

1 |

0 |

1 |

0 |

|

0 |

|

|

0 |

|

1 |

1 |

|

||||

|

0 |

|

0 |

|

1 |

0 |

1 |

1 |

|

0 |

|

|

1 |

|

0 |

0 |

|

||||

|

0 |

|

0 |

|

1 |

1 |

0 |

0 |

|

0 |

|

|

1 |

|

0 |

1 |

|

||||

|

0 |

|

0 |

|

1 |

1 |

0 |

1 |

|

0 |

|

|

1 |

|

1 |

0 |

|

||||

|

0 |

|

0 |

|

1 |

1 |

1 |

0 |

|

0 |

|

|

1 |

|

1 |

1 |

|

||||

|

0 |

|

0 |

|

1 |

1 |

1 |

1 |

|

1 |

|

|

0 |

|

0 |

0 |

|

||||

|

0 |

|

1 |

|

0 |

0 |

0 |

0 |

|

0 |

|

|

0 |

|

1 |

0 |

|

||||

|

0 |

|

1 |

|

0 |

0 |

0 |

1 |

|

0 |

|

|

0 |

|

1 |

1 |

|

||||

|

0 |

|

1 |

|

0 |

0 |

1 |

0 |

|

0 |

|

|

1 |

|

0 |

0 |

|

||||

|

0 |

|

1 |

|

0 |

0 |

1 |

1 |

|

0 |

|

|

1 |

|

0 |

1 |

|

||||

|

0 |

|

1 |

|

0 |

1 |

0 |

0 |

|

0 |

|

|

1 |

|

1 |

0 |

|

||||

|

0 |

|

1 |

|

0 |

1 |

0 |

1 |

|

0 |

|

|

1 |

|

1 |

1 |

|

||||

|

0 |

|

1 |

|

0 |

1 |

1 |

0 |

|

1 |

|

|

0 |

|

0 |

0 |

|

||||

|

0 |

|

1 |

|

0 |

1 |

1 |

1 |

|

1 |

|

|

0 |

|

0 |

1 |

|

||||

|

0 |

|

1 |

|

1 |

0 |

0 |

0 |

|

0 |

|

|

0 |

|

1 |

1 |

|

||||

|

0 |

|

1 |

|

1 |

0 |

0 |

1 |

|

0 |

|

|

1 |

|

0 |

0 |

|

||||

|

0 |

|

1 |

|

1 |

0 |

1 |

0 |

|

0 |

|

|

1 |

|

0 |

1 |

|

||||

|

0 |

|

1 |

|

1 |

0 |

1 |

1 |

|

0 |

|

|

1 |

|

1 |

0 |

|

||||

|

0 |

|

1 |

|

1 |

1 |

0 |

0 |

|

0 |

|

|

1 |

|

1 |

1 |

|

||||

|

0 |

|

1 |

|

1 |

1 |

0 |

1 |

|

1 |

|

|

0 |

|

0 |

0 |

|

||||

|

0 |

|

1 |

|

1 |

1 |

1 |

0 |

|

1 |

|

|

0 |

|

0 |

1 |

|

||||

|

0 |

|

1 |

|

1 |

1 |

1 |

1 |

|

1 |

|

|

0 |

|

1 |

0 |

|

||||

|

1 |

|

0 |

|

0 |

0 |

0 |

0 |

|

0 |

|

|

1 |

|

0 |

0 |

|

||||

|

1 |

|

0 |

|

0 |

0 |

0 |

1 |

|

0 |

|

|

1 |

|

0 |

1 |

|

||||

|

1 |

|

0 |

|

0 |

0 |

1 |

0 |

|

0 |

|

|

1 |

|

1 |

0 |

|

||||

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1.3 ФУНКЦИОНАЛЬНАЯ СХЕМА

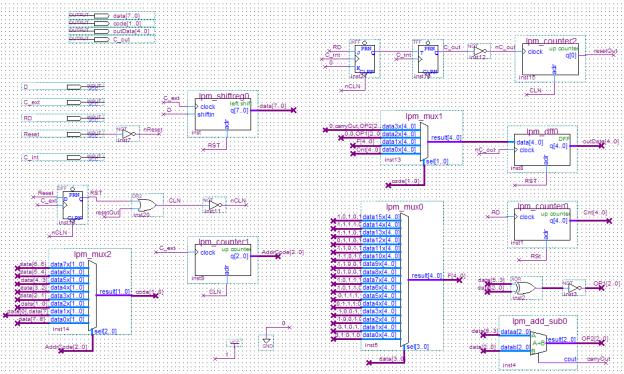

На рисунке 2 представлена полная функциональная схема

вычислительного блока.

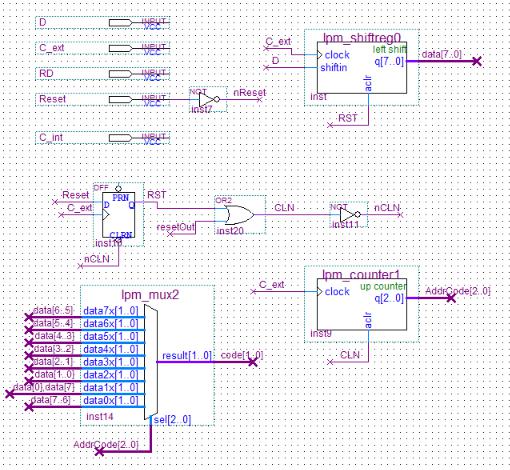

Рисунок 2 – Функциональная схема На рисунке 3 представлена подробно описанная входная часть

функциональной схемы. Данные записываются в регистр последовательно по входу D. Счетчик считает количество поступивших на вход сигналов, для определения номера входов, в которых записан КОП.

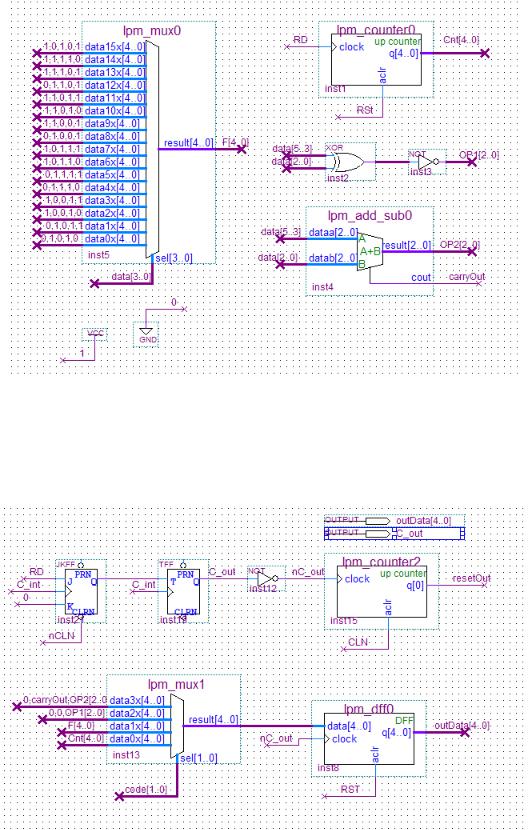

Рисунок 3 – Функциональная схема входной части На рисунке 4 представлен операционный блок функциональной схемы.

Операционный блок включает в себя кодировке двоичного кода, счетчик команд, логическую и арифметическую операции над входными данными.

Рисунок 4 – Операционный блок На рисунке 5 представлена выходная часть функциональной схемы. В

выходной части формируется сигнал C_out и подается результат операционного блока на выход схемы.

Рисунок 5 – Выходная часть функциональной схемы

1.4МОДЕЛИРОВАНИЕ

Втаблице 4 представлен план моделирования для вычислительного

блока.

Таблица 4 – План моделирования

|

|

|

|

|

Входы |

|

|

|

|

|

Выходы |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

№ |

КОП |

|

|

|

|

Данные |

|

Сброс |

|

|

|

|

|

|

|||

Сигнала |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

C0 |

D5 |

D4 |

|

D3 |

|

D2 |

D1 |

D0 |

R |

Q4 |

Q3 |

Q2 |

Q1 |

|

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

1 |

0 |

1 |

X |

X |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

|

0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

0 |

1 |

X |

X |

|

1 |

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

1 |

0 |

1 |

0 |

|

1 |

|

1 |

1 |

1 |

0 |

- |

- |

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

1 |

0 |

0 |

1 |

|

0 |

|

1 |

0 |

0 |

0 |

- |

- |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

1 |

1 |

1 |

1 |

|

0 |

|

1 |

1 |

0 |

0 |

- |

1 |

1 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

1 |

1 |

0 |

0 |

|

0 |

|

1 |

1 |

1 |

0 |

- |

0 |

1 |

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

7 |

0 |

0 |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

1 |

1 |

|

1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

8 |

X |

X |

X |

X |

X |

X |

X |

X |

1 |

0 |

0 |

0 |

0 |

|

0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

9 |

0 |

0 |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

|

1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

На рисунке 6 представлен результат моделирования функциональной схемы в режиме Timing. В промежуток 0-720нс промоделирована работа первого сигнала, 760-1460нс – второго, 1480-2310нс – третьего, 2320-3160нс – четвертого, 3160-3990нс – пятого, 4040-4850нс – шестого, 4920-5240нс – седьмого, 5400-5480 нс – восьмого и 5560-6000нс – девятого.

Рисунок 6 – Моделирование функционального блока в режиме Timing

На рисунке 7 представлен результат моделирования функциональной схемы в режиме Timing.