Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

РАЗРАБОТКА ВЫЧИСЛИТЕЛЬНОГО БЛОКА

Отчет по лабораторной работе №8 по дисциплине «Электроника и схемотехника»

Вариант № 12

Студент гр.

..2022

Руководитель

== кафедры КИБЭВС _______

====2022

Томск 2022

ВВЕДЕНИЕ

Цель работы − овладеть навыками совместного применения устройств

средней степени интеграции.

В ходе данной лабораторной работы требуется выполнить следующие

задачи:

1.Разработать обобщённую функциональную схему устройства и описать составные части схемы.

2.Составить таблицы функционирования операционного блока.

Логическая операция:

̅

Арифметическая операция:

− + 1

3.Организовать приём и выдачу данных согласно варианту для выполнения 4-х операций, используя встроенные блоки регистров и счётчиков.

4.Создать схему реализации вычислительного блока, выполняющего заданные операции и осуществляющего приём входных данных и выдачу результата согласно варианту.

5.Составить план моделирования. Использовать для каждой операции по два различных набора данных.

6.Промоделировать работу схемы в двух режимах (timing и functional).

Сравнить результаты моделирования с составленным планом моделирования. 7. Используя заданный вариантом HDL, описать и промоделировать то

же устройство. Вариант HDL: VHDL.

2

1.ВЫЧИСЛИТЕЛЬ ФУНКЦИИ

1.1Обобщенная функциональная схема

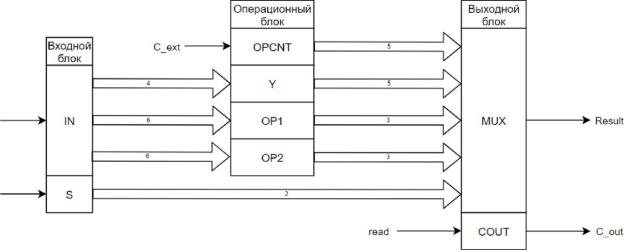

На рис. 1.1 представлена обобщенная функциональная схема.

Рисунок 1.1 - Функциональная схема

Устройство получает на вход 6-разрядный код x, должно выполнять четыре операции и выводить результат одного из них по линии result в

зависимости от кода операции S. При подаче активного уровня сигнала read

вырабатываются сигналы C_out, количество которых зависит от длины result. IN - хранение входных данных.

S - хранение кода операции.

OPCNT - счётчик операций.

Y - кодирование двоичного числа.

OP1 - логическая операция.

OP2 - арифметическая операция.

MUX - мультиплексирование выходных данных.

COUT - выработка выходного синхросигнала.

1.2Таблица истинности

Втаблице 2.1 представлена таблица функционирования кодирования двоичного числа в IBM GCR-код.

3

Таблица 2.1 - Таблица функционирования IBM GCR

Код операции |

|

Входы |

|

|

|

Выходы |

|

|

||||

X3 |

X2 |

X1 |

X0 |

Y4 |

Y3 |

|

Y2 |

|

Y1 |

Y0 |

||

|

|

|

|

|||||||||

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

0 |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

|

1 |

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

|

1 |

|

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

|

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

|

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

|

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

1 |

|

1 |

1 |

Втаблице 2.2 представлена таблица истинности логической операции

̅.

Таблица 2.2 - Таблица истинности логической операции

Код операции |

|

|

Входы |

|

|

|

Выходы |

||||

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

OP1.2 |

OP1.1 |

OP1.0 |

|||

|

|

||||||||||

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

4 |

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

|

|

|

|

|

5 |

|

|

|

|

|

1 |

0 |

|

1 |

1 |

0 |

|

1 |

|

1 |

|

0 |

|

1 |

1 |

1 |

1 |

0 |

|

1 |

1 |

0 |

|

1 |

|

1 |

|

1 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

|

0 |

|

0 |

|

0 |

|

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

|

0 |

|

0 |

|

1 |

|

0 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

|

0 |

|

1 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

|

0 |

|

1 |

|

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

|

0 |

|

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

|

0 |

|

1 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

|

1 |

|

0 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

|

1 |

|

1 |

|

1 |

1 |

1 |

В |

таблице |

2.3 |

представлена |

таблица |

|

истинности |

арифметической |

||||||||

операции − + 1.

Таблица 2.3 - Таблица истинности арифметической операции

Код операции |

|

|

Входы |

|

|

|

Выходы |

|

||||

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

OP1.2 |

|

OP1.1 |

|

OP1.0 |

||

|

|

|

|

|||||||||

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

1 |

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

|

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

|

1 |

|

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

|

0 |

|

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

|

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

0 |

|

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

|

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

|

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

0 |

|

0 |

|

|

|

|

|

6 |

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

|

|

|

|

|

7 |

|

|

|

|

|

1.3Функциональная схема

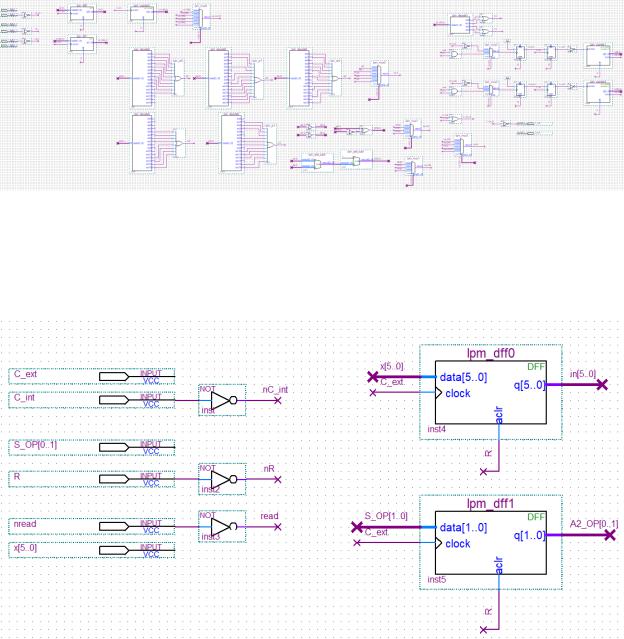

На рисунке 3.1 представлена функциональная схема из САПР QuartusII.

Рисунок 3.1 - Функциональная схема На рис. 3.2 представлен входной блок схемы. В регистры по переднему

фронту внешнего синхросигнала C_ext сохраняются входные данные x,

данные для выполнения операции, и S_OP, код операции.

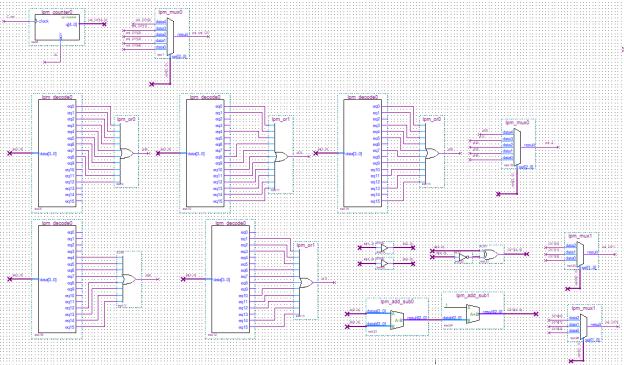

Рисунок 3.2 - Входной блок На рис. 3.3 представлен операционный блок схемы. Счетчик по

переднему фронту C_ext считает количество операций. С помощью дешифраторов выполняется задача кодирования двоичного числа в IBM GCR-

код. Элементы xor и not выполняют логическую операцию, а add_sub -

арифметическую. При этом выходы всех этих элементов параллельные. Их

8

преобразование в последовательный код выполняется четырьмя мультиплексорами.

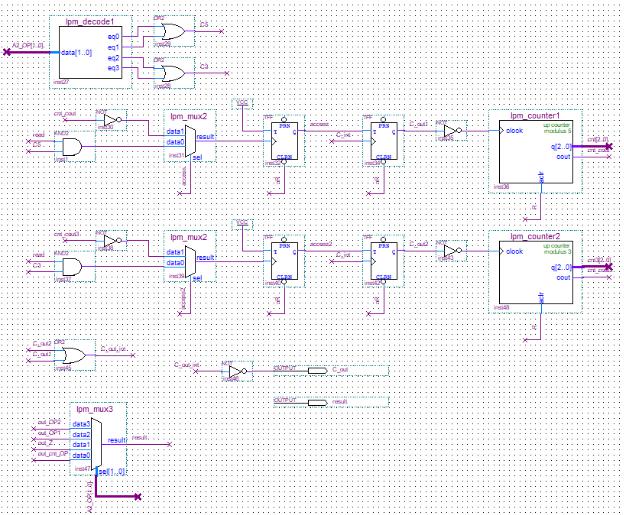

Рисунок 3.3 - Операционный блок На рис. 3.4 представлен выходной блок схемы.

Есть два блока с C_out. С помощью мультиплексоров, триггеров и счетчиков при подаче сигнала read формируется выход C_out1 или C_out2.

Первый в количестве 5 штук, а второй - 3. Дешифратор используется в роли мультиплексора, т.е. выбирает, какой из блоков привести в действие.

Мультиплексором inst47 выбирается какой результат выводить.

9

Рисунок 3.4 - Выходной блок

1.4Моделирование

Втаблице 4.1 представлен план моделирования.

Таблица 4.1 - План моделирования

|

|

|

|

Входы |

|

|

|

|

|

|

Выходы |

|

|||

№ |

|

Код |

|

A |

|

|

B |

|

R |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

Сигнала |

операции |

X5 |

X4 |

X3 |

X2 |

X1 |

X0 |

|

|

|

|

|

|

||

1 |

0 |

|

1 |

- |

- |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

2 |

0 |

|

1 |

- |

- |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

3 |

1 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

- |

- |

1 |

0 |

0 |

4 |

1 |

|

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

- |

- |

0 |

1 |

0 |

5 |

1 |

|

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

- |

- |

1 |

1 |

0 |

6 |

1 |

|

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

- |

- |

1 |

0 |

1 |

7 |

0 |

|

0 |

- |

- |

- |

- |

- |

- |

0 |

0 |

0 |

1 |

1 |

1 |

8 |

x |

|

x |

- |

- |

- |

- |

- |

- |

1 |

0 |

0 |

0 |

0 |

0 |

9 |

0 |

|

0 |

- |

- |

- |

- |

- |

- |

0 |

0 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|

|