- •Редакционная коллегия:

- •Введение

- •Выполнение алгоритмов цифровой обработки сигналов в базисе программируемых логических интегральных схем

- •Е.А. Азарова анализ лазерных устройств хранения информации

- •Параметры синтезируемых процессорных ip-модулей

- •Исправляющая способность кода Рида-Маллера

- •Преимущества и недостатки кодов

- •О.Ю. Макаров, д.А. Кабанов

- •Д.А. Кабанов

- •Р.Р. Абулханов, и.И. Застрожнов, о.Ю. Макаров

- •Р.Р. Абулханов, и.И. Застрожнов

- •Р.Р. Абулханов, и.И. Застрожнов

- •Р.Р. Абулханов

- •Р.Р. Абулханов

Выполнение алгоритмов цифровой обработки сигналов в базисе программируемых логических интегральных схем

Программируемые логические интегральные схемы (ПЛИС) сделали взрыв в технике реализации алгоритмов ЦОС. Самые простые и давно сделанные архитектуры ПЛИС – SPLD и CPLD (Simple и Complex Programmable Logic Device). В них можно создавать схемы соединений, в эквиваленте 10–100 корпусам ТТЛ-логики стандартных серий. На самых простых ПЛИС современные сложные алгоритмы реализовать не получится, в связи с этим их основное использование в схемах интерфейса. А вот для самых сложных задач наиболее подходящими являются ПЛИС с FPGA-архитектурой. Существует 2-а класса описанной архитектуры – крупно- и мелкомодульный. ПЛИС с крупномодульной архитектурой имеет в себя крупные логические блоки с таблицами перекодировки и перепрограммируемыми внутриблочными соединениями. ПЛИС с мелкомодульной (мелкозернистой) архитектурой включают в себя множество относительно простых блоков. Плюсы крупномодульной технологии – хорошая производительность. Для мелкомодульной архитектуры особенно достаточно большая гибкость при имплементации схем и работе в систолических структурах.

В новейших разработках идет тенденция вытеснения ИС малой и средней степени интеграции ПЛИС. Использование ПЛИС в средствах ЦОС обуславливается их высоким быстродействием (тактовые частоты – до 250 –300 МГц), а также возможностью выполнения достаточно сложных параллельных алгоритмов. А так же совместимость различных типов ПЛИС при переносе проектных решений описанных на языках описания аппаратуры (VHDL, AHDL, Verilog и др.). Существуют библиотеки мегафункций, позволяющие реализовывать сложнейшие алгоритмы. Имеются САПР, в которых проводится полное моделирование разрабатываемых устройств, а также программирование или изменение конфигурации ПЛИС прямо в системе. Архитектурные особенности: ПЛИС хорошо подходят для операций умножения, свертки и других [6,7].

Большое количество алгоритмов ЦОС, в частности алгоритмы фильтрации, выполняют в виде устройств с конечной импульсной характеристикой (КИХ). В ПЛИС таких семейств как FLEX 6000, FLEX8000 и FLEX10K фирмы Altera можно создавать быстродействующие КИХ-структуры высокого порядка.

Разработчики понимают необходимость создания библиотек параметризируемых мегафункций многих устройств, особенно систем ЦОС. Определенные шаги в этом направлении предпринимает фирма Altera. Так, в августе 1995 г. стартовала ее программа поддержки партнеров – разработчиков мегафункций (AMPP, Altera Megafunction Partners Program).

Проанализировав номенклатуру мегафункций, выпущенных в рамках программы, можно сказать, что вопросам ЦОС и, в частности, фильтрации, в ней уделяется недостаточное внимание. Так, из 18 партнеров AMPP не более четверти представили готовые продукты или заявили о ведущихся разработках в этой области. Основную массу составляют мегафункции стандартных микропроцессоров и микроконтроллеров, устройств обслуживания шинных магистралей (ISA, PCI), сетевых контроллеров и т.д. Типичные предложения средств ЦОС – мегафункции, реализующие быстрые преобразования Фурье и КИХ-фильтры. Например, фирма Vendor объявила о реализации медианного фильтра и фильтра с бесконечной импульсной характеристикой (БИХ). Лидер в области разработок мегафункций ЦОС – фирма Integrated Silicon Systems (ISS) – создала библиотеки мегафункций БИХ-фильтров, фильтров обработки изображений, медианных фильтров. Разработаны также мегафункции, реализующие некоторые алгоритмы адаптивной обработки. Однако до сих пор нет предложений в области нелинейных, оптимальных и большинства типов адаптивных структур, не реализованы давно известные алгоритмы последователностной фильтрации.

Литература

1. Гоноровский И.С. Радиотехнические цепи и сигналы. 1986.

2. Залмазон Л.А. Преобразования Фурье, Уолша, Хаара и их применение в управлении, связи и др. областях. 1989.

3. Марил С.Л. Цифровой спектральный анализ и его приложения. 1990.

4. Мальцева О.К. Основы цифровой техники. 1986.

5. Солодовников А.И., Спиваковский А.М. Основы теории и методы спектральной обработки информации. 1986.

6. Гольдберг Л.М., Матюшкин Б.Д., Поляк М.Н. Цифровая обработка сигналов. 1985.

7. Хемминг Р.В. Цифровые фильтры. 1987.

Воронежский государственный технический университет

УДК 681.3

П.С. Крайнюченко, Л.Н. Никитин

АНАЛИЗАТОР ДОСТОВЕРНОСТИ ЗВУКОВОЙ ИНФОРМАЦИИ

В работе представлена структурная схема и краткое описание функционирования данного прибора. Уделено внимание микроколебаниям, присутствующим в человеческой речи. Представлены некоторые формы сигнала, снятые с определенных участков цепи устройства. Сфера использования и предложения по применению

В настоящее время для анализа различных видов информации с успехом используется радиоэлектронная аппаратура. Представленное нами ниже позволяет создать комплекс средств для анализа достоверности звуковых явлений. Кроме того, в настоящее время производить анализ достоверности информации требуется не только в специальных учреждениях, но даже в отделах кадров, в государственных и частных предприятиях. Как владельцу, директору фирмы проверить надежность сотрудника или порядочность партнера по бизнесу, не привлекая при этом лишнего внимания? В подавляющем большинстве жизненных ситуаций традиционный детектор лжи - полиграф применить невозможно. В основе его работы лежит одновременное измерение четырех важнейших физиологических характеристик давления крови, пульса, грудного и брюшного дыхания, а также кожно-гальванической реакции. Но при возбуждении или волнении меняется также частотный диапазон звуков речи [1].

Анализатор звука. Естественно, речь в данном случае пойдет не о спектроанализаторе всего звукового диапазона, а об его упрощенной версии, используемой только для определенного узкого диапазона частот.

Основной частотный диапазон звуков человеческой речи заключен в пределах от 90 до 2000 Гц, и в обычных ситуациях этот звук промодулирован микровибрациями частотой от 8 до 12 Гц. Последние, как правило, маскируются другими составляющими, однако, эти микровибрации могут быть выявлены электронным путем и измерены.

В соответствии с теорией, когда человек попадает в стрессовую ситуацию, микровибрации значительно уменьшаются. Нервная система подготавливает тело к действиям в опасной ситуации: зрачки расширяются, конечности усиленно снабжаются кровью, мышцы напрягаются. А поскольку голосовые связки состоят в основном из мышц, они также напрягаются, и упомянутые выше микровибрации (тремоло) вообще прекращаются, или же их амплитуда значительно уменьшается. Поэтому, если обнаруживается изменение микровибраций, можно считать, что человек находится в состоянии стресса. Но, как уже известно, состояние стресса не эквивалентно лжи! Посмотрим на спектральное разложение волны нормального человеческого голоса (слабый стресс), показанного на рис. 1 [2].

Рис. 1. Спектральное разложение волны нормального

человеческого голоса

Структурная схема портативного звукового анализатора приведена на рис. 2, а форма сигнала в некоторых точках схемы на рис. 3.

Рис. 2. Структурная схема звукового анализатора

По сравнению с речью в обычном состоянии, во входном сигнале (UM2 на рис. 3) видны более близко расположенные пики средней амплитуды. Они играют основную роль в дальнейшем. Поступающий на вход сложный сигнал после усиления подается на фильтр нижних частот. Частота среза 150 Гц. Как видно, полоса все более и более ограничивается окрестностью микровибраций. Выход этого каскада управляет триггером Шмитта, на выходе которого получаются, естественно, прямоугольные импульсы (UB на рис. 3). Они проходят через фильтр нижних частот 20 Гц, за которым следует полосовой фильтр от 10 до 12 Гц. То, что будет на его выходе, зависит от наличия или отсутствия микровибраций. После последнего фильтра сигналы усредняются с помощью двухполупериодного выпрямителя и интегрирующего каскада. В том случае, когда микровибрации плотно следуют друг за другом, получающееся из них усредненное постоянное напряжение будет превышать заранее установленный порог, и начинают светиться в определенном порядке светодиоды блока сигнализации.

Рис. 3. Форма сигнала в некоторых точках схемы

Предложения по использованию. Если к анализатору подключить микрофон, регистрирующий речь, то можно вскоре убедиться на опыте, что большей частью горит зеленый светодиод («Нормально»). Был проанализирован звук телевизионных программ, новостей. Когда говорит диктор, в основном светится зеленый светодиод. Ситуация оказывается такой же во время исполнения актерами ролей (что и понятно, поскольку здесь ложь не сопровождается реакцией страха). При проверке же звука рекламных роликов довольно часто загораются светодиоды, сигнализирующие о неопределенности, и даже довольно часто светится красный светодиод (вероятно, это не случайно?). При этом необходимо учитывать и то обстоятельство, что звукоинженеры на радио и телевидении почти в обязательном порядке используют т.н. фильтры шумов дискретизации, которые отсекают сигналы с частотами ниже 15 Гц, «одурачивая» наш анализатор [3].

Таким образом, можно сказать, что звуковой анализатор стресса - очень интересное устройство, в состав которого входит доступная элементная база, которая не составляет особых проблем при конструировании. Данный прибор может изготавливаться в мелкосерийном и серийном производстве. С ним имеет смысл поработать, т.к. это устройство нового поколения.

Литература

1. Электронные данные-Режим доступа: http//www.ldetector.narod.ru

2. Nagymate C., Reinacs B. Детектор лжи // Радиомир. 2002. № 4. С. 32 - 33.

3. Nagymate C., Reinacs B. Детектор лжи // Радиомир. 2002. № 5. С. 30 - 33.

Воронежский государственный технический университет

УДК 681.3

Д.Ю. Пигловский, А.А. Гришечкин, Л.Н. Никитин

УСТРОЙСТВО ДИСТАНЦИОННОГО МОНИТОРИНГА

ПОДВИЖНЫХ ОБЪЕКТОВ

Данное устройство отличается от базового расширенными функциональными возможностями. Помимо определения координат объекта устройство может контролировать работу и состояние каких-либо датчиков автомобиля (датчик топлива, переключатель «газ-бензин», кнопка поднятия кузова самосвала и т.п.), помимо этого устройство оснащено встроенным аккумулятором, зарядным устройством и акселерометром

В настоящее время в мире существуют различные активно развивающиеся сферы бизнеса. Для своего развития и эффективного решения экономических проблем предприятия стремятся использовать новейшие достижения науки и техники. Например, каждая транспортная компания или организация, имеющая свой автопарк, регулярно сталкивается с проблемой контроля использования служебного транспорта. Соответственно, возникает необходимость сокращения выявленных нецелевых расходов. Данные мероприятия на сегодняшний день носят название «мониторинг транспорта», или, другими словами, реализовывается система слежения за автомобилем. Перед учредителями встает проблема незаконного использования транспорта компании ее сотрудниками, вследствие чего появляется необходимость эффективного решения следующих задач:

- сокращение непредусмотренных расходов без сокращения объемов перевозок;

- оптимизация маршрута транспорта или выявление не запланированного рейса;

- определение местонахождения автомобиля в интервале между посещениями конечных точек маршрута, которые отмечены в накладных;

- доступ к достоверной информации о пробеге транспорта и количестве израсходованного топлива или информации о количестве имеющегося запаса топлива автомобиля в данный момент;

- доступ к достоверной информации, подтверждающей задержку автомобиля ко времени прибытия, по какой-либо причине, например, задержка транспорта в пробке.

Реализация таких подходов в настоящее время возможна путем создания автоматизированных систем мониторинга подвижных объектов. Автоматизированная система мониторинга – это современное решение логистических задач и контроль состояния подвижных объектов в режиме реального времени. Благодаря высокотехнологичному оборудованию система позволяет отслеживать местоположение и состояние подвижных объектов оснащенных бортовым комплектом оборудования из диспетчерского центра, вне зависимости от их местоположения.

Слежение за объектами происходит с помощью глобальной спутниковой системы позиционирования NAVSTAR GPS. Эта система содержит 29 спутников, координаты объектов вычисляются с высокой точностью, а значит в любой момент времени известно точное местоположение каждого из них.

Связь диспетчерского центра с бортовым модулем системы поддерживается через каналы цифровой мобильной сотовой связи GSM. Технология GSM была специально выбрана, так как является наиболее распространенной на территории Российской Федерации.

Автоматизированная система мониторинга подвижных объектов позволяет решить следующие задачи:

- отображение в реальном масштабе времени местоположения подвижного объекта на электронной карте;

- автоматическое слежение за соблюдением водителем каждого подвижного объекта маршрута, графика и режима движения;

- автоматическую регистрацию вхождения подвижного объекта в контролируемую зону и выхода из нее;

- сохранение в базе данных истории перемещения каждого объекта;

- по сигналам установленных датчиков контролировать место и время поднятия кузова самосвала, открывания дверей фургона, поднятия стрелы подъемного крана и т.п., что позволит гарантировать сохранность груза и целевое использование техники;

- позволяет получить информацию о пробеге транспорта и количестве израсходованного топлива или информацию о количестве имеющегося запаса топлива автомобиля в данный момент;

- прогнозирование времени прибытия в конечную точку маршрута и автоматизацию решения логистических задач;

- контроль за соблюдением условий транспортировки груза – температура в рефрижераторе, уровень ударов и вибраций, соблюдение скоростного режима;

- исключает возможность несанкционированного использования автотранспорта и других самоходных машин с выдачей тревожного сообщения диспетчеру.

По мере развития научных и технических средств растёт и актуальность внедрения автоматизированных систем мониторинга в различные сферы бизнеса и предприятия.

Устройства слежения принято называть «трекерами». Ниже приведена структурная схема такого прибора.

За основу было взято базовое устройство, в которое входили следующие блоки: Активная GPS антенна, мобильная GSM антенна, модуль GPS, модуль GSM, преобразователь уровней и схема питания. В качестве активной GPS антенны применена стандартная GPS антенна наружного размещения со встроенным малошумящим усилителем.

Структурная схема трекера

Также в качестве GSM антенны применена стандартная выносная мобильная антенна с коэффициентом усиления 14 Дб. Используемый модуль GPS представляет собой 12-канальный GPS приёмник фирмы Trimble и является одной из последних разработок данной фирмы. Этот приёмник гражданского назначения и способен принимать сигналы C/A кода на частоте 1575.42 МГц. GPS приёмник оснащен портами UART интерфейса для связи с другими радиоэлектронными устройствами, в частности с GSM модулем. GSM модуль представляет собой GPRS модем Q24 компании Wavecom. Модем способен работать в диапазоне частот EGSM 900/1800/850/1900 МГц, класс GPRS – 10-ый. Преобразователь уровней реализован на микросхеме ADM 3202 фирмы Analog Devices. Данная микросхема необходима для согласования трекера с компьютером посредством RS-232 интерфейса. Схема коммутации представляет собой микроконтроллер PIC16F876 со схемой его включения. Данный микроконтроллер позволяет контролировать состояния 9-ти датчиков бортовой системы наблюдаемого объекта. Схема питания собрана на микросхеме LM2576, импульсном стабилизаторе напряжения.

Возможности устройства были ограничены только определением местоположения объекта, определение его скорости, временем поездки, времени стоянок. И перед нами возникла задача расширить функциональные возможности трекера. Необходимо было контролировать состояния датчиков, контролировать наличие GSM сети и наличия спутников на небе для получения координат местоположения, умение устройства переходить в режим ожидания при постановке на стоянку наблюдаемого объекта и сохранения своей работоспособности при отключении питании устройства (например, снятие АКБ с автомобиля для его зарядки). И в результате было разработано устройство, удовлетворяющее всем предъявленным требованиям.

В ходе совместной разработки были решены вышеперечисленные проблемы и для их решения применялись действия, описанные ниже.

Для решения проблемы сохранения работоспособности были введены блоки АКБ и схема зарядки этой АКБ. АКБ представляет собой 3 последовательно соединённых никель-кадмиевых аккумулятора общим напряжением 3,6 В. Никель-кадмиевые аккумуляторы были выбраны потому, что они в отличие от литий-ионных сохраняют свою работоспособность при низких температурах окружающей среды. Данные аккумуляторы позволяют сохранять работу устройства при пропадании внешнего напряжения питания до 24 часов. Схема зарядки для данных аккумуляторов реализована на микросхеме MAX1501 фирмы MAXIM. Данное зарядное устройство полностью автоматизировано и при отключении основного питания оно не «тянет» энергию с аккумуляторной батареи, что является важным фактором при питании устройства от внутреннего источника питания.

Акселерометр применён для решения проблемы перевода устройства в дежурный режим при постановке наблюдаемого транспорта на стоянку. Это было реализовано для того, чтобы не разряжать аккумуляторную батарею при постановке на стоянку транспорта. Акселерометр реализован на микросхеме MMA6270Q компании Freescale Semiconductor. Акселерометр позволяет определять изменение скорости объекта, и при его отсутствии через некоторое время переводить прибор в режим ожидания.

Устройство индикации собрано по примитивной схеме управления маломощной нагрузкой, в данном случае светодиодной, при подаче на него управляющего сигнала. При обнаружении необходимого количества спутников для определения координат и собственно само определение местоположения загорается светодиод синего свечения, который мигает с частотой 1 Гц. При пропадании сигнала местоопределения, данный светодиод гаснет. Для индикации наличия GSM сети применён светодиод зелёного свечения. При наличии GSM сети светодиод производит кратковременные вспышки с частотой 1 Гц, при пропадании сети светодиод индицирует постоянным свечением.

Для решения проблемы контроля состояния датчиков был применён блок схемы коммутации датчиков в составе с блоком защиты входных цепей микросхемы.

Подведя итоги можно сделать вывод: была выполнена поставленная задача по расширению функциональных возможностей устройства в целом, что позволило сделать его более конкурентоспособным устройством на рынке устройств дистанционного мониторинга подвижных объектов.

Воронежский государственный технический университет

УДК 681.3

А.В. Анохин, О.Ю. Макаров, А.А. Пирогов

ТехнологиИ DSSS и FHSS в беспроводных сетях

Статья описывает метод прямой последовательности и метод частотных скачков, использующих принцип широкополосной передачи сигнала в беспроводных сетях стандарта 802.11, а также описаны достоинства и недостатки данных методов. Приведены различия в стандартах беспроводных сетей IEEE 802.11

Стандарт 802.11 предусматривает использование двух методов передачи данных. Один из них получил название Direct Sequence Spread Spectrum (DSSS) - «метод прямой последовательности», а другой - Frequency Hopping Spread Spectrum (FHSS) - «метод частотных скачков». Оба эти метода используют принцип широкополосной передачи сигнала.

При потенциальном кодировании информационные биты — логические нули и единицы - передаются прямоугольными импульсами напряжений. Прямоугольный импульс длительности T имеет спектр, ширина которого обратно пропорциональна длительности импульса. Поэтому чем меньше длительность информационного бита, тем больший спектр занимает такой сигнал.

Для преднамеренного уширения спектра первоначально узкополосного сигнала в технологии DSSS в каждый передаваемый информационный бит (логический 0 или 1) в буквальном смысле встраивается последовательность так называемых чипов. Если информационные биты - логические нули или единицы - при потенциальном кодировании информации можно представить в виде последовательности прямоугольных импульсов, то каждый отдельный чип - это тоже прямоугольный импульс, но его длительность в несколько раз меньше длительности информационного бита. Последовательность чипов представляет собой последовательность прямоугольных импульсов, то есть нулей и единиц, однако эти нули и единицы не являются информационными. Поскольку длительность одного чипа в n раз меньше длительности информационного бита, то и ширина спектра преобразованного сигнала будет в n-раз больше ширины спектра первоначального сигнала. При этом и амплитуда передаваемого сигнала уменьшится в n раз.

Чиповые последовательности, встраиваемые в информационные биты, называют шумоподобными кодами (PN-последовательности), что подчеркивает то обстоятельство, что результирующий сигнал становится шумоподобным и его трудно отличить от естественного шума.

Как уширить спектр сигнала и сделать его неотличимым от естественного шума, понятно. Для этого, в принципе, можно воспользоваться произвольной чиповой последовательностью. Однако, возникает вопрос: а как такой сигнал принимать? Ведь если он становится шумоподобным, то выделить из него полезный информационный сигнал не так то просто, если вообще возможно. Оказывается, возможно, но для этого нужно соответствующим образом подобрать чиповую последовательность. Используемые для уширения спектра сигнала чиповые последовательности должны удовлетворять определенным требованиям автокорреляции. Под термином автокорреляции в математике подразумевают степень подобия функции самой себе в различные моменты времени. Если подобрать такую чиповую последовательность, для которой функция автокорреляции будет иметь резко выраженный пик лишь для одного момента времени, то такой информационный сигнал возможно будет выделить на уровне шума. Для этого в приемнике полученный сигнал умножается на ту же чиповую последовательность, т.е. вычисляется автокорреляционная функция сигнала. В результате сигнал становится опять узкополосным, поэтому его фильтруют в узкой полосе частот и любая помеха, попадающая в полосу исходного широкополосного сигнала, после умножения на чиповую последовательность, наоборот, становится широкополосной и обрезается фильтрами, а в узкую информационную полосу попадает лишь часть помехи, по мощности значительно меньшая, чем помеха, действующая на входе приемника (рис. 1).

Рис. 1. Использование технологии уширения спектра позволяет

передавать данные на уровне естественного шума

Метод DSSS использует всю полосу одновременно, разбивая ее на 11 одинаковых полос [1]. Сигнал передатчика кодируется таким образом, что каждый бит передаваемой информации преобразуется в последовательность из 11 бит. После чего эта последовательность передается параллельно и одновременно по всем 11 полосам. Приемник, получивший эту последовательность, производит обратное преобразование сигнала. Каждая пара «передатчик-приемник» использует свой алгоритм кодирования, исключающий перехват сигнала другим приемником.

Первое достоинство данного метода заключается в надежной защите передаваемой информации. Вероятность совпадения схем кодирования двух разных устройств практически исключена. Расшифровать же такой сигнал, не зная алгоритма, невозможно.

Второе достоинство состоит в том, что благодаря одиннадцатикратной избыточности информации для передачи сигнала можно использовать маломощную аппаратуру. При этом нет необходимости использовать дорогостоящие усилители или изменять конструкцию антенн. Кроме того, «размазывание» сигнала приводит к тому, что отношение сигнала к шуму становится близким к единице. С точки зрения узкополосной аппаратуры такой сигнал практически не отличается от шума (отсюда произошло второе название - «метод шумоподобного сигнала»). В свою очередь, узкополосная аппаратура не влияет на DSSS, поскольку частичная потеря информации на одной или нескольких полосах не портит сигнал из-за избыточности передаваемой информации. Это позволяет одновременно использовать в одном диапазоне узкополосную и DSSS-аппаратуру.

Метод частотных скачков использует полосу по-иному. Весь диапазон, отведенный для передачи, согласно стандарту 802.11 делится на 79 каналов. Передатчик использует в единицу времени только один из этих каналов, переключаясь между ними согласно заложенному в него алгоритму. Частота таких «скачков» стандартом не определена и варьируется в зависимости от того, в какой стране используется данное оборудование. В свою очередь, приемник синхронно совершает такие же «скачки», используя ту же «случайную» последовательность, что и передатчик. Случайная последовательность является уникальной для каждой пары передатчикприемник.

В отличие от метода прямой последовательности метод FHSS имеет два существенных недостатка. Первый из них заключается в том, что при достаточно большом числе одновременных сеансов работы резко увеличивается вероятность коллизии. Это обусловлено конечным числом каналов и узкополосностью передаваемого в единицу времени сигнала. Два различных сигнала, столкнувшись на одной частоте, заглушат друг друга и инициируют повторную передачу на следующем скачке. Поэтому помехозащищенность реализуется за счет уменьшения пропускной способности. Второй недостаток - создание помех для узкополосной аппаратуры, что в ряде случаев делает невозможным их совместное использование. Это обстоятельство резко сужает круг возможных применений. Аппаратура FHSS, как правило, используется в закрытых помещениях либо на небольшой территории (исключение составляет случай, когда необходимо организовать соединение «точка-точка») [2].

На сегодняшний день существуют следующие разновидности данного стандарта построения беспроводных локальных сетей IEEE 802.11 a/b/g. Стандарт IEEE 802.11, принятый в 1997 г., стал первым стандартом данного семейства. Он предусматривает использование диапазона частот 2,4 ГГц, а также технологии расширения спектра скачкообразной сменой частоты (Frequency Hopping Spread Spectrum или технологии расширения спектра по методу прямой последовательности. [Direct Sequence Spread Spectrum DSSS. Стандарт IEEE 802.11 обеспечивает пропускную способность до 2 Мбит/с в расчете на одну точку доступа

Стандарт IEEE 802.11а предусматривает использование нового, не требующего лицензирования частотного диапазона 5 ГГц и модуляции по методу ортогонального мультиплексирования с разделением частот (Orthogonal Frequency Domain Multiplexing [OFDM]). Применение этого стандарта позволяет увеличить скорость передачи в каждом канале с 11 Мбит/с до 54 Мбит/с. При этом одновременно может быть организовано до восьми непересекающихся каналов, а не три, как в диапазоне 2,4 ГГц. Продукты стандарта IEEE 802.11а (сетевые адаптеры NIC и точки доступа) не имеют обратной совместимости с продуктами стандартов 802.11 и 802.11b, так как они работают на разных частотах.

Стандарт IEEE 802.11b был принят в 1999 г. в развитие принятого ранее стандарта IEEE 802.11. Он также предусматривает использование диапазона частот 2,4 ГГц, но только с модуляцией DSSS. Данный стандарт обеспечивает пропускную способность до 11 Мбит/с в расчете на одну точку доступа. Продукты стандарта IEEE 802.11b, поставляемые разными изготовителями, тестируются на совместимость и сертифицируются организацией Wireless Ethernet Compatibility Alliance (WECA), которая в настоящее время больше известна под названием Wi-Fi Alliance.

Проект стандарта IEEE 802.11g был утвержден в октябре 2002 г. Этот стандарт предусматривает использование диапазона частот 2,4 ГГц, обеспечивая скорость передачи 54 Мбит/с и превосходя, таким образом, ныне действующий стандарт 802.11b. Кроме того, он гарантирует обратную совместимость со стандартом 802.11b. Обратная совместимость стандарта IEEE 802.11g может быть реализована в режиме модуляции DSSS, и тогда скорость передачи будет ограничена одиннадцатью мегабитами в секунду либо в режиме модуляции OFDM, при котором скорость составляет 54 Мбит/с. Таким образом, данный стандарт является наиболее приемлемым при построении беспроводных сетей.

Литература

1. Шахнович И.В. Современные технологии беспроводной связи. М.: Техносфера, 2006. 288 с.

2. Рошан П. Основы построения беспроводных локальных сетей стандарта 802.11. Вильямс, 2004. 296 с.

Воронежский государственный технический университет

УДК 681.3

Т.А. Черепанова, Н.В. Астахов, А.В. Башкиров, Ю.В. Дьячков,

С.Ю. Белецкая

ПРОГРАММИРУЕМАЯ ЛОГИКА

ДЛЯ ВЫСОКОПРОИЗВОДИТЕЛЬНЫХ ПЛАТФОРМ

В статье описаны принципы построения структурированных файловых хранилищ

Требования к файловым хранилищам (network attached storage — NAS) компаний постоянно возрастают. Это связано, прежде всего, со значительным увеличением числа конечных пользователей IT - инфраструктуры, а также количественным и качественным ростом запросов с их стороны; наращиванием производительности рабочих станций и серверов; ростом объемов обрабатываемых данных и распространением HPC-систем (High Performance Computing) для проведения расчетов; развитием инфраструктуры передачи данных и т.п. Это приводит к тому, что классические файловые серверы уже просто не способны справляться с возросшей нагрузкой [1,2].

Большая часть NAS-серверов строится на основе стандартных компонентов или, проще говоря, на базе стандартных серверных платформ. И, несмотря на то, что производительность NAS-серверов постоянно возрастает за счет использования современных CPU, шин/интерфейсов, высокопроизводительных дисков/средств хранения данных, в ряде случаев требования к файловым хранилищам могут значительно превосходить их возможности.

Один из наиболее простых способов решения этой проблемы — развертывание множества NAS-устройств в сетевой инфраструктуре компании. Однако это приводит к децентрализации данных и усложнению управления хранением. Частично эти недостатки можно устранить, объединяя файловые хранилища в один общий пул на основе средств виртуализации, однако проблемы производительности при этом остаются.

Многие пользователи ищут решение проблемы производительности в переходе к SAN-инфраструктурам. Но здесь появляются препятствия, которых не было в NAS-инфраструктурах. Одно из наиболее существенных — это более дорогая реализация SAN-инфраструктуры в сравнении с NAS, но основная — это то, что SAN не обеспечивает стандартно реализуемого разделяемого доступа к файлам, необходимого для простого управления данными.

Другой подход к решению выше отмеченных проблем — это переход к концепции кластеров хранения. В дальнейшем для этого будем использовать термин грид-хранение или storage-grids. Однако длительное время из-за ряда проблем, связанных с работой с файловыми системами, эта концепция не имела промышленных реализаций. К ним можно отнести: блокировку файлов при их совместном использовании, когерентность кэш-памяти, кэширование с клиентской стороны и много других аспектов совместного использования файловой системы требующих решения для реализации этой концепции.

Часть этих проблем для большинства применений разрешимы, но для приложений, связанных с вычислительными кластерами, требуются значительные усилия. Поэтому несколько лет назад TIETF-комитет (The Internet Engineering Task Force) предложил новый стандарт, названный pNFS и призванный упростить развитие NAS-серверов для параллельных вычислений. pNFS представляет собой расширение NFS v4 и призван стандартизовать усилия промышленности в этой области. В архитектуре BlueArc полностью поддерживается этот новый стандарт и ряд других протоколов для ускорения потока данных.

Рис. 1. Структура BlueArc

Физически NAS-решение компании BlueArc представляет собой NAS-gateway или специализированную систему, управляющую потоком данных и файловых операций, которая для подключения к прикладным серверам и пользователям имеет или 6 1GE портов, или 2 порта по 10GE с одной стороны, а с другой — 4 FC-порта (1, 2 или 4 Gbps) для подключения системы хранения (рис. 1). Для управления имеются еще четыре 100 Mbps порта.

Концепция, заложенная в основу архитектуры решения от компании BlueArc — это аппаратная реализация файловых систем как локальной SiliconFS, так и сетевых NFS, CIFS.

За счет использования специализированных чипов FPGA и высокой параллелизации в обработке потоков в NAS-системе BlueArc удалось достичь производительность одну из самых высоких на тесте SPECsfs97_R1.v3 — 98131 NFS SpecOps/Sec на 1 узел. Число узлов может масштабироваться от 1 до 4 (в ближайшее время — 8). При этом общий объем поддерживаемых ресурсов хранения в одной файловой системе может достигать 512 Тбайт (в ближайшей перспективе — до 2 Пбайт), а число файлов в одной директории — 4 млн. и до 60 тыс. одновременно поддерживаемых соединений.

Одно из основных преимуществ, помимо названных, — возможность поддержки самых разных по требованиям приложений на одной консолидированной системе хранения, что обеспечивается за счет возможности выделения для них разных уровней RAID, типов дисков (FC, SATA), а также возможность назначения разных политик управления данными.

NAS-решения BlueArc строятся на т.н. Titan Silicon Server архитектуре. В ее основе лежит имплементация функций файлового сервера в аппаратуру (чипы и специализированные устройства). Технология Silicon Server представляет множество машин с массовым параллелизмом для реализации функциональности, которая в стандартном файловом сервере выполняется на уровне операционной системы, но с гораздо более высокой производительностью и надежностью. Однако при этом поддерживаются все стандартные протоколы для коммуникации с существующими клиентскими компьютерами.

Программируемые вентильные матрицы — FPGA — или параллельные конечные автоматы составляют основу архитектуры BlueArc Titan. Современные FPGAs — перепрограммируемые интегральные схемы, представляющие собой высокоэффективные аппаратные компоненты/чипы с собственной памятью, буферами ввода-вывода и внутренней синхронизацией. FPGA подобны специализированным интегральным схемам (Application Specific Integrated Circuits — ASIC), используемым, например, в высокоскоростных коммутаторах и маршрутизаторах, но, в отличие от ASIC, являются перепрограммируемыми. Возможность перепрограммирования FPGA во время эксплуатации дает повышенную гибкость решения. Например, возможность его изменения для выполнения новых или модифицированных задач, а также для поддержания новых протоколов, появляющихся на рынке, или решения проблем апгрейдов.

Разработчики аппаратуры иногда используют FPGA для предварительного дизайна, поскольку они позволяют быстро ("на лету") проводить все изменения в течение стадии проектирования и короткой эксплуатации. Как только логика отработана, вся схемотехника переносится на ASIC. В BlueArc Titan архитектуре на FPGA реализована финальная имплементация Titan-сервера.

За счет параллельной работы нескольких FPGA и их специализации производительность одноузлового Titan-сервера (по заявлениям разработчика) превосходит производительность одноядерного 3,8 ГГц микропроцессора Intel на однотипных операциях более чем в 10 000 раз.

Концептуально NAS-платформа компании BlueArc была разработана в трех отдельных секциях, названных подсистемами.

Первая подсистема — Network Interface Module (NIM) — ответственна за управление всеми Ethernet функциями ввода-вывода, соответствующими OSI уровню 1-4. Функции, имплементированные в NIM-модуль, включают управление Ethernet и Jumbo Ethernet фреймами до 9000 байт, ARP, IP-протоколом и роутингом, а также TCP- и UDP-протоколом.

Вторая подсистема, состоящая из двух модулей — File System Modules (FSA & FSB), поддерживает различные сетевые файловые системы, включая NFS, CIFS, FTP и NDMP, а также объектную файловую систему.

Третья секция — Storage Interface Module (SIM) — обеспечивает кэширование и управление для подключенных систем хранения.

Каждая подсистема имеет собственные процессорные мощности и память для управления всеми задачами параллельно. Такая архитектура позволяет всем процессам работать параллельно без влияния на другие процессы, что существенно отличается от архитектуры традиционных NAS-серверов.

Каждая из подсистем связана с соседними через 2 высокоскоростных канала, каждый из которых может писать и читать данные со скоростью до 20 Гбит/с без влияния друг на друга, что позволяет реализовать преимущества полной дуплексной связи.

Конструктивно NAS-платформа компании BlueArc представляет собой 4U модульную систему, в которую устанавливаются 4 специализированных модуля, функциональность которых описана выше. Также в состав решения входит выделенный сервер управления, так называемый SMU.

Литература

1. Иванов В.Ю. Высокопроизводительные системы на основе программируемой логики. М.: IT-пресс, 2008. 250 с., ил.

2. Крамарева Н.И. Масштабируемые файловые хранилища. М., 2007. 112 с.

Воронежский государственный технический университет

УДК 681.3

К.С. Струков, Н.В. Астахов, А.В. Башкиров,

Ю.В. Дьячков, С.Ю. Белецкая

ТЕНДЕНЦИИ РАЗВИТИЯ ЦИФРОВОЙ ТЕХНИКИ В УСЛОВИЯХ ПРИМЕНЕНИЯ ПРОГРАММИРУЕМОЙ ЛОГИКИ

Тенденция развития цифровой техники на современном этапе является широкое применение ресурсов программируемой логики не только для реализации отдельных блоков, но и проектируемых устройств в целом, вплоть до создания систем на кристалле

Одной из тенденций развития цифровой техники на современном этапе является широкое применение ресурсов программируемой логики не только для реализации отдельных блоков, но и проектируемых устройств в целом, вплоть до создания систем на кристалле. Программируемые логические интегральные схемы (ПЛИС) и соответствующие средства проектирования, выпускаемые фирмой Xilinx®, позволяют выполнить жесткие требования, предъявляемые ко времени разработки, и в сжатые сроки создавать цифровые устройства и системы с различным уровнем сложности и степенью интеграции [1,2,3].

Программируемые логические интегральные схемы (ПЛИС) все более широко используются для создания цифровых систем различного назначения. Фирма Xilinx, являясь ведущим мировым производителем ПЛИС, предоставляет разработчикам широкий спектр кристаллов с различной технологией производства, степенью интеграции, архитектурой, быстродействием, потребляемой мощностью и напряжением питания, выпускаемых в различных типах корпусов и в нескольких вариантах исполнения, включая промышленное, военное и радиационностойкое. Кристаллы, выпускаемые фирмой Xilinx, в полной мере реализуют преимущества ПЛИС по сравнению с "жесткой логикой":

высокое быстродействие;

возможность перепрограммирования непосредственно в системе;

высокая степень интеграции, позволяющая разместить цифровое устройство в одном кристалле и тем самым снизить время и затраты на трассировку и производство печатных плат;

сокращение времени цикла разработки и производства устройства;

наличие мощных инструментов САПР, позволяющих устранить возможные ошибки в процессе проектирования устройства;

сравнительно низкая стоимость (в пересчете на один логический вентиль).

В настоящее время каталог продукции фирмы Xilinx включает в себя пять серий ПЛИС с архитектурой FPGA (Field Programmable Gate Array), две серии кристаллов CPLD (Complex Programmable Logic Device) и две серии ПЗУ/ППЗУ, предназначенные для хранения конфигурационных данных.

В кристаллах CPLD конфигурационные данные хранятся во внутренней энергонезависимой памяти. Соответствующая информация заносится в процессе программирования ПЛИС, которое может осуществляться непосредственно в системе с помощью загрузочного кабеля, подключаемого к JTAG-порту. В состав этого сегмента ПЛИС, выпускаемых фирмой Xilinx, входят следующие серии кристаллов CPLD:

ХС9500, представленная семействами ХС9500, XC9500XL, XC9500XV;

CoolRunner TM, содержащая семейства CoolRunner XPLA3™ и CoolRunner-II.

ПЛИС серий FPGA выполнены на основе статического ОЗУ. Так как информация о конфигурации кристалла записывается во внутреннее "теневое" ОЗУ, то при выключении источника питания эти данные не сохраняются. Поэтому для хранения конфигурационной последовательности используются внешние элементы ПЗУ и ППЗУ, данные из которых заносятся в "теневое" ОЗУ в процессе инициализации ПЛИС, выполняемой при включении напряжения питания или подаче специального сигнала. Линейка выпускаемых кристаллов FPGA представлена следующими сериями:

Spartan™, включающей семейства Spartan, SpartanXL, Spartan-II и Spartan-IIE;

Virtex™, состоящей из семейств Virtex, Virtex-E, Virtex-II, Virtex-IV и Virtex-V;

XC4000, содержащей семейства ХС4000Е, XC4000EX, XC4000XL, XC4000XLA;

XC5200;

XC3000, включающей семейства ХС3000А. XC3000L, ХС3100А, XC3100L.

Для хранения конфигурационных данных кристаллов серий FPGA фирма Xilinx предоставляет следующие разновидности ПЗУ:

серию однократно программируемых ПЗУ ХС1700;

серию перепрограммируемых в системе ППЗУ ХС18V00.

Серии ХС3000, ХС5200 и ХС4000 считаются морально устаревшими, их производство осуществляется только для поддержания ранее разработанных устройств. Несмотря на то, что кристаллы этих серий продолжают выпускаться, в большинстве своем они не рекомендуются для использования в новых проектах. Вместо них следует использовать ПЛИС семейств Spartan и Virtex. [1,2,3].

Система проектирования ПЛИС на примере программных решений фирмы Xilinx.

Программа Навигатор проекта (Project Navigator™) предназначена для организации эффективного управления процессом проектирования цифрового устройства на базе ПЛИС Xilinx в среде пакета WebPACK ISE. Она является основой интегрированной среды разработки проекта. Управляющая оболочка пакета WebPACK ISE Навигатор проекта предоставляет пользователю удобный интерфейс для работы с проектом и управления всеми процессами в ходе проектирования, включая программирование ПЛИС. Запуск всех необходимых программных модулей пакета осуществляется непосредственно в среде Навигатора проекта.

В состав пакета WebPACK ISE входит встроенный текстовый редактор, предназначенный для ввода описаний разрабатываемых устройств на языках высокого уровня VHDL и Verilog. HDL- редактор (Hardware Description Language) обладает следующими особенностями:

Подсветка синтаксических конструкций языков VHDL и Verilog;

Возможность использования шаблонов различных частей модулей;

Автодополнение зарезервированных слов;

Выделение функций, входящих в стандартные библиотеки;

В режиме отладки программы, позволяет устанавливать точки остановки и метки;

Так же имеется возможность использования внешних текстовых редакторов для ввода кода программы.

Кроме текстового редактора в состав САПР WebPACK ISE входит схемотехнический редактора Engineering Schematic Capture™ (ECS), при этом следует обратить внимание на то, что программные средства рассматриваемого пакета ориентированы, прежде всего, на применение языков HDL для описания проектируемого устройства. Однако схемотехнический редактор ECS целесообразно использовать в случае применения смешанного способа описания проектируемого устройства. При таком способе функциональные блоки проектируемого устройства описываются на одном из языков HDL, а для верхнего уровня иерархии проекта, где производится их объединение, используется схемотехническая форма описания. Графические символы для представления функциональных блоков и схема верхнего уровня иерархии проекта создаются средствами схемотехнического редактора ECS. Учитывая, что САПР WebPACK ISE укомплектована обширными библиотеками компонентов для всех поддерживаемых пакетом семейств ПЛИС фирмы Xilinx, описание проектируемого устройства может быть полностью выполнено в виде схем, разработанных в среде редактора ECS. Несмотря на то, что схемотехническая форма представления является наиболее привычной для разработчиков, рекомендуется использовать один из языков HDL, например VHDL. Этот язык поддерживается большинством САПР, и поэтому разработанный проект легко может быть перенесен из одной системы в другую. [1,2,3].

Схемотехнический редактор ECS предназначен для создания модулей исходного описания проекта в форме принципиальных схем, а также для формирования условных графических образов (УГО) компонентов и функциональных блоков проектируемого цифрового устройства.

Отличительными особенностями редактора ECS являются:

возможность одновременного открытия нескольких рабочих окон для создания и редактирования схем и символов;

использование единой управляющей графической оболочки для создания и редактирования схем и символов;

удобный механизм создания многостраничных схем;

эффективные средства разработки многоуровневых иерархических структур;

двухступенчатый контроль электрических соединений и целостности схемы;

возможность внесения дополнительной информации, необходимой в процессе проектирования устройства, в форме атрибутов;

"мастер" автоматического формирования УГО функциональных блоков и компонентов схем;

возможность размещения на страницах схемы графических и текстовых элементов оформления.

При создании схем в среде редактора ECS используются следующие элементы:

условные графические образы компонентов из библиотек редактора или созданные пользователем;

элементы соединений (проводники и шины);

маркеры цепей, предназначенных для подключения "внешних" элементов и контактов ПЛИС;

атрибуты (параметры компонентов, цепей и контактов);

текстовая информация;

декоративные графические элементы.

Два последних типа элементов не являются обязательными. Они не оказывают влияния на процесс проектирования и используются лишь для представления схем (документации) в соответствии с предъявляемыми требованиями.

Литература

1. Зотов В.Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС XILINX. М.: Горячая линия Телеком, 2006. 520 с., ил.

2. Система синтаксического и семантического контроля VHDL-описаний “VHDL-анализатор”. Руководство пользователя. М.: РосНИИИС, 1991. 112 с.

3. Резидентный справочник по языку VHDL. Руководство пользователя. М.: РосНИИИС, 1993. 21 с.

4. Alliance: A Complete CAD System for VLSI Design. Users manual. Paris: Universite Pierre et Marie Curie, 1997.

Воронежский государственный технический университет

УДК 681.3

Д.Е. Басов, Н.В. Астахов, А.В. Башкиров,

Ю.В. Дьячков, С.Ю. Белецкая

ОСОБЕННОСТИ ПРОЕКТИРОВАНИЯ ПЛИС

С МИКРОМОЩНЫМ ПОТРЕБЛЕНИЕМ

В процессе разработки устройств часто возникает необходимость расчета мощности, потребляемой кристаллом, на основе которого реализуется проект. Этот параметр является чрезвычайно важным при использовании ПЛИС семейств CPLD CoolRunner XPLA3 и CoolRunner-II

В ходе разработки устройства часто возникает необходимость расчета мощности, потребляемой кристаллом, на основе которого реализуется проект. Этот параметр является чрезвычайно важным при использовании ПЛИС семейств CPLD CoolRunner XPLA3 и CoolRunner-II. Кристаллы этих серий относятся к классу ПЛИС с микромощным потреблением и предназначены, в первую очередь, для применения в мобильных системах, где емкость автономного источника питания ограничена. Поэтому необходимо оценить продолжительность работы проектируемого устройства в зависимости от ресурса используемого автономного источника питания. При проектировании цифровых устройств на базе кристаллов семейств FPGA таких, как Spartan-II, Spartan-IIE, Virtex, Virtex-II, Virtex-IV, Virtex-V, задача расчета потребляемой мощности является также актуальной. Потребляемая мощность ПЛИС этих серий в динамическом режиме зависит от проектов, выполняемых на их основе, и может изменяться в широком диапазоне, достигая значительной величины. Чтобы корректно сформулировать требования, предъявляемые к источнику питания этих устройств, необходимо иметь оценку их потребляемой мощности. Для этих целей в состав системы проектирования WebPACK ISE включен программный модуль XPower, который предназначен для автоматизированного расчета оценки потребляемой мощности устройств, проектируемых на базе кристаллов фирмы Xilinx. Программный модуль XPower может функционировать как в интерактивном режиме, так и в режиме командной строки. Наиболее рациональным является запуск программы XPower в интерактивном режиме с помощью Навигатора проекта [1,2,3].

Исходная информация об используемых ресурсах кристалла, необходимая для оценки его потребляемой мощности с помощью программы XPower, становится доступной только после завершения этапа размещения и трассировки проекта, а точнее, после выполнения стадии Fit для семейств CPLD и Place and Route для семейств FPGA. Кроме того, дополнительная информация, которая используется в процессе вычислений и может повысить точность оценки, формируется в ходе выполнения этапа полного временного моделирования проекта. Система HDL-моделирования ModelSim, входящая в комплект пакета WebPACK ISE в редакции ModelSim XE Starter, позволяет формировать файлы результатов моделирования в формате VCD (Value Change Dump), воспринимаемом программой XPower. Программа XPower предоставляет разработчику следующие возможности:

три метода определения исходных данных, необходимых для выполнения вычислений;

вычисление оценки потребляемой мощности проектируемого устройства с точностью плюс-минус 10 %;

расчет температурных характеристик кристалла ПЛИС, используемого для реализации проекта;

получение оценки продолжительности работы проектируемого устройства от автономного источника напряжения питания (батареи);

перерасчет оценок после ввода каждого нового значения исходных параметров;

формирование подробного отчета о полученных результатах вычислений, содержащего оценки потребляемой мощности различными блоками проектируемого устройства и ресурсами кристалла, в текстовом (ASCII) и HTML-формате.

Для моделирования цифровых систем, которые представлены в виде HDL-описаний, выполненных с использованием языков высокого уровня VHDL и Verilog предназначен пакет программных средств ModelSim.

Отличительные особенности пакета:

Полная поддержка всех основных стандартов языков VHDL и Verilog и их расширений: IEEE VHDL Std 1076-1987 и IEEE VHDL Std 1076-1993, IEEE 1164-1993 Standard Multivalue Logic System for VHDL Interoperability, IEEE 1076.2-1996 Standard VHDL Mathematical Packages, IEEE VITAL Std 1076.4-1995 (VITAL'95), IEEE 1076.4-2000 (VITAL 2000) и IEEE Verilog Std 1364-1995, IEEE Verilog Std 1364-2001. Полная совместимость со спецификациями 1.0-3.0 стандартного формата описания задержек SDF (Standard Delay Format) обеспечивает возможность обратной аннотации временных параметров. Кроме того, пакет ModelSim удовлетворяет требованиям VCD (Value Change Dump) по формированию стандартных выходных векторов для VHDL и Verilog и PLI (Programming Language Interface) [1,2,3].

Единое ядро моделирования пакета SKS (Single Kernel Simulation), обеспечивающее возможность полной отладки "смешанных" проектов, которые одновременно содержат модули, написанные на VHDL и Verilog. Для реализации этого режима предусмотрена специальная лицензия (редакция пакета ModelSim SE/PLUS), разрешающая совместное VHDL- и Verilog-моделирование.

Поддержка библиотек всех ведущих фирм-изготовителей как программируемых логических интегральных схем семейств FPGA и CPLD, так и специализированных интегральных схем ASIC (Application-Specific Integrated Circuit), предоставляющая разработчику широкие возможности сравнения различных платформ и выбора оптимальной для реализации проектируемой системы. Сертифицированные изготовители библиотеки обеспечивают максимальную достоверность результатов моделирования.

Высокая скорость компиляции и моделирования (полнофункциональных версий), обеспечивающая минимальное время отладки систем различного уровня сложности. Одним из главных факторов, повышающих производительность, является использование принципа оптимизированной прямой компиляции. В соответствии с этим принципом исходные VHDL- или Verilog-описания компилируются в машинно-независимый объектный код, исполняемый на любой поддерживаемой платформе.

Открытая архитектура программных средств ModelSim, обеспечивающая тесную интеграцию с пакетами САПР "третьих" фирм. Пользователь может выполнять этапы моделирования фактически в рамках основной системы проектирования, в среде которой осуществляется процесс разработки устройства. Средства управления пользовательским интерфейсом Tcl (Tool command language) и Tk (Tool kit) предоставляют возможность организации прямого доступа к моделирующему ядру ModelSim, загрузки информации о выполнении процесса моделирования и его результатов в среду используемой САПР и управления работой системы ModelSim через интерфейс применяемых средств проектирования. Возможен также и противоположный метод интеграции с программным обеспечением других фирм, когда в качестве основной системы используется ModelSim, интерфейсная оболочка которой адаптируется для управления выбранным пакетом САПР.

Наличие защищенного режима компиляции моделей, гарантирующего выполнение требований, предъявляемых к охране интеллектуальной собственности, к которой относятся коммерчески распространяемые модули (IP Core). В обычном режиме разрешается полная отладка моделей с доступом к исходному коду и внутренней структуре объекта. Если интеллектуальные продукты распространяются производителем в скомпилированном виде без передачи исходного кода, внутренней структуры и переменных, то следует использовать защищенный режим компиляции моделей. При этом в процессе моделирования отображается состояние только внешних (интерфейсных) сигналов объектов интеллектуальной собственности, а контроль поведения их внутренних сигналов и процессов не доступен пользователю.

Расширенные отладочные возможности пакета, позволяющие пользователям не только быстро отыскать и идентифицировать ошибки, но и сразу же устранить причины их возникновения. После обнаружения ошибки достаточно перейти из режима отладки в режим редактирования исходного кода, внести соответствующие изменения в текст описания и после сохранения файла выполнить повторную компиляцию данного модуля. Все перечисленные операции производятся в процессе текущего сеанса работы системы моделирования и требуют минимальных временных затрат. Динамическое обновление окон системы обеспечивает возможность быстрого и легкого перемещения по базе данных проекта.

Наличие встроенного индикатора активности кода, не только повышающего эффективность отладки проекта, но и позволяющего быстро создавать более полные и надежные тестовые последовательности. Этот инструмент предоставляет возможность проследить строки исходного кода, которые не "активизировались" в процессе моделирования и вывести в графической форме соответствующий отчет обо всех файлах проекта. Индикатор активности кода может быть использован как на уровне отдельного блока, так и для всей системы в целом.

Использование встроенного анализатора производительности, позволяющего повысить скорость моделирования за счет обнаружения в проекте и последующего устранения факторов, оказывающих отрицательное влияние на быстродействие этого процесса. С помощью этого инструмента можно получить информацию о библиотечных элементах, обработка которых требует значительных временных затрат, фрагментах исходного кода, написанных нерационально с точки зрения скорости его исполнения, неиспользуемых сигналах в выводимых списках, избыточном коде в тестовых последовательностях. Исключение перечисленных элементов из проекта позволяет резко снизить общее время моделирования.

Возможность работы в различных режимах, в том числе и пакетном. Разработав и отладив некоторый сценарий моделирования в интерактивном режиме, можно оформить его для последующего использования в виде пакетного командного файла.

• Доступный для разработчика визуальный пользовательский интерфейс и наличие подробной справочной системы, сокращающие время освоения пакета моделирования. Средства управления пользовательским интерфейсом Tcl и Tk позволяют выполнить настройку его элементов (панелей кнопок, меню) в соответствии с требованиями каждого конкретного пользователя [1,2,3].

Система моделирования ModelSim выпускается в двух основных редакциях: Special Edition (SE), функционирующей под управлением операционных систем (ОС) UNIX™, Linux™, Windows 98, Windows ME™, Windows 2000, Windows NT, Windows XP, и Personal Edition (РЕ), предназначенной только для ОС семейства Windows. Кроме того, имеются специализированные редакции, предназначенные для интеграции с пакетами САПР "третьих" фирм.

Литература

1. Максфилд Клайв. Проектирование на ПЛИС. Архитектура, средства и методы. – М.: Издательский дом «Додека» 2007. - 408 с., ил.

2. Зотов В.Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС XILINX. М.: Горячая линия Телеком, 2006. 520 с., ил.

3. Система синтаксического и семантического контроля VHDL-описаний “VHDL-анализатор”. Руководство пользователя. М.: РосНИИИС, 1991. 112 с.

Воронежский государственный технический университет

УДК 681.3

Д.В. Гукин, Н.В. Астахов, А.В. Башкиров, М.Ю. Чепелев,

Ю.В. Дьячков, С.Ю. Белецкая

НОВЫЕ ПОДХОДЫ К ПРОЦЕССУ ОПИСАНИЯ СТРУКТУРЫ ПРОЕКТА В САПР WebPACK ISE

При определении семейства и типа ПЛИС для реализации проекта необходимо не только оценить его сложность с учетом требований, предъявляемых к быстродействию, потребляемой мощности, условиям эксплуатации, но и учесть дополнительные факторы, как, например, стоимость, возможность перепрограммирования в системе

В процессе разработки цифровых устройств на базе ПЛИС Xilinx в общем случае можно выделить следующие этапы:

создание нового проекта (выбор семейства и типа ПЛИС, а также средств синтеза);

подготовка описания проектируемого устройства в схемотехнической, алгоритмической или текстовой форме;

синтез устройства;

функциональное моделирование;

размещение и трассировка проекта в кристалле;

временное моделирование;

программирование ПЛИС (загрузка проекта в кристалл).

Перед созданием нового проекта следует определиться с выбором метода описания разрабатываемого устройства и, соответственно, средств синтеза. При определении семейства и типа ПЛИС для реализации проекта необходимо не только оценить его сложность с учетом требований, предъявляемых к быстродействию, потребляемой мощности, условиям эксплуатации, но и учесть дополнительные факторы, как, например, стоимость, возможность перепрограммирования в системе. Выбранное семейство или тип кристалла при необходимости достаточно легко можно изменить в процессе проектирования. Исходная информация о проектируемом устройстве может быть представлена в виде принципиальных схем, описаний на языке HDL, диаграмм состояний, пакетов и библиотек пользователя. На этом же этапе можно установить временные и топологические ограничения, которые должны учитываться при синтезе, размещении и трассировки проекта в кристалле. В процессе синтеза на основании исходных модулей проекта формируется список соединений (netlist), содержащий набор примитивов или компонентов, который может быть реализован на основе ресурсов выбранного кристалла ПЛИС. Результаты синтеза используются далее в качестве исходных данных средствами размещения и трассировки. Функциональное моделирование устройства производится без учета реальных значений задержек прохождения сигналов и позволяет проконтролировать соответствие выходных сигналов алгоритмам работы проектируемого устройства. На этапе размещения и трассировки проекта в кристалл производится распределение выполняемых функций в конфигурируемые логические блоки CLB (Configurable Logic Block) или макроячейки Macrocell, в зависимости от используемого семейства ПЛИС, и формирование необходимых связей в кристалле. В процессе выполнения этого этапа проектирования также определяются реальные значения задержек распространения сигналов, которые необходимы для полного временного моделирования устройства. Основным результатом этапа размещения и трассировки является формирование файла, в котором содержится информация о конфигурации ПЛИС, реализующей проектируемое устройство. Завершением процесса разработки цифрового устройства является загрузка конфигурационных данных в кристалл с помощью соответствующих программ и загрузочного кабеля. Следует обратить внимание на то, что этапы функционального и временного моделирования не являются обязательными. Тем не менее, не рекомендуется пренебрегать этими этапами, так как высокоэффективные средства моделирования, включаемые в состав пакетов САПР фирмы Xilinx, позволяют обнаружить большинство возможных ошибок и, тем самым, значительно сократить общее время разработки устройства. При обнаружении ошибок на любом из этапов, например, логических ошибок на этапе функционального моделирования или при получении неудовлетворительных результатов временного моделирования, следует вернуться на стадию разработки исходных описаний проекта, внести необходимые изменения и повторить последующие этапы [1,2,3].

Выполнение этапов создания нового проекта и подготовки исходных описаний проектируемого устройства не зависит от выбора типа ПЛИС (CPLD или FPGA), используемого для его реализации. Содержание последующих этапов (синтеза, функционального и временного моделирования, размещения, трассировки и загрузки проекта в кристалл) различается для случаев использования ПЛИС семейств CPLD и FPGA.

Проектом в САПР WebPACK ISE называется совокупность модулей (файлов), которые содержат информацию, необходимую для выполнения всех этапов процесса разработки цифрового устройства на базе ПЛИС Xilinx. В структуре проекта WebPACK ISE можно выделить следующие группы модулей:

исходные описания проектируемого устройства в графической или текстовой форме;

модули временных и топологических ограничений проекта;

документация, сопровождающая проект;

промежуточные результаты, используемые в качестве исходных данных для последующих шагов проектирования;

отчеты о выполнении основных этапов проектирования;

функциональная и временная модели проектируемого устройства;

описания тестовых воздействий, необходимых для моделирования устройства, в текстовом и графическом формате;

результаты функционального и временного моделирования в графической и текстовой форме;

отчеты, формируемые вспомогательными средствами пакета;

окончательные результаты проектирования, используемые для конфигурирования ПЛИС.

Все модули проекта располагаются в одном каталоге (пачке), название которого совпадает с названием проекта. Изначально проект представлен только заголовком и модулем, в котором указываются параметры проекта. Затем к проекту добавляются модули описания проектируемого устройства. Далее, после выполнения каждого этапа процесса разработки устройства, в проект включаются результаты, полученные на этом этапе, и соответствующий отчет. Кроме того, разработчик может включить в проект необходимую текстовую документацию.

Исходное описание проектируемого устройства может быть представлено в виде:

принципиальных схем;

описаний на одном из языков HDL;

диаграмм состояний и переходов между ними.

Кроме того, допускаются смешанные способы описания, представляющие собой сочетание перечисленных выше форм. САПР WebPACK ISE поддерживает все указанные методы описания разрабатываемого устройства и содержит программные средства создания соответствующих форм.

Языки описания аппаратуры HDL в настоящее время становятся основным средством представления цифровых устройств в процессе их проектирования. В значительной степени это обусловлено такими взаимосвязанными факторами, как широкое применение программируемых логических интегральных схем в качестве элементной базы для создания цифровых систем, постоянным совершенствованием соответствующих инструментов синтеза и средств моделирования. Кроме того, при реализации больших проектов на базе ПЛИС проявляются ограничения схемотехнического метода, которые снимаются при использовании языков высокого уровня VHDL и Verilog. Применение этих языков также повышает мобильность проектов, так как большинство систем проектирования поддерживает VHDL и Verilog. Поэтому проекты, представленные в виде HDL - описаний, с минимальными изменениями переносятся из одной системы проектирования в другую. Необходимость такого переноса часто возникает при смене элементной базы для реализации проектируемого устройства. Для пакета WebPACK ISE метод описания проекта с использованием языков HDL является основным. Учитывая, однако, что схемотехнический способ представления проектируемого устройства наиболее нагляден и привычен для разработчиков и поэтому широко практикуется.

Дополнительная информация для программ синтеза, размещения и трассировки может располагаться непосредственно в модулях исходного описания проекта в форме атрибутов или вынесена в файл временных и топологических ограничений User Constraints File (UCF). Использование файла UCF является наиболее предпочтительным, так как при этом сохраняется универсальность модулей исходного описания, которые могут использоваться в других проектах. Кроме того, чтобы внести коррективы в параметры ограничений, например, при изменении типа ПЛИС, не требуется редактировать различные модули исходного описания, а достаточно скорректировать содержимое файла UCF. Файл временных и топологических ограничений проекта имеет текстовый формат, каждая строка которого представляет собой выражение, описывающее соответствующий параметр. Для внесения информации в файл UCF можно использовать встроенный HDL-редактор или специальную программу Constraints Editor пакета WebPACK ISE, которая на основании данных, указанных разработчиком в диалоговом режиме, автоматически формирует соответствующие выражения для описания ограничений проекта. Кроме того, в проектах, выполняемых на основе ПЛИС семейств FPGA, для этих целей может использоваться редактор назначения выводов кристалла и топологических ограничений РАСЕ (Pinout and Area Constraints Editor).

Для описаний наиболее часто используемые временные и топологические ограничения применяются следующие форматы выражений. Параметр LOC позволяет осуществить закрепление выводов перед трассировкой, а также явно указать функциональный блок для реализации элементов проекта [1,2,3].

Временные ограничения могут устанавливаться как для отдельных элементов схемы (например, цепей), так и для совокупности элементов определенного типа. Такие совокупности называются временными группами. Вначале рассмотрим временные ограничения, относящиеся к единичному элементу схемы.

Литература

1. Максфилд Клайв. Проектирование на ПЛИС. Архитектура, средства и методы. М.: Издательский дом «Додека» 2007. 408 с., ил.

2. Зотов В.Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС XILINX. М.: Горячая линия Телеком, 2006. 520 с., ил.

3. Система синтаксического и семантического контроля VHDL-описаний “VHDL-анализатор”. Руководство пользователя. М.: РосНИИИС, 1991. 112 с.

Воронежский государственный технический университет

УДК 681.3

C.К. Пономарев, Н.В. Астахов, А.В. Башкиров,

Ю.В. Дьячков, С.Ю. Белецкая

СИНТЕЗ ЦИФРОВЫХ УСТРОЙСТВ НА БАЗЕ ПЛИС XILINX

Элементы низкоуровневого описания, формируемого в процессе синтеза, должны соответствовать архитектуре семейства ПЛИС, выбранного для реализации проекта. Синтезированный список цепей должен быть максимально адаптирован к ресурсам используемого кристалла, что обеспечивает его наиболее эффективное отображение средствами размещения и трассировки на физическом уровне

Этап синтеза представляет собой процесс трансформации исходного HDL-описания проектируемого устройства в список цепей, выполненный на низком логическом уровне. Элементы низкоуровневого описания, формируемого в процессе синтеза, должны соответствовать архитектуре семейства ПЛИС, выбранного для реализации проекта. Синтезированный список цепей должен быть максимально адаптирован к ресурсам используемого кристалла, что обеспечивает его наиболее эффективное отображение средствами размещения и трассировки на физическом уровне. Поэтому результаты синтеза одного и того же проекта отличаются при использовании ПЛИС семейств CPLD и FPGA.

Процесс синтеза начинается с анализа исходного HDL-описания проектируемого устройства, в ходе которого делаются попытки выделения блоков кода, представимых в виде соответствующих макросов. Использование макросов часто позволяет повысить производительность разрабатываемого устройства, поэтому средства синтеза пытаются идентифицировать как можно большее их количество. Выделенные макросы в процессе последующей оптимизации, выполняемой на этапе синтеза, могут сохраняться в виде отдельных блоков или оптимизироваться совместно с окружающей логикой. Выбор одного из этих способов представления с целью достижения наилучших результатов оптимизации определяется типом и размером макроса. Управление процессом идентификации макросов различного типа (например, ПЗУ, ОЗУ, мультиплексоров, дешифраторов, приоритетных шифраторов, регистров сдвига) осуществляется с помощью соответствующих ограничений или параметров синтеза HDL options Выделенные макросы впоследствии могут быть реализованы с помощью макрогенераторов, входящих в состав средств синтеза, размещения и трассировки.

Следующим шагом в процессе синтеза является оптимизация, которая при использовании ПЛИС семейств FPGA для реализации проекта выполняется в два захода. Вначале выполняется оптимизация каждого отдельного объекта или модуля HDL-описания. Затем производится их объединение, и создается полный список соединений (netlist) проекта. Завершающим шагом является оптимизация полученного списка цепей.

Основным результатом этапа синтеза, выполняемого средствами Xilinx Synthesis Technology (XST), является формирование файла NGC, который представляет собой описание проекта на низком логическом уровне в двоичном формате.

Этап реализации проектов (Implement Design), выполняемых на базе ПЛИС семейств CPLD фирмы Xilinx, включает в себя две фазы: трансляции (Translate) и распределения ресурсов кристалла для реализации проектируемого устройства (Fit). В качестве названия для фазы Fit в литературе используются различные термины: компоновка, покрытие. Но ни один из них не соответствует полностью содержанию этого процесса. Поэтому в дальнейшем Fit будем называть фазой размещения и трассировки проекта. Но при этом следует учитывать, что одноименный этап в процессе проектирования устройства на основе ПЛИС семейств FPGA имеет принципиально иное содержание, в корне отличное от Fit.

В процессе трансляции выполняется объединение всех списков соединений в формате EDIF, входящих в состав проекта, и информации обо всех ограничениях, которая содержится в файлах UCF и NCF (Netlist Constraints File). Результатом фазы трансляции является формирование логического описания проекта в терминах примитивов Xilinx низкого уровня с учетом временных и топологических ограничений, выполненного в формате NGD (Native Generic Database). На второй стадии рассматриваемого этапа производится разбиение логического описания проекта, полученного на предыдущем шаге, на блоки в соответствии с ресурсами выбранного типа ПЛИС. При этом выполняется оптимизация с целью минимизации используемых (необходимых) ресурсов кристалла с учетом заданных ограничений. В результате выполнения процесса размещения и трассировки создается двоичный файл, который описывает использование физических ресурсов кристалла для реализации функций проектируемого устройства.

Этап реализации (Implementation) проектов, выполняемых на базе ПЛИС семейств FPGA, включает в себя три фазы: трансляции (Translate), отображения логического описания проекта на физические ресурсы кристалла (MAP), размещения и трассировки (Place and Route). В процессе трансляции выполняется объединение всех списков соединений в формате EDIF, входящих в состав проекта, и информации обо всех ограничениях, которая содержится в файлах UCF (User Constraints File) и NCF (Netlist Constraints File). Результатом фазы трансляции является формирование логического описания проекта в терминах примитивов Xilinx низкого уровня с учетом временных и топологических ограничений, выполненного в формате NGD (Native Generic Database). На второй стадии рассматриваемого этапа логическое описание проекта, полученное на предыдущем шаге, проецируется на физические ресурсы выбранного типа ПЛИС. При этом выполняется оптимизация в соответствии с выбранным критерием и заданными ограничениями. В процессе размещения и трассировки выбирается наилучшее расположение конфигурируемых логических блоков, реализующих соответствующие функции проекта, и выполняются необходимые соединения с учетом временных и топологических ограничений.

В результате выполнения рассматриваемого этапа создается двоичный файл, который описывает использование физических ресурсов кристалла для реализации элементов (функций) проектируемого устройства и выполнения необходимых соединений между ними. Этот файл затем используется в качестве исходного для генерации конфигурационной последовательности.

В процессе проектирования средства пакета WebPACK ISE позволяют сформировать несколько видов моделей разрабатываемого устройства. После создания модулей исходного описания проекта генерируется поведенческая модель, которая позволяет выполнить их функциональную верификацию. На этой стадии проектирования отсутствует информация о значениях задержек распространения сигналов, поэтому при функциональном моделировании можно обнаружить только логические и синтаксические ошибки в описании разрабатываемого устройства. Таким образом, функциональное моделирование устройства позволяет выполнить предварительную верификацию проекта. На этом этапе фактически не учитываются временные характеристики и особенности архитектуры кристалла, на базе которого предполагается реализация проектируемой системы. Часто в литературе этот процесс называют моделированием на уровне регистровых передач (Register Transfer Level, RTL). Для функционального моделирования проекта используется библиотека UniSim Library, элементы которой имеют единичные задержки.

Состав моделей, формируемых на последующих этапах процесса проектирования, зависит от типа семейства ПЛИС (FPGA или CPLD), выбранного для реализации разрабатываемого устройства. Только после проведения этапов синтеза, размещения и трассировки становится доступной информация об используемых ресурсах кристалла и задержках распространения сигналов, которая необходима для формирования более адекватной модели. В отличие от функционального последующие этапы моделирования выполняются с применением библиотеки SimPrim Library, которая содержит описание элементов на уровне ресурсов кристалла. Эта библиотека позволяет учитывать информацию о задержках распространения сигналов, которая содержится в соответствующих файлах, имеющих стандартный формат SDF (Standard Delay Format). Так как содержание этапа реализации (Implementation) коренным образом отличается для семейств CPLD и FPGA, что обусловлено их архитектурными особенностями, то процесс генерации моделей, учитывающих временные характеристики используемых кристаллов, включает в себя различные фазы, в зависимости от выбранного типа ПЛИС. Для проектов, выполняемых на основе ПЛИС семейств CPLD, кроме функциональной модели может быть сформирована только полная временная модель устройства. Таким образом, процесс проектирования систем на базе кристаллов семейств CPLD включает в себя два этапа моделирования: функционального и полного временного. В процессе проектирования устройств на базе кристаллов семейств FPGA разработчику предоставляется возможность проведения моделирования на следующих стадиях:

после создания исходных описаний проекта (Simulate Behavioral VHDL Model);

после выполнения этапов синтеза и трансляции (Simulate Post-Translate VHDL Model);

после выполнения фазы отображения логического описания проекта на физические ресурсы кристалла (Simulate Post-Map VHDL Model);

после завершения процедур размещения и трассировки (Simulate Post-Place & Route VHDL Model).

Такая организация позволяет обнаружить возможные ошибки на более раннем шаге проектирования, и, тем самым, избежать значительных временных потерь. Уровень сложности проектов, выполняемых на базе ПЛИС семейств FPGA, как правило, более высок по сравнению с проектами, разрабатываемыми на основе кристаллов CPLD. Поэтому этапы синтеза и реализации с учетом проводимой оптимизации требуют больших временных затрат.

Все виды моделирования цифровых устройств, разрабатываемых в среде САПР WebPACK ISE, выполняются с помощью системы HDL-моделирования ModelSim.

Прежде чем приступать непосредственно к выполнению этапов моделирования, необходимо сформировать файл описаний тестовых воздействий, если он не был подготовлен на этапе создания исходных модулей проекта.

При этом средствами пакета WebPACK ISE автоматически создастся пакетный файл, который содержит последовательность команд управления программой ModelSim, необходимых для проведения сеанса функционального моделирования проектируемого устройства. Далее автоматически производится запуск средств моделирования, сразу после инициализации которых, выполняется этот командный файл.

Литература

1. Максфилд Клайв. Проектирование на ПЛИС. Архитектура, средства и методы. М.: Издательский дом «Додека» 2007. 408 с., ил.

2. Зотов В.Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС XILINX. М.: Горячая линия Телеком, 2006. 520 с., ил.

3. Система синтаксического и семантического контроля VHDL-описаний “VHDL-анализатор”. Руководство пользователя. М.: РосНИИИС, 1991. 112 с.

Воронежский государственный технический университет

УДК 621.3.037

Е.Н. Циблиев, В.С. Скоробогатов, Ю.М. Данилов

ГЕРМЕТИЗАЦИЯ ТРАНЗИСТОРОВ ХОЛОДНОЙ СВАРКОЙ

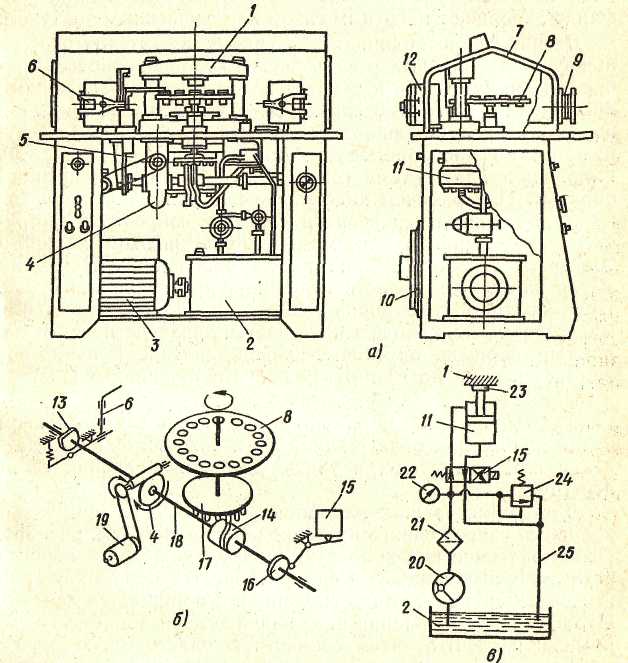

Представлен процесс герметизация транзисторов холодной сваркой

Надежность полупроводниковых приборов и интегральных микросхем при работе в аппаратуре и хранении в значительной степени зависит от герметичности корпуса.

Герметизация — одна из завершающих операций технологического процесса производства полупроводниковых приборов, так как обеспечивает их долголетнюю работу при механических и климатических воздействиях. Кроме того, она является последней операцией сборки полупроводниковых приборов, от качества которой зависит выход годных изделий.

Постоянное стремление к повышению компактности, миниатюризации и быстродействию электронных систем вызывает увеличение плотности рассеиваемой мощности (особенно в микросхемах), что усложняет теплоотвод от активных компонентов и предъявляет дополнительные требования к конструкции корпусов и способам их герметизации.