- •Основы микропроцессорной техники

- •В.И. Енин

- •В.И. Енин

- •Введение

- •После изучения дисциплины необходимо знать

- •После изучения дисциплины необходимо уметь

- •В.1. Роль и место курса “Микропроцессорная техника” в учебном процессе

- •1. Микропрограммные автоматы

- •После изучения главы необходимо знать

- •1.1. Автомат без памяти

- •1.2. Микропрограммный автомат

- •1.2.1. Автомат с памятью

- •1.2.2. Микропрограммный автомат в системе управления

- •1.2.3. Структурный автомат

- •1.3. Схемная реализация микропрограммных автоматов

- •2. МикропрограмМируемые контроллеры и микропроцессоры

- •После изучения главы необходимо знать

- •2.1. Блок микропрограммного управления

- •2.2. Блок обработки цифровых данных.

- •3. Принципы организации эвм

- •После изучения главы необходимо знать

- •3.1. Выполнение команд в эвм

- •Система команд и методы адресации

- •Подпрограммы

- •3.2. Общие принципы организации ввода-вывода

- •3.2.1. Программный режим ввода-вывода

- •3.2.2. Обмен информацией в режиме прерывания программы

- •3.2.3. Прямой доступ к памяти

- •3.2.4. Подключение внешних устройств

- •4. Архитектура однокристального микропроцессора

- •После изучения главы необходимо знать

- •4.1. Архитектура микропроцессора к580ик80а

- •4.1.1. Формат команд микропроцессора к580ик80а

- •4.1.2. Методы адресации микропроцессора к580ик80а

- •4.1.3. Команды безусловной и условной передач управления

- •4.1.4. Примеры команд процессора к580ик80а

- •4.2. Организация обмена в однокристальных микроЭвм

- •4.2.1. Функционирование микропроцессора

- •4.2.2. Подключение озу и регистров внешних устройств

- •5. Системы счисления и арифметические операции над числами

- •После изучения главы необходимо знать

- •5.1. Системы счисления для представления чисел в эвм

- •5.2. Представление в эвм целых двоичных чисел без знака

- •5.3. Представление в эвм целых чисел со знаком

- •5.3.1. Представление чисел со знаком в прямом коде

- •5.3.2. Представление чисел со знаком в дополнительном коде

- •5.3.3. Особенности выполнения сложения двоичных чисел без знака и со знаком

- •1. Примеры сложения чисел без знака.

- •2. Примеры сложения чисел со знаком.

- •5.4. Двоично-десятичная система представления чисел

- •5.5. Представление чисел в формате с плавающей точкой

- •Примеры представления чисел типа single

- •Примеры представления чисел типа real

- •6. Семейство процессоров х86

- •После изучения главы необходимо знать

- •6.1. Архитектура процессора 8086

- •Регистры процессора

- •Инструкции процессора

- •Сегментация памяти

- •Методы адресации

- •Распределение памяти

- •Прерывания

- •Функционирование

- •6.2. Процессоры 80286

- •Реальный режим

- •Защищенный режим

- •Прерывания

- •Регистр состояния задачи

- •Некоторые особенности функционирования

- •Функциональная схема pc at

- •7. Шина isa и интерфейсы сопряжения с устройствами управления

- •После изучения главы необходимо знать

- •7.1. Конструкция шины isa

- •Выводы шины isa

- •Распределение адресов на системной плате ат

- •Циклы магистрали

- •Прямой доступ к памяти

- •Регенерация памяти

- •Основные электрические характеристики линий isa

- •7.2. Проектирование устройств сопряжения для шины isa

- •7.2.1. Селекторы (дешифраторы) адреса

- •7.2.2. Операционная часть интерфейса

- •7.2.3. Микросхемы для построения интерфейсов Условные графические обозначения элементов цифровой техники

- •7.2.4. Микросхемы приемопередатчиков сигналов магистрали

- •Микросхемы селекторов адреса выходных регистров

- •8. Интерфейс centronics

- •После изучения главы необходимо знать

- •8.1. Порядок обмена по интерфейсу Centronics

- •8.2. Программируемый параллельный интерфейс ( ппи)

- •9. Обмен данными по интерфейсу rs-232

- •После изучения главы необходимо знать

- •9.1. Назначение линий связи rs-232

- •9.2. Подключение модема к rs-232

- •9.3. Подключение терминалов к rs-232

- •9.4. Подключение удаленных объектов управления

- •9.5. Назначение портов rs-232

- •10. Отсчёт реального времени в эвм

- •После изучения главы необходимо знать

- •10.1. Программируемый таймер

- •10.1.1. Режимы работы таймера

- •10.1.2. Таймер на системной плате ibm pc

- •10.2. Программируемый контроллер прерываний

- •10.2.1. Режимы работы пкп

- •10.2.2. Программирование пкп

- •10.3. Прерывания в ibm pc

- •10.3.1. Векторы прерывания

- •10.3.2. Прерывания bios и dos

- •10.3.3. Написание собственных прерываний

- •10.4. Отсчёт реального времени в эвм

- •10.5. Процедуры и функции для работы с прерываниями

- •После изучения главы необходимо знать

- •11.1. Архитектура 32-разрядных процессоров

- •11.1.1. Регистры процессора

- •11.1.2. Организация памяти

- •11.1.3. Режимы адресации

- •11.1.4. Ввод и вывод

- •11.1.5. Прерывания и исключения

- •11.1.6. Процессоры Pentium

- •11.2. Страничное управление памятью

- •11.3. Кэширование памяти

- •Кэш прямого отображения

- •Ассоциативный кэш

- •12. Однокристальные микроконтроллеры

- •После изучения главы необходимо знать

- •12.1. Однокристальный микроконтроллер к1816

- •12.2. Avr микроконтроллеры

- •12.3. Процессоры обработки сигналов

- •12.3.1. Однокристальный цифровой процессор обработки

- •12.3.2. Цифровые процессоры обработки сигналов (цпос)

- •13. Промышленное оборудование для цифровых систем управления

- •После изучения главы необходимо знать

- •13.1. Оборудование для централизованных систем управления

- •13.1.1. Персональные компьютеры для целей управления

- •13.1.2. Промышленные рабочие станции

- •13.1.3. Шасси для ibm совместимых промышленных компьютеров

- •13.1.4. Модульные промышленные компьютеры mic-2000

- •13.1.5. Процессорные платы

- •13.1.6. Устройства для сбора данных и управления

- •13.2. Оборудование для распределенных систем сбора данных и управления

- •13.2.1. Модули удаленного сбора данных и управления adam-5000

- •13.2.2. Модули удаленного сбора данных и управления adam-4000

- •13.3. Прикладное программное обеспечение

- •Заключение

- •Список использованных источников

- •Оглавление

- •Системы счисления и арифметические

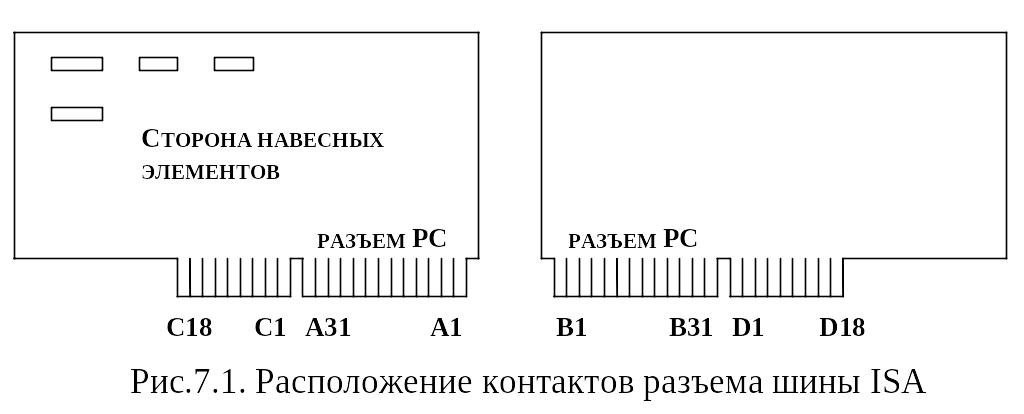

7.1. Конструкция шины isa

Выводы шины isa

Отметим основные сигналы шины, определяющие структуру интерфейса. В квадратных скобках приведены номера контактов. Черта над названием сигнала означает, что активному состоянию сигнала соответствует низкий уровень.

SA0 - SA19 [A31-A12]- фиксируемые адресные разряды (20 линий для адресации 1Мбайта памяти). Защелкивание адреса идет по падающему фронту сигнала BALE. Сигналы действительны в течении всего цикла обмена. Они используются и для адресации устройств ввода-вывода (SA0-SA15), в действительности используются SA0-SA9. Значительная часть этих адресов занята стандартными устройствами компьютера. Логика всех сигналов положительная. В режиме MASTER эти сигналы вырабатывает устройство, захватившее магистраль. Тип выходного каскада - каскад с 3 состояниями.

L A17

- LA23

[C8-C2]

- не фиксируемые адресные разряды.

Используются для адресации памяти и

выработки сигнала MEM

CS

16 . Действительны только в начале цикла

обмена. Исполнитель должен фиксировать

их по отрицательному фронту сигнала

BALE.

При обращении к устройствам вводa-вывода

имеют уровень логического нуля. Для

фиксации необходимо использовать

регистр типа "защелка" (КР1533ИР23,

К555ИР22). При прямом доступе к памяти эти

сигналы действительны в течение всего

цикла обмена. Сигнал вырабатывает

устройство MASTER.

Тип выходного каскада - каскад с 3

состояниями.

A17

- LA23

[C8-C2]

- не фиксируемые адресные разряды.

Используются для адресации памяти и

выработки сигнала MEM

CS

16 . Действительны только в начале цикла

обмена. Исполнитель должен фиксировать

их по отрицательному фронту сигнала

BALE.

При обращении к устройствам вводa-вывода

имеют уровень логического нуля. Для

фиксации необходимо использовать

регистр типа "защелка" (КР1533ИР23,

К555ИР22). При прямом доступе к памяти эти

сигналы действительны в течение всего

цикла обмена. Сигнал вырабатывает

устройство MASTER.

Тип выходного каскада - каскад с 3

состояниями.

BALE [B28] (Bus Address Latch Enable) - выходной сигнал разрешения защелкивания адреса, т.е. сигнал стробирования адресных разрядов. Его отрицательный фронт соответствует действительности адреса на линиях SA0 - SA23. Высокий уровень показывает, что адрес на системной шине сформирован. Это буферизированный вариант сигнала GATE ALE. Тип выходного каскада - TTL.

S BHE

[C1]

(System

Bus

High

Enable)-

разрешение старшего байта. Сигнал

определяет тип передачи данных (8 или

16- разрядный), вырабатывается параллельно

с SA0-SA19

и может рассматриваться как дополнительный

разряд адреса. Он активен при передаче

старшего байта или 16-разрядного слова.

Вырабатывается устройством MASTER,

т.е. устройством, захватившим магистраль.

Выходной каскад имеет 3 состояния. Это

буферизированный вариант сигнала BHE

процессора, который совместно с разрядом

адреса А0 указывает на одну из 3 ситуаций

при передаче данных.

BHE

[C1]

(System

Bus

High

Enable)-

разрешение старшего байта. Сигнал

определяет тип передачи данных (8 или

16- разрядный), вырабатывается параллельно

с SA0-SA19

и может рассматриваться как дополнительный

разряд адреса. Он активен при передаче

старшего байта или 16-разрядного слова.

Вырабатывается устройством MASTER,

т.е. устройством, захватившим магистраль.

Выходной каскад имеет 3 состояния. Это

буферизированный вариант сигнала BHE

процессора, который совместно с разрядом

адреса А0 указывает на одну из 3 ситуаций

при передаче данных.

-

SBHE

A0

передача

0

0

перенос слова

0

1

перенос байта по верхней половине шины

1

0

перенос байта по нижней половине шины

1

1

не используется

SD0-SD7 [A9-A2] - линии передачи младшего байта; логика положительная; выходной каскад имеет 3 состояния

SD8-SD15[C11-C18] - линии передачи старшего байта; логика положительная; выходной каскад имеет 3 состояния

SD0 - SD15 - шина данных; при обмене с Х шиной шириной 8 бит происходит передача на Х шину как с верхней, так и с нижней половины S-шины, что достигается коммутацией.

S

MEMR[B12],

MEMR[C9]

(Memory

Read)

- стробы чтения данных из памяти

формируются шинным контроллером и

информируют о чтении слова или байта

из памяти. Первый сигнал вырабатывается

только при обращении к адресам не

превышающим FFFFF

(1Мбайт), второй- ко всем адресам. В ответ

на этот сигнал память выставляет данные.

Вырабатывается устройством MASTER,

захватившим шину. Выходной каскад имеет

3 состояния.

MEMR[B12],

MEMR[C9]

(Memory

Read)

- стробы чтения данных из памяти

формируются шинным контроллером и

информируют о чтении слова или байта

из памяти. Первый сигнал вырабатывается

только при обращении к адресам не

превышающим FFFFF

(1Мбайт), второй- ко всем адресам. В ответ

на этот сигнал память выставляет данные.

Вырабатывается устройством MASTER,

захватившим шину. Выходной каскад имеет

3 состояния.

S MEMW[B11],

MEMW[C10]

(Memory

Write)-

стробы записи в память, исходят от

шинного контроллера и информируют о

записи слова или байта в память. Память

принимает данные по положительному

заднему фронту сигнала. Первый сигнал

используется при обращении к первому

мегабайту ОЗУ .

MEMW[B11],

MEMW[C10]

(Memory

Write)-

стробы записи в память, исходят от

шинного контроллера и информируют о

записи слова или байта в память. Память

принимает данные по положительному

заднему фронту сигнала. Первый сигнал

используется при обращении к первому

мегабайту ОЗУ .

I OR[B14]

(I/O

Read)

-строб чтения данных из устройств

ввода-вывода. адрес

порта находится на линиях SA0-SA15.

Устройство должно выставлять свои

данные при активизации сигнала и снимать

при его снятии.

OR[B14]

(I/O

Read)

-строб чтения данных из устройств

ввода-вывода. адрес

порта находится на линиях SA0-SA15.

Устройство должно выставлять свои

данные при активизации сигнала и снимать

при его снятии.

I OW

[B13](I/O

Write)- строб записи данных в устройство

ввода-вывода Устройство должно принимать

данные по положительному (заднему)

фронту сигнала. В линиях IOR,

IOW

тип выходного каскада - каскад с 3

состояниями и сигналы вырабатывает

устройство, захватившее магистраль

(MASTER).

OW

[B13](I/O

Write)- строб записи данных в устройство

ввода-вывода Устройство должно принимать

данные по положительному (заднему)

фронту сигнала. В линиях IOR,

IOW

тип выходного каскада - каскад с 3

состояниями и сигналы вырабатывает

устройство, захватившее магистраль

(MASTER).

M EM

CS16 [D1]

(Memory Cycle Select)-

выбор

цикла

из

памяти.

Сигнал

выставляется памятью для сообщения

задатчику, что она имеет 16-разрядную

организацию. При отсутствии сигнала

выполняется 8-разрядный обмен. Сигнал

вырабатывается при распознавании

памятью своего адреса на линиях LA17-LA23.

Процессор фиксирует его по заднему

фронту сигнала BALE.

Выходной каскад имеет открытый коллектор.

EM

CS16 [D1]

(Memory Cycle Select)-

выбор

цикла

из

памяти.

Сигнал

выставляется памятью для сообщения

задатчику, что она имеет 16-разрядную

организацию. При отсутствии сигнала

выполняется 8-разрядный обмен. Сигнал

вырабатывается при распознавании

памятью своего адреса на линиях LA17-LA23.

Процессор фиксирует его по заднему

фронту сигнала BALE.

Выходной каскад имеет открытый коллектор.

I /O

CS16

[D2]

(I/O

Cycle

Select)

- выбор цикла для устройства ввода-вывода.

Сигнал используется для сообщения

задатчику, что устройство имеет 16

разрядную организацию При отсутствии

сигнала выполняется 8-разрядный обмен.

Сигнал вырабатывается при распознавании

своего адреса на линиях SA0-SA15.

Выходной каскад имеет открытый коллектор.

/O

CS16

[D2]

(I/O

Cycle

Select)

- выбор цикла для устройства ввода-вывода.

Сигнал используется для сообщения

задатчику, что устройство имеет 16

разрядную организацию При отсутствии

сигнала выполняется 8-разрядный обмен.

Сигнал вырабатывается при распознавании

своего адреса на линиях SA0-SA15.

Выходной каскад имеет открытый коллектор.

I/O CH RDY [A10] (I/O Channel Ready) -готовность канала ввода-вывода и устанавливается равным 0 (не готов) для увеличения цикла обмена. Сигнал снимается (делается низким) устройством ввода-вывода по переднему фронту сигналов IOR, IOW , если оно не успевает выполнить требуемую операцию в темпе задатчика. При этом реализуется асинхронный обмен. Если исполнитель успевает работать в темпе задатчика, сигнал не снимается (не устанавливается в низкий уровень). Цикл обмена в ответ на снятие сигнала продлевается на целое число периодов сигнала SYSCLK. Сигнал не должен сниматься на время большее заданного в компьютере (по стандарту 15мксек, по другим данным 2.5 мксек, т. е. 30 циклов CLK) во избежание немаскируемого прерывания по отсутствию регенерации. Выходной каскад имеет открытый коллектор.

I /O

CH

CK

[A1](I/O

Channel

Check)-

проверка канала ввода-вывода. Сигнал

вырабатывается любым исполнителем

(устройством ввода-вывода или памятью)

для информирования задатчика о фатальной

ошибке (например, ошибки четности при

обращении к памяти). Сигнал вызывает

немаскируемое прерывание. Выходной

каскад имеет открытый коллектор.

/O

CH

CK

[A1](I/O

Channel

Check)-

проверка канала ввода-вывода. Сигнал

вырабатывается любым исполнителем

(устройством ввода-вывода или памятью)

для информирования задатчика о фатальной

ошибке (например, ошибки четности при

обращении к памяти). Сигнал вызывает

немаскируемое прерывание. Выходной

каскад имеет открытый коллектор.

0 WS [B8] ( 0 Wait States) - 0 тактов ожидания. Сигнал формируется и выставляется исполнителем (адаптером периферийного устройства) для информирования задатчика о необходимости проведения цикла обмена без вставки такта ожидания, если длительность стандартного цикла обмена велика для него. Вырабатывается после перехода сигнала BALE в низкий уровень. Сигнал OWS должен быть синхронизован с SYSCLK. Он используется редко. Выходной каскад имеет открытый коллектор.

R EFRESH

[B19]-регенерация.

Сигнал выставляется контроллером

регенерации для информирования всех

устройств магистрали о выполнении

циклов регенерации динамического ОЗУ

(каждые 15мксек). При регенерации

выполняется псевдочтение одного из 256

адресов ОЗУ (активизируются только

разряды SA0-SA7).

Полный цикл регенерации- 4мсек. Выходной

каскад- открытый коллектор.

EFRESH

[B19]-регенерация.

Сигнал выставляется контроллером

регенерации для информирования всех

устройств магистрали о выполнении

циклов регенерации динамического ОЗУ

(каждые 15мксек). При регенерации

выполняется псевдочтение одного из 256

адресов ОЗУ (активизируются только

разряды SA0-SA7).

Полный цикл регенерации- 4мсек. Выходной

каскад- открытый коллектор.

RESET DRV [B2] (Reset of Driver)- сброс устройства (буферизированный сигнал RESET). Сигнал сброса всех устройств магистрали. Вырабатывается ЦП при включении или при сбое питания. Внешние платы в ответ на этот сигнал (длительностью 1мсек) должны перевести свои выходы в высокоимпендансное состояние. Тип выходного каскада -TTL.

SYSCLK [B20] (System Clock) - сигнал системного тактового генератора со скважностью 2 (меандр). В большинстве компьютеров его частота равна 8Мгц, независимо от тактовой частоты процессора. Если в программе SETUP предусмотрена возможность изменения тактовой частоты, то пользователь может задавать ее в широких пределах. Но для совместимости с имеющимися платами расширения ее нежелательно повышать ее выше 8Мгц. Выходной каскад имеет 3 состояния.

OSC [B30] - не синхронизированный с SYSCLK сигнал кварцевого генератора с частотой 14.311818 и скважностью 2, одинаковый для всех компьютеров. Может использоваться в расширениях как тактовый сигнал. Выходной каскад -TTL-совместимый.

IRQ (Interrupt Request)- группа линий запроса прерывания. Запросом является положительный переход на соответствующей линии IRQ. Сигнал должен удерживаться до начала обработки процессором запрашиваемого прерывания. Выходной каскад - TTL. На каждой линии должен быть один выход (лучше с 3 состояниями). Многие входы IRQ заняты системными ресурсами. Сигналы IRQ0...IRQ2, IRQ8,IRQ13 заняты в системной плате и недоступны платам расширения. В компьютерах используются 2 контроллера прерываний (IRQ0-IRQ7, IRQ8-IRQ15). Вход IRQ2 задействован для каскадирования контроллеров прерывания. Поэтому приоритеты распределены в порядке возрастания: IRQ7 ... IRQ3, IRQ15, IRQ14, IRQ12... IRQ9. Заметим, что большинство линий заняты устройствами, входящими в ЭВМ, и пользователь для своих расширений реально может использовать только линии IRQ10, IRQ11, IRQ12, IRQ15.

IRQ |

Конт. |

IRQ |

Конт. |

IRQ3 |

B25 |

IRQ10 |

D3 |

IRQ4 |

B24 |

IRQ11 |

D4 |

IRQ5 |

B23 |

IRQ12 |

D5 |

IRQ6 |

B22 |

IRQ14 |

D7 |

IRQ7 |

B21 |

IRQ15 |

D5 |

IRQ9 |

B4 |

|

|

Номера некоторых аппаратных прерываний шины ISA:

-

Номер прерывания IRQ

INT

Назначение

0

08h

Программируемый таймер

1

09h

Контроллер клавиатуры

8

70h

Часы реального времени

13

75h

Математический сопроцессор

3

0Ch

Последовательный порт COM1

6

0Eh

Контроллер гибкого диска

7

0Fh

Параллельный порт LPT1

DRQ |

Конт. |

DRQ0 |

D9 |

DRQ2 |

B6 |

DRQ3 |

B16 |

DRQ5 |

D11 |

DRQ6 |

D13 |

DRQ7 |

D15 |

DACK |

Конт. |

DACK1 |

B17 |

DACK2 |

B26 |

DACK3 |

B15 |

DACK0 |

D8 |

DACK5 |

D10 |

DACK6 |

D12 |

DACK7 |

D14 |

ACK

(DMA

Acknowledge)

- группа линий подтверждения ПДП. Сигналы

подтверждения прерывания вырабатываются

в ответ на соответствующий сигнал DRQ,

если прямой доступ предоставлен данному

каналу. Сигнал удерживается до окончания

прямого доступа. Выходной каскад - TTL.

ACK

(DMA

Acknowledge)

- группа линий подтверждения ПДП. Сигналы

подтверждения прерывания вырабатываются

в ответ на соответствующий сигнал DRQ,

если прямой доступ предоставлен данному

каналу. Сигнал удерживается до окончания

прямого доступа. Выходной каскад - TTL.

AEN [A11] (Address Enable)- разрешение адреса. Используется в режиме ПДП для сообщения всем платам расширения, что производится цикл ПДП. Устанавливается и снимается параллельно с адресом. При его переходе в активное состояние все платы расширения, не участвующие в данном ПДП, должны отключиться. Выходной каскад - TTL.

T/C [B27]- (Terminal Count) - окончание счета. Устанавливается в режиме ПДП, когда по текущему каналу ПДП закончен счет циклов пересылки данных. Тип выходного каскада - TTL.

M

ASTER

- мастер, задатчик. Используется платой

расширения желающей стать задатчиком

магистрали (например, для организации

многопроцессорных систем). Выходной

каскад - открытый коллектор. Порядок

установки сигнала: выставить сигнал

DRQ

и в ответ на DACK

установить сигнал MASTER.

Через 1 период SYSCLK

выставить адрес и через 2 периода

выставлять стробы обмена.

ASTER

- мастер, задатчик. Используется платой

расширения желающей стать задатчиком

магистрали (например, для организации

многопроцессорных систем). Выходной

каскад - открытый коллектор. Порядок

установки сигнала: выставить сигнал

DRQ

и в ответ на DACK

установить сигнал MASTER.

Через 1 период SYSCLK

выставить адрес и через 2 периода

выставлять стробы обмена.

В шине имеются выходы источника питания для плат расширения. Стандартом магистрали предусмотрено максимальное значение тока, потребляемого каждой платой. Ток определяется нагрузкой разъема. Суммарный ток потребления от источника питания определяется его мощностью и для 200-ваттного источника приведен в таблице 7.1.

Максимальная допустимая нагрузка Табл. 7.1.

Напряжение питания |

+5 |

-5 |

+12 |

-12 |

Общий |

Максимальный ток платы |

3а |

1.5а |

1.5а |

1.5а |

|

Суммарный ток |

7-19а |

0.3а |

2.5-7а |

0.3а |

|

Контакты |

D16, B29, B3 |

B5 |

B9 |

B7 |

D18, B31, B1 |

Источники имеют защиту от перенапряжения с временем включения 20 мсек. Источник должен быть обязательно нагружен по напряжению +5в и +12в. Если по ним не будет обеспечен минимальный ток, то это воспринимается как перегрузка. Для выхода из перегрузки надо выключить питание и включить его через время большее 1 сек.