- •Основы микропроцессорной техники

- •В.И. Енин

- •В.И. Енин

- •Введение

- •После изучения дисциплины необходимо знать

- •После изучения дисциплины необходимо уметь

- •В.1. Роль и место курса “Микропроцессорная техника” в учебном процессе

- •1. Микропрограммные автоматы

- •После изучения главы необходимо знать

- •1.1. Автомат без памяти

- •1.2. Микропрограммный автомат

- •1.2.1. Автомат с памятью

- •1.2.2. Микропрограммный автомат в системе управления

- •1.2.3. Структурный автомат

- •1.3. Схемная реализация микропрограммных автоматов

- •2. МикропрограмМируемые контроллеры и микропроцессоры

- •После изучения главы необходимо знать

- •2.1. Блок микропрограммного управления

- •2.2. Блок обработки цифровых данных.

- •3. Принципы организации эвм

- •После изучения главы необходимо знать

- •3.1. Выполнение команд в эвм

- •Система команд и методы адресации

- •Подпрограммы

- •3.2. Общие принципы организации ввода-вывода

- •3.2.1. Программный режим ввода-вывода

- •3.2.2. Обмен информацией в режиме прерывания программы

- •3.2.3. Прямой доступ к памяти

- •3.2.4. Подключение внешних устройств

- •4. Архитектура однокристального микропроцессора

- •После изучения главы необходимо знать

- •4.1. Архитектура микропроцессора к580ик80а

- •4.1.1. Формат команд микропроцессора к580ик80а

- •4.1.2. Методы адресации микропроцессора к580ик80а

- •4.1.3. Команды безусловной и условной передач управления

- •4.1.4. Примеры команд процессора к580ик80а

- •4.2. Организация обмена в однокристальных микроЭвм

- •4.2.1. Функционирование микропроцессора

- •4.2.2. Подключение озу и регистров внешних устройств

- •5. Системы счисления и арифметические операции над числами

- •После изучения главы необходимо знать

- •5.1. Системы счисления для представления чисел в эвм

- •5.2. Представление в эвм целых двоичных чисел без знака

- •5.3. Представление в эвм целых чисел со знаком

- •5.3.1. Представление чисел со знаком в прямом коде

- •5.3.2. Представление чисел со знаком в дополнительном коде

- •5.3.3. Особенности выполнения сложения двоичных чисел без знака и со знаком

- •1. Примеры сложения чисел без знака.

- •2. Примеры сложения чисел со знаком.

- •5.4. Двоично-десятичная система представления чисел

- •5.5. Представление чисел в формате с плавающей точкой

- •Примеры представления чисел типа single

- •Примеры представления чисел типа real

- •6. Семейство процессоров х86

- •После изучения главы необходимо знать

- •6.1. Архитектура процессора 8086

- •Регистры процессора

- •Инструкции процессора

- •Сегментация памяти

- •Методы адресации

- •Распределение памяти

- •Прерывания

- •Функционирование

- •6.2. Процессоры 80286

- •Реальный режим

- •Защищенный режим

- •Прерывания

- •Регистр состояния задачи

- •Некоторые особенности функционирования

- •Функциональная схема pc at

- •7. Шина isa и интерфейсы сопряжения с устройствами управления

- •После изучения главы необходимо знать

- •7.1. Конструкция шины isa

- •Выводы шины isa

- •Распределение адресов на системной плате ат

- •Циклы магистрали

- •Прямой доступ к памяти

- •Регенерация памяти

- •Основные электрические характеристики линий isa

- •7.2. Проектирование устройств сопряжения для шины isa

- •7.2.1. Селекторы (дешифраторы) адреса

- •7.2.2. Операционная часть интерфейса

- •7.2.3. Микросхемы для построения интерфейсов Условные графические обозначения элементов цифровой техники

- •7.2.4. Микросхемы приемопередатчиков сигналов магистрали

- •Микросхемы селекторов адреса выходных регистров

- •8. Интерфейс centronics

- •После изучения главы необходимо знать

- •8.1. Порядок обмена по интерфейсу Centronics

- •8.2. Программируемый параллельный интерфейс ( ппи)

- •9. Обмен данными по интерфейсу rs-232

- •После изучения главы необходимо знать

- •9.1. Назначение линий связи rs-232

- •9.2. Подключение модема к rs-232

- •9.3. Подключение терминалов к rs-232

- •9.4. Подключение удаленных объектов управления

- •9.5. Назначение портов rs-232

- •10. Отсчёт реального времени в эвм

- •После изучения главы необходимо знать

- •10.1. Программируемый таймер

- •10.1.1. Режимы работы таймера

- •10.1.2. Таймер на системной плате ibm pc

- •10.2. Программируемый контроллер прерываний

- •10.2.1. Режимы работы пкп

- •10.2.2. Программирование пкп

- •10.3. Прерывания в ibm pc

- •10.3.1. Векторы прерывания

- •10.3.2. Прерывания bios и dos

- •10.3.3. Написание собственных прерываний

- •10.4. Отсчёт реального времени в эвм

- •10.5. Процедуры и функции для работы с прерываниями

- •После изучения главы необходимо знать

- •11.1. Архитектура 32-разрядных процессоров

- •11.1.1. Регистры процессора

- •11.1.2. Организация памяти

- •11.1.3. Режимы адресации

- •11.1.4. Ввод и вывод

- •11.1.5. Прерывания и исключения

- •11.1.6. Процессоры Pentium

- •11.2. Страничное управление памятью

- •11.3. Кэширование памяти

- •Кэш прямого отображения

- •Ассоциативный кэш

- •12. Однокристальные микроконтроллеры

- •После изучения главы необходимо знать

- •12.1. Однокристальный микроконтроллер к1816

- •12.2. Avr микроконтроллеры

- •12.3. Процессоры обработки сигналов

- •12.3.1. Однокристальный цифровой процессор обработки

- •12.3.2. Цифровые процессоры обработки сигналов (цпос)

- •13. Промышленное оборудование для цифровых систем управления

- •После изучения главы необходимо знать

- •13.1. Оборудование для централизованных систем управления

- •13.1.1. Персональные компьютеры для целей управления

- •13.1.2. Промышленные рабочие станции

- •13.1.3. Шасси для ibm совместимых промышленных компьютеров

- •13.1.4. Модульные промышленные компьютеры mic-2000

- •13.1.5. Процессорные платы

- •13.1.6. Устройства для сбора данных и управления

- •13.2. Оборудование для распределенных систем сбора данных и управления

- •13.2.1. Модули удаленного сбора данных и управления adam-5000

- •13.2.2. Модули удаленного сбора данных и управления adam-4000

- •13.3. Прикладное программное обеспечение

- •Заключение

- •Список использованных источников

- •Оглавление

- •Системы счисления и арифметические

4.2.2. Подключение озу и регистров внешних устройств

Структура интерфейсов для подключения к процессору К580 ОЗУ и внешних устройств целиком определяется протоколом обмена, т.е. системой сигналов в шинах адреса, данных, управления и их временными соотношениями, определяемыми тактами функционирования процессора.

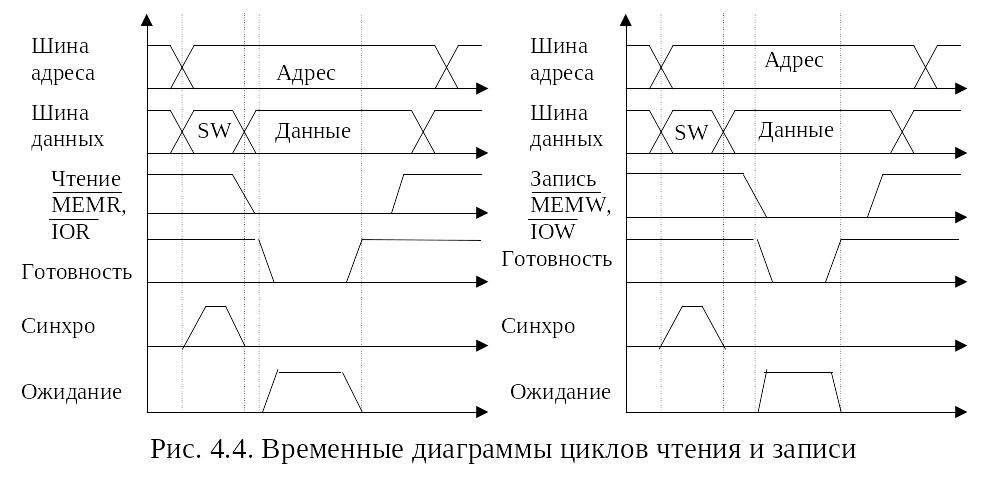

Временные диаграммы циклов чтения и записи (Рис.4.4) содержат только основные сигналы шин, определяющие структуру интерфейса. Они являются базовыми для всех процессоров, имеющих раздельные шины адреса, данных и управления.

В соответствии с приведенными временными диаграммами подключение ОЗУ в системе с раздельными шинами адреса и данных реализуется по функциональной схеме представленной на рис 4.5.

Старшая часть адреса через приемник поступает на дешифратор, который вырабатывает сигнал "устройство выбрано", если адрес совпадает с адресом устройства (блока памяти ОЗУ). Результат дешифрации поступает на вход выбор кристалла микросхемы памяти. Младшая часть адреса поступает на адресный вход ОЗУ, выбирая одну из ячеек памяти. Вход данных ОЗУ (желательно через буфер) подключен к шине данных.

В цикле

запись процессор выставляет адрес и

данные, затем вырабатывает импульсный

сигнал "запись в память" (MEMW)

и данные записываются в ячейку по заднему

фронту импульса. В ц икле

чтения после установки адреса процессор

выставляет сигнал "чтение памяти"

(MEMR),

который вместе с сигналом дешифратора

"устройство выбрано" поступает

на схему совпадения, формируя разрешающий

сигнал для передатчика. Заметим, что

сигналы записи и чтения памяти можно

вводить в обобщенный дешифратор сигналов

адреса и управления, который сформирует

все внутренние управляющие сигналы.

Заметим, что сигналы записи и чтения

снимаются при наличии сигнала “Готовность”.

икле

чтения после установки адреса процессор

выставляет сигнал "чтение памяти"

(MEMR),

который вместе с сигналом дешифратора

"устройство выбрано" поступает

на схему совпадения, формируя разрешающий

сигнал для передатчика. Заметим, что

сигналы записи и чтения памяти можно

вводить в обобщенный дешифратор сигналов

адреса и управления, который сформирует

все внутренние управляющие сигналы.

Заметим, что сигналы записи и чтения

снимаются при наличии сигнала “Готовность”.

П одключение

внешних устройств производится

аналогично, но в этом случае проводится

полная дешифрация всего адреса. Пример

функциональной схемы подключения

внешних устройств приведена на рис.4.6.

одключение

внешних устройств производится

аналогично, но в этом случае проводится

полная дешифрация всего адреса. Пример

функциональной схемы подключения

внешних устройств приведена на рис.4.6.

Устройство сопряжения с объектом управления может содержать несколько параллельных регистров ввода-вывода. Разряды выходных регистров подключаются к объектам управления для дискретного управления ИМ. Выходные дискретные сигнала от ОУ чаще всего поступают непосредственно на входы передатчиков (используется виртуальный входной регистр).

При подключении регистров внешних устройств необходима дешифрация всего адреса. Каждый входной или выходной регистр имеет свой адрес. Поэтому число выходов дешифратора адреса равно числу регистров. Для формирования сигналов записи и чтения регистров, выходы дешифратора адреса объединяются по схеме "И" соответственно с сигналами "вывод" (IOW) или "ввод" (IOR) шины управления. Возможно, а иногда целесообразно, использовать обобщенный дешифратор адреса и управляющих сигналов, который объединяет по схеме "И" сигнал "Устройство выбрано" каждого отдельного регистра с сигналом "Ввод" или "Вывод", формируя управляющие сигналы для своих регистров.

При выводе данных процессор устанавливает адрес, данные и, с задержкой, сигнал "Вывод", по которому данные записываются в адресуемый регистр. При чтении процессор устанавливает адрес и, с задержкой, сигнал "Ввод". При этом вырабатывается сигнал включения передатчика и данные поступают в шину данных.

Внешнее устройство, не успевающее выполнять обмен в темпе процессора, должно снимать сигнал готовности при обращении по его адресу и восстанавливать этот сигнал при завершении обмена. Для снятия сигнала готовности используется логический элемент (передатчик) с открытым коллектором, подключенный к линии “Готовность”.

В качестве регистров выходных данных и приемопередатчиков (виртуальных входных регистров) целесообразно использовать программируемый параллельный интерфейс (микросхему ППИ).