- •1. История цвм, поколения цвм.

- •2. Классификация эвм.

- •3. Принципы работы цвм по Фон-Нейману, основные определения.

- •4. Понятия об архитектуре и структуре цвм.

- •5. Основные технические характеристики цвм.

- •Установка охлаждения;

- •Уменьшение размеров;

- •Оптимизация алгоритмов вычисления.

- •10. Формат числа с плавающей запятой, его особенности.

- •11. Двоично-десятичный формат числа.

- •12. Прямой, обратный и дополнительный коды двоичных чисел, упрощенные правила перевода чисел в обратный и дополнительный коды.

- •13. Модифицированные коды двоичных чисел, их реализация в цвм.

- •27. Система команд процессора, формат команды.

- •28. Упрощенная структурная схема типового 16-разрядного процессора, назначение его частей.

- •31. Понятия о cisc и risc архитектуре процессора, отличия.

- •32. Организация прерываний вычисления в типовом процессоре.

- •34. Поколения процессоров фирмы Intel: характеристики, отличия, основные тенденции.

- •35. Классификация современных процессоров.

- •36. Классификация запоминающих устройств.

- •37. Принципы построения постоянного и оперативного запоминающих устройств.

- •38. Назначение и принципы построения кеш-памяти.

- •39. Принципы построения внешних запоминающих устройств.

- •40. Понятие об интерфейсах современных аппаратных средств вычислительной техники.

- •41. Классификация многопроцессорных вычислительных систем по взаимодействию команд и данных.

- •42. Классификация многопроцессорных вычислительных систем по распределению оперативной памяти.

- •43.Основные методы обслуживания средств вычислительной техники

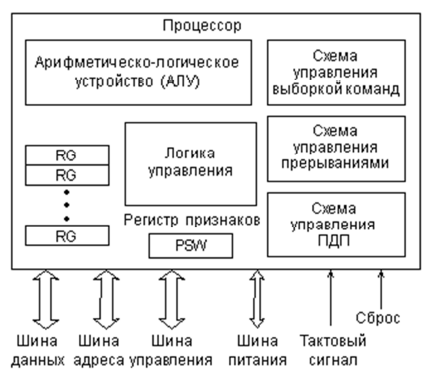

28. Упрощенная структурная схема типового 16-разрядного процессора, назначение его частей.

Схема управления выборкой команд выполняет чтение команд из памяти и их

дешифрацию. Совместно с блоком «Логика управления» выполняет функцию УУ. Схема использует для своей работы один из РОН − счетчик команд (СК, IP – Instruction Pointer), указывающий адрес выполняемой команды.

Блок логики управления – организует взаимодействие всех узлов процессора при

выполнении команды путем дешифрации КОП и формирования совокупности УС.

Арифметико-логическое устройство (или АЛУ, ALU) предназначено для обработки информации в соответствии с полученной процессором командой. Например, логические побитные операции над операндами типа "И", "ИЛИ", "НЕ" и т.д.), арифметические операции (типа сложения, вычитания, умножения, деления и т.д.). Над какими кодами производится операция, куда помещается ее результат — определяется выполняемой командой. Если команда сводится всего лишь к пересылке данных без их обработки, то АЛУ не участвует в ее выполнении.

Регистры общего назначения представляют собой ячейки сверхоперативной (очень быстрой) памяти и служат для временного хранения различных машинных слов: данных, адресов, служебных кодов. Обычно разрядность РОН = разрядности машинного слова.

Регистр признаков, РП (регистр состояния) − хранит слово состояния процессора (PSW – Processor Status Word); каждый бит этого слова (флаг) содержит информацию о результате предыдущей команды и флаги управления.

Например, структура РП i8086:

0 разряд: CF – Carry Flag – флаг переноса при арифметических операциях;

2 разряд: PF – Paritu Flag – флаг четности результата;

4 разряд: AF – Auxiliary Flag – флаг дополнительного переноса;

6 разряд: ZF – Zero Flag – флаг нулевого результата;

7 разряд: SF – Sign Flag – флаг знака результата;

8 разряд: TF – Trap Flag – флаг пошагового режима (при отладке);

9 разряд: IF – Interrupt-enable Flag – флаг разрешения аппаратных прерываний;

10 разряд: DF – Direction Flag – флаг направления при строковых операциях;

11 разряд: OF – Overflow Flag – флаг переполнения разрядной сетки;

Остальные разряды в резерве.

29-30. Взаимодействие узлов процессора при выполнении линейной программы/ветвлений в программе.

Лабораторная работа №8

31. Понятия о cisc и risc архитектуре процессора, отличия.

Один из путей решения этой задачи повышения быстродействия состоит в упрощении АЛУ за счет уменьшения количества выполняемых АЛУ команд (так называемые RISC-процессоры; альтернатива − CISC-процессоры с расширенным набором команд).

CISC – Complexed Instruction Set Computing – полный набор команд (микропроцессоры IA – Intel Architecture, например, Pentium-IV имеет 250 команд).

RISC – Reduceded Instruction Set Computing – сокращенный набор команд. Основные отличия RISC-архитектуры:

количество команд приблизительно в 3 раза меньше аналогичного CISC-процессора;

фиксированная длина команд;

большое число РОН, до 128;

основная часть команд представляет собой регистровые команды и команды

пересылки;

команды выполняются за один такт (аппаратная логика), за исключением единичных операций типа умножения;

нет команд косвенной адресации;

проще АЛУ, а значит больше места на кристалле для Кеша;

исходя из перечисленного RISC-процессоры используются в

высокопроизводительных системах, например, серверах.