- •У. Титце к. Шенк

- •4.7.1. Основная схема

- •5. Полевые транзисторы

- •9.5.1. Основная схема

- •10. Оптоэлектронные приборы

- •11. Линейные и нелинейные аналоговые вычислительные схемы

- •12. Управляемые источники и схемы преобразования полного сопротивления

- •15. Усилители мощности

- •15.4. Комплементарный эмиттерный повторитель по схеме дарлингтона

- •16. Источники питания

- •17. Аналоговые коммутаторы и компараторы

- •18. Генераторы сигналов

- •18.4. Генераторы сигналов специальной формы (функциональные генераторы)

- •19. Комбинационные логические схемы

- •20. Интегральные схемы со структурами последовательностного типа

- •20.4.1. Основная схема

- •21. Микро-эвм

- •22.2.1. Описание во временной области

- •22.2.2. Описание в частотной области

- •25. Измерительные схемы

- •26. Электронные регуляторы

- •Часть I.

- •1. Пояснение применяемых величин

- •Значения времени установления фильтра нижних частот

- •2.1.3. Длительность фронта импульса и частота среза филыра

- •2.2. Фильтр верхних частот

- •Выражение для частоты среза совпадает с соответствующим выражением для фильтра нижних частот:

- •Фильтр верхних частот как элемент rc-связи

- •Фильтр верхних частот как дифференцирующее звено

- •Последовательное соединение нескольких фильтров верхних частот

- •2.3. Компенсированный делитель напряжения

- •2.4. Пассивный полосовой rc-фильтр

- •2.5. Мост вина-робинсона

- •2.6. Двойной т-образный фильтр

- •2.7. Колебательный контур

- •3. Диоды

- •3.1. Характеристики и параметры

- •Динамический режим

- •3.2. Стабилитроны

- •3.3. Варикапы

- •4. Транзистор и схемы на его основе

- •4.1. Характеристики и параметры в режиме малых сигналов

- •4.2. Схема с общим эмиттером

- •4.2.1. Принцип работы

- •Входное и выходное сопротивления

- •4.2.2. Нелинейные искажения

- •4.2.3. Схема с общим эмиттером и отрицательной обратной связью по току

- •Расчет входного сопротивления

- •4.2.4. Отрицательная обратная связь по напряжению

- •4.2.5. Установка рабочей точки

- •Установка рабочей точки с помощью базового тока

- •Установка рабочей точки с помощью отрицательной обратной связи по току

- •4.3. Схема с общей базой

- •4.4. Схема с общим коллектором, эмиттерный повторитель

- •4.5. Транзистор как источник стабильного тока

- •4.5.1. Основная схема

- •4.5.2. Биполярный источник питания

- •4.5.3. Схема «токового зеркала»

- •Тогда получим

- •4.6. Схема дарлингтона

- •Комплементарная схема Дарлингтона

- •4.7. Дифференциальные усилители

- •4.7.1. Основная схема

- •4.7.2. Режим большого сигнала

- •4.7.3. Дифференциальный усилитель с отрицательной обратной связью по току

- •4.7.4. Напряжение разбаланса

- •Дрейф напряжения разбаланса

- •4.8. Измерение некоторых параметров при малом сигнале

- •4.9. Шумы транзистора

- •4.10. Предельные параметры

- •Ряд I (слева направо) то 18, то 5, то 66, то 3; ряд II: транзисторы соответствующей мощности в пластмассовых корпусах

- •5. Полевые транзисторы

- •5.1. Классификация

- •5.2. Характеристики и параметры малых сигналов

- •5.3. Предельные электрические параметры

- •5.4. Основные схемы включения

- •5.4.1. Схема с общим истоком

- •5.4.2. Схема с общим затвором

- •5.4.3. Схема с общим стоком, истоковый повторитель

- •5.5. Полевой транзистор как стабилизатор тока

- •5.6. Дифференциальный усилитель на полевых транзисторах

- •Дрейф рабочей точки

- •5.7. Полевой транзистор в качестве управляемого сопротивления

- •6. Операционный усилитель

- •6.1. Свойства операционного усилителя

- •Входное сопротивление

- •6.2. Принцип отрицательной обратной связи

- •6.3. Неинвертирующий усилитель

- •Входное сопротивление

- •Выходное сопротивление

- •6.4. Инвертирующий усилитель

- •7. Внутренняя структура операционных усилителей

- •7.1. Основные положения

- •7.2. Простейшие схемы операционных усилителей

- •Операционные усилители на полевых транзисторах

- •7.4. Коррекция частотной характеристики

- •7.4.1. Основные положения

- •7.4.2. Полная частотная коррекция

- •Схемная реализация

- •7.4.3. Подстраиваемая частотная коррекция

- •7.4.4. Скорость нарастания

- •Повышение максимального значения скорости нарастания

- •7.4.5. Компенсация емкостной нагрузки

- •7.5. Измерение параметров операционных усилителей

- •Измерение входного тока покоя

- •8. Простейшие переключающие схемы

- •8.1. Транзисторный ключ

- •Динамические свойства

- •8.2. Бистабильные релаксационные схемы

- •8.2.2. Триггер шмитта

- •Триггер Шмитта с эмиттерными связями

- •8.3. Моностабильная релаксационная схема

- •8.4. Нестабильная релаксационная схема

- •9. Базовые логические схемы

- •9.1. Основные логические функции

- •9.2. Составление логических функций

- •9.2.1. Таблица карно

- •9.3. Производные основных логических функций

- •Схемы ттл с диодами Шоттки

- •9.4.7. Комплементарная моп-логика (кмоп)

- •Двунаправленные логические элементы

- •9.4.8. Обзор

- •9.4.9. Специальные схемы выходных каскадов

- •При низком уровне ue выход схемы находится в безразличном состоянии

- •9.5. Интегральные триггеры

- •9.5.1. Основная схема

- •Статический синхронный rs-триггер

- •Статический синхронный d-триггер

- •9.5.2. Триггеры типа m-s (master-slave)

- •9.5.3. Динамический триггер

- •9.6. Полупроводниковые запоминающие устройства

- •Динамические свойства

- •Параметры некоторых распространенных микросхем озу

- •10. Оптоэлектронные приборы

- •10.1. Основные понятия фотометрии

- •10.2. Фоторезистор

- •10.3. Фотодиоды

- •10.4. Фототранзисторы

- •10.5. Светодиоды

- •10.6. Оптроны

- •Часть II. Применения

- •11. Линейные и нелинейные аналоговые вычислительные схемы

- •11.1 Схема суммирования

- •11.2. Схемы вычитания

- •11.3. Биполярное усилительное звено

- •11.4. Схемы интегрирования

- •11.5. Схемы дифференцирования

- •11.6. Решение дифференциальных уравнений

- •11.7. Функциональные преобразователи

- •Решение степенного уравнения вида

- •Применение степенных рядов

- •Дифференциальный усилитель

- •11.8. Аналоговые схемы умножения

- •Генератор треугольного сигнала— разд. 18.4

- •11.9. Преобразование координат

- •12. Управляемые источники и схемы преобразования полного сопротивления

- •12.1. Источники напряжения, управляемые напряжением

- •12.2. Источники напряжения, управляемые током

- •12.3. Источники тока, управляемые напряжением

- •12.4. Источники тока, управляемые током

- •12.5. Преобразователь отрицательного сопротивления (nic)

- •12.6. Гиратор

- •12.7. Циркулятор

- •13. Активные фильтры

- •13.1. Теоретическое описание фильтров нижних частот

- •Фильтр с критическим затуханием: 2-фильтр Бесселя:

- •Фильтр Баттерворта; 4 фильтр Чебышева с неравномерностью 3дБ.

- •13.2. Преобразование нижних частот в верхние

- •13.3. Реализация фильтров нижних и верхних частот первого порядка

- •13.4. Реализация фильтров нижних и верхних частот второго порядка

- •13.5. Реализация фильтров верхних и нижних частот более высокого порядка

- •13.6. Преобразование фильтра нижних частот в полосовой фильтр

- •13.7. Реализация полосовых фильтров второго порядка

- •13.8. Преобразование фильтров нижних частот в заграждающие полосовые фильтры

- •13.9. Реализация заграждающих. Фильтров второго порядка

- •13.10. Фазовый фильтр

- •13.11. Перестраиваемый универсальный фильтр

- •14. Широкополосные усилители

- •14.1. Зависимость коэффициента усиления по току от частоты

- •14.2. Влияние внутренних емкостей транзистора и емкостей монтажа

- •14.3. Каскодная схема

- •14.4. Дифференциальный усилитель как широкополосный усилитель

- •14.5. Симметричный широкополосный усилитель

- •14.6. Широкополосный повторитель напряжения

- •14.7. Широкополосный операционный усилитель

- •15. Усилители мощности

- •15.1. Эмоттерный повторитель как усилитель мощности

- •15.2. Комплементарный эмиттерный повторитель

- •15.3. Схемы ограничения тока

- •15.4. Комплементарный эмиттерный повторитель по схеме дарлингтона

- •15.5. Расчет мощного оконечного каскада

- •15.6. Схемы предварительных усилителей напряжения

- •15.7. Повышение нагрузочной способности интегральных операционных усилителей

- •16. Источники питания

- •16.1. Свойства сетевых трансформаторов

- •16.2 Выпрямители

- •Из соотношения (16.8) определим сначала

- •16.3. Последовательная стабилизация напряжения

- •Ограничение выходного тока

- •Повышение выходного тока стабилизатора

- •Стабилизация отрицательных напряжений

- •16.4. Получение опорного напряжения

- •Полевой транзистор как источник опорного напряжения

- •I кремниевый диод 2 два последовательно включенных кремниевых диода; з светодиод красного свечения;

- •5 Светодиод желтого свечения.

- •16.5. Импульсные регуляторы напряжения

- •Импульсный стабилизатор с повышением напряжения

- •Импульсный стабилизатор с инвертированием напряжения

- •17. Аналоговые коммутаторы и компараторы

- •17.1. Принцип действия

- •17.2. Электронные коммутаторы

- •Параллельный коммутатор

- •Последовательный коммутатор

- •Последовательно-параллельный коммутатор

- •17.3. Аналоговые коммутаторы на базе операционных усилителей

- •17.4. Аналоговые коммутаторы с памятью

- •Аналоговый коммутатор с памятью, выполненный на базе интегратора

- •17.5. Компараторы

- •17.6. Триггер шмитта

- •18. Генераторы сигналов

- •18.2. Кварцевые генераторы

- •18.3. Синусоидальные lс-генераторы

- •18.4. Генераторы сигналов специальной формы (функциональные генераторы)

- •Изменение скважности выходного напряжения

- •18.5. Мультивибраторы

- •Мультивибратор на базе прецизионного триггера Шмитта

- •Для времени, в течение которого транзистор открыт, получим выражение

- •19. Комбинационные логические схемы

- •19.1. Преобразователи кодов

- •Применение дешифраторов для программного управления

- •Преобразование кода «I из п» в двоичный

- •19.2. Мультиплексор и демультиплексор

- •Демультиплексор

- •19.3. Комбинационное устройство сдвига

- •Типы ис

- •19.4. Компараторы

- •Типы ис

- •19.5. Сумматоры

- •Определение переполнения

- •19.6. Умножители

- •19.7. Цифровые функциональные преобразователи

- •20. Интегральные схемы со структурами последовательностного типа

- •20.1. Двоичные счетчики

- •Счетчик с входами прямого и обратного счета

- •Устранение состязаний

- •20.2. Двоично-десятичный счетчик в коде 8421

- •Синхронный двоично-десятичный реверсивный счетчик

- •20.3. Счетчик с предварительной установкой

- •20.4. Регистры сдвига

- •20.4.1. Основная схема

- •20.5. Получение псевдослучайных последовательностей

- •20.6. Первоначальная обработка асинхронного сигнала

- •20.7. Систематический синтез последовательностньк схем

- •Входной мультиплексор

- •21. Микро-эвм

- •21.1. Основная структура микро-эвм

- •21.2. Принцип действия микропроцессора

- •21.3. Набор команд

- •Безусловные переходы

- •Маска прерываний

- •21.4. Отладочные средства

- •Язык ассемблера

- •21.5. Обзор микропроцессоров различного типа

- •21.6. Модульное построение микро-эвм

- •Микромощные запоминающие устройства

- •21.7. Периферийные устройства

- •Адаптер интерфейса периферийных устройств

- •Передача сигналов телетайпа

- •21.8. Минимальные система

- •22. Цифровые фильтры

- •22.1. Теорема о дискретизации (теорема о выборках)

- •Восстановление аналогового сигнала

- •22.2. Цифровая функция передачи фильтра

- •22.2.1. Описание во временной области

- •22.2.2. Описание в частотной области

- •22.3. Билинейное преобразование

- •22.4. Реализация цифровых фильтров

- •Простой пример реализации цифрового фильтра

- •Последовательная обработка сигнала

- •23. Передача данных и индикация

- •23.1. Соединительные линии

- •23.2. Защита данных

- •23.3. Статические цифровые индикаторы

- •23.4. Мультиплексные индикаторы

- •24. Цифро-аналоговые и аналого-цифровые преобразователи

- •24.1. Схемотехнические принципы ца-преобразователей

- •24.2. Построение ца-преобразователей с электронными ключами

- •Дифференциальный усилитель как токовый ключ

- •24.4. Основные принципы ац-преобразования

- •24.5. Точность ац-преобразоватю1ей

- •24.6. Построение ац-преобразователей

- •Компенсационный метод

- •Метод пилообразного напряжения

- •Метод двойного интегрирования

- •Автоматическая корректировка нуля

- •25. Измерительные схемы

- •25.1. Измерение напряжений

- •Увеличение диапазона управляемого напряжения

- •25.2. Измерение тока

- •Величина тока, вытекающего через точку 2, определяется соотношением

- •25.3. Измерительный выпрямитель

- •Двухполупериодный выпрямитель с заземленным выходом

- •Широкополосный Двухполупериодный выпрямитель

- •Измерение «истинного» эффективного значения

- •Термическое преобразование

- •Измерение мгновенных пиковых значений

- •26. Электронные регуляторы

- •26.1. Основные положения

- •26.2. Типы регуляторов

- •26.3. Управление нелинейными объектами

- •26.4. Отслеживающая синхронизация (автоподсгройка)

- •Динамическая характеристика

- •Расчет регулятора

9.5. Интегральные триггеры

Помимо логических элементов, реализующих основные логические функции, большое значение в качестве базовых элементов цифровой техники имеют различные триггерные схемы, работа которых будет описана также с помощью основных логических функций. Это дает возможность понять принцип их действия независимо от используемой в каждом случае схемной реализации.

9.5.1. Основная схема

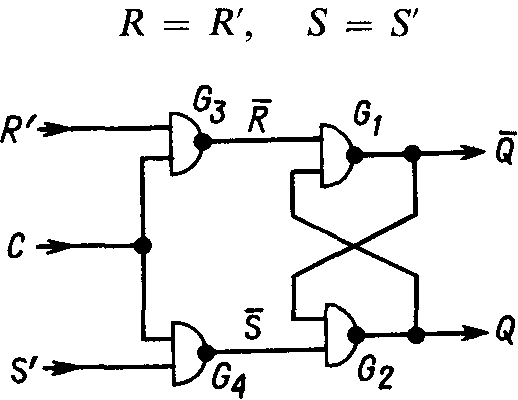

Триггер можно получить, охватив, как показано на рис. 9.24, два логических элемента ИЛИ-НЕ обратными связями.

Рис. 9.24 RS-триггер на элементах ИЛИ-НЕ

Он имеет два выходных сигнала: Q и Q, инверсные друг другу, и два входных: S (установка - Set) и R (сброс-Reset).

Если входные сигналы взаимоинверсны, причем S = 1 и R = 0, то

![]()

Следовательно, оба выходных сигнала действительно находятся в инверсных друг другу состояниях. При R = 1 и S = 0 можно получить обратные значения выходных сигналов триггера. Если R = S = 0, состояние выходных сигналов сохраняется Поэтому RS-триггер можно использовать для запоминания информации. При R = = S = 1 оба выходных сигнала равны нулю; однако в этом случае состояние выходных сигналов триггера не будет определено, если в какой-либо момент оба входных сигнала одновременно станут равными нулю Поэтому комбинация входных сигналов R = S = 1, как правило, является запрещенной. Все возможные состояния триггера отображены в таблице переключении 9.13. Мы уже ознакомились с этой таблицей, изучая транзисторную схему на рис. 8 8.

Таблица 9.13

Таблица переключении RS-триггера

Рис 9.25 .RS-триггер на элементах И-НЕ

В разд. 9.2 было отмечено, что логическое тождество не изменяется, если все переменные инвертировагь, а операции (+) и (•) поменять местами. Используя это правило, можно получить .RS-триггер, построенный на элементах И-НЕ (рис. 9.25), с таблицей переключении 9.13. Следует, однако, обратить внимание на то, что в качестве входных сигналов используются переменные R и S. Так как мы часто будем рассматривать RS-триггер на элементах И-НЕ, для входных переменных R и S представлена еще одна таблица переключении 9.14.

Таблица 9.14

Таблица переключении RS-триггера на элементах И-НЕ

Статический синхронный rs-триггер

Часто необходим такой триггер, который реагировал бы на входные сигналы только в определенные моменты времени. Эти моменты задаются с помощью дополнительного входного сигнала синхронизации С. На рис. 9.26 показан такой статический синхронный .R.S-триггер. При С = 0 сигналы R = S = 1. В этом случае триггер запоминает предыдущее состояние. При С = 1

Рис 9.26 Статический синхронный RS- триггер

и эта схема ведет себя как обычный RS-триггер.

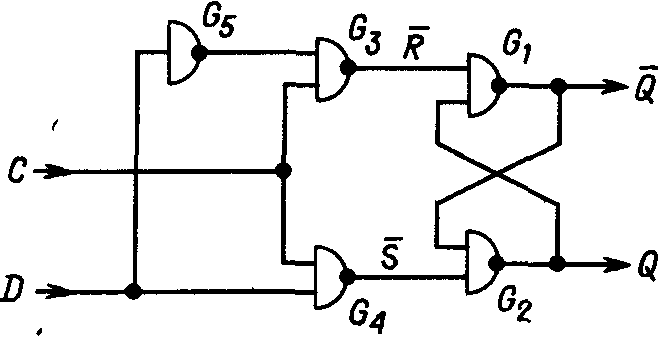

Статический синхронный d-триггер

Рассмотрим далее, как с помощью триггера, изображенного на рис. 9.26, можно запомнить значение логической переменной D. Ранее было показано, что Q = S, если входные сигналы инверсны друг другу и С = 1. Следовательно, для того чтобы запомнить значение переменной D, нужно лишь положить S = D и R = D. Для этого на рис. 9.27 используется инвертор G5. В выполненной таким образом ячейке памяти во время такта С = 1 устанавливается Q = D. Если С = 0, то запоминается полученное состояние триггера. Характерная особенность запоминающей ячейки состоит в том, что она имеет только один информационный вход D. Эти схемы называются обычно D-триггерами.

Легко заметить, что элемент G4 на рис. 9.27 при С = 1 работает как инвертор для переменной D. Поэтому можно исключить инвертор G5 и получить при этом упрощенную схему запоминающей ячейки, представленную на рис. 9.28.

Рис. 9.27 Статический синхронный D-триггер.

Рис 9.28 Упрощенная схема ячейки запоминающего устройства