- •У. Титце к. Шенк

- •4.7.1. Основная схема

- •5. Полевые транзисторы

- •9.5.1. Основная схема

- •10. Оптоэлектронные приборы

- •11. Линейные и нелинейные аналоговые вычислительные схемы

- •12. Управляемые источники и схемы преобразования полного сопротивления

- •15. Усилители мощности

- •15.4. Комплементарный эмиттерный повторитель по схеме дарлингтона

- •16. Источники питания

- •17. Аналоговые коммутаторы и компараторы

- •18. Генераторы сигналов

- •18.4. Генераторы сигналов специальной формы (функциональные генераторы)

- •19. Комбинационные логические схемы

- •20. Интегральные схемы со структурами последовательностного типа

- •20.4.1. Основная схема

- •21. Микро-эвм

- •22.2.1. Описание во временной области

- •22.2.2. Описание в частотной области

- •25. Измерительные схемы

- •26. Электронные регуляторы

- •Часть I.

- •1. Пояснение применяемых величин

- •Значения времени установления фильтра нижних частот

- •2.1.3. Длительность фронта импульса и частота среза филыра

- •2.2. Фильтр верхних частот

- •Выражение для частоты среза совпадает с соответствующим выражением для фильтра нижних частот:

- •Фильтр верхних частот как элемент rc-связи

- •Фильтр верхних частот как дифференцирующее звено

- •Последовательное соединение нескольких фильтров верхних частот

- •2.3. Компенсированный делитель напряжения

- •2.4. Пассивный полосовой rc-фильтр

- •2.5. Мост вина-робинсона

- •2.6. Двойной т-образный фильтр

- •2.7. Колебательный контур

- •3. Диоды

- •3.1. Характеристики и параметры

- •Динамический режим

- •3.2. Стабилитроны

- •3.3. Варикапы

- •4. Транзистор и схемы на его основе

- •4.1. Характеристики и параметры в режиме малых сигналов

- •4.2. Схема с общим эмиттером

- •4.2.1. Принцип работы

- •Входное и выходное сопротивления

- •4.2.2. Нелинейные искажения

- •4.2.3. Схема с общим эмиттером и отрицательной обратной связью по току

- •Расчет входного сопротивления

- •4.2.4. Отрицательная обратная связь по напряжению

- •4.2.5. Установка рабочей точки

- •Установка рабочей точки с помощью базового тока

- •Установка рабочей точки с помощью отрицательной обратной связи по току

- •4.3. Схема с общей базой

- •4.4. Схема с общим коллектором, эмиттерный повторитель

- •4.5. Транзистор как источник стабильного тока

- •4.5.1. Основная схема

- •4.5.2. Биполярный источник питания

- •4.5.3. Схема «токового зеркала»

- •Тогда получим

- •4.6. Схема дарлингтона

- •Комплементарная схема Дарлингтона

- •4.7. Дифференциальные усилители

- •4.7.1. Основная схема

- •4.7.2. Режим большого сигнала

- •4.7.3. Дифференциальный усилитель с отрицательной обратной связью по току

- •4.7.4. Напряжение разбаланса

- •Дрейф напряжения разбаланса

- •4.8. Измерение некоторых параметров при малом сигнале

- •4.9. Шумы транзистора

- •4.10. Предельные параметры

- •Ряд I (слева направо) то 18, то 5, то 66, то 3; ряд II: транзисторы соответствующей мощности в пластмассовых корпусах

- •5. Полевые транзисторы

- •5.1. Классификация

- •5.2. Характеристики и параметры малых сигналов

- •5.3. Предельные электрические параметры

- •5.4. Основные схемы включения

- •5.4.1. Схема с общим истоком

- •5.4.2. Схема с общим затвором

- •5.4.3. Схема с общим стоком, истоковый повторитель

- •5.5. Полевой транзистор как стабилизатор тока

- •5.6. Дифференциальный усилитель на полевых транзисторах

- •Дрейф рабочей точки

- •5.7. Полевой транзистор в качестве управляемого сопротивления

- •6. Операционный усилитель

- •6.1. Свойства операционного усилителя

- •Входное сопротивление

- •6.2. Принцип отрицательной обратной связи

- •6.3. Неинвертирующий усилитель

- •Входное сопротивление

- •Выходное сопротивление

- •6.4. Инвертирующий усилитель

- •7. Внутренняя структура операционных усилителей

- •7.1. Основные положения

- •7.2. Простейшие схемы операционных усилителей

- •Операционные усилители на полевых транзисторах

- •7.4. Коррекция частотной характеристики

- •7.4.1. Основные положения

- •7.4.2. Полная частотная коррекция

- •Схемная реализация

- •7.4.3. Подстраиваемая частотная коррекция

- •7.4.4. Скорость нарастания

- •Повышение максимального значения скорости нарастания

- •7.4.5. Компенсация емкостной нагрузки

- •7.5. Измерение параметров операционных усилителей

- •Измерение входного тока покоя

- •8. Простейшие переключающие схемы

- •8.1. Транзисторный ключ

- •Динамические свойства

- •8.2. Бистабильные релаксационные схемы

- •8.2.2. Триггер шмитта

- •Триггер Шмитта с эмиттерными связями

- •8.3. Моностабильная релаксационная схема

- •8.4. Нестабильная релаксационная схема

- •9. Базовые логические схемы

- •9.1. Основные логические функции

- •9.2. Составление логических функций

- •9.2.1. Таблица карно

- •9.3. Производные основных логических функций

- •Схемы ттл с диодами Шоттки

- •9.4.7. Комплементарная моп-логика (кмоп)

- •Двунаправленные логические элементы

- •9.4.8. Обзор

- •9.4.9. Специальные схемы выходных каскадов

- •При низком уровне ue выход схемы находится в безразличном состоянии

- •9.5. Интегральные триггеры

- •9.5.1. Основная схема

- •Статический синхронный rs-триггер

- •Статический синхронный d-триггер

- •9.5.2. Триггеры типа m-s (master-slave)

- •9.5.3. Динамический триггер

- •9.6. Полупроводниковые запоминающие устройства

- •Динамические свойства

- •Параметры некоторых распространенных микросхем озу

- •10. Оптоэлектронные приборы

- •10.1. Основные понятия фотометрии

- •10.2. Фоторезистор

- •10.3. Фотодиоды

- •10.4. Фототранзисторы

- •10.5. Светодиоды

- •10.6. Оптроны

- •Часть II. Применения

- •11. Линейные и нелинейные аналоговые вычислительные схемы

- •11.1 Схема суммирования

- •11.2. Схемы вычитания

- •11.3. Биполярное усилительное звено

- •11.4. Схемы интегрирования

- •11.5. Схемы дифференцирования

- •11.6. Решение дифференциальных уравнений

- •11.7. Функциональные преобразователи

- •Решение степенного уравнения вида

- •Применение степенных рядов

- •Дифференциальный усилитель

- •11.8. Аналоговые схемы умножения

- •Генератор треугольного сигнала— разд. 18.4

- •11.9. Преобразование координат

- •12. Управляемые источники и схемы преобразования полного сопротивления

- •12.1. Источники напряжения, управляемые напряжением

- •12.2. Источники напряжения, управляемые током

- •12.3. Источники тока, управляемые напряжением

- •12.4. Источники тока, управляемые током

- •12.5. Преобразователь отрицательного сопротивления (nic)

- •12.6. Гиратор

- •12.7. Циркулятор

- •13. Активные фильтры

- •13.1. Теоретическое описание фильтров нижних частот

- •Фильтр с критическим затуханием: 2-фильтр Бесселя:

- •Фильтр Баттерворта; 4 фильтр Чебышева с неравномерностью 3дБ.

- •13.2. Преобразование нижних частот в верхние

- •13.3. Реализация фильтров нижних и верхних частот первого порядка

- •13.4. Реализация фильтров нижних и верхних частот второго порядка

- •13.5. Реализация фильтров верхних и нижних частот более высокого порядка

- •13.6. Преобразование фильтра нижних частот в полосовой фильтр

- •13.7. Реализация полосовых фильтров второго порядка

- •13.8. Преобразование фильтров нижних частот в заграждающие полосовые фильтры

- •13.9. Реализация заграждающих. Фильтров второго порядка

- •13.10. Фазовый фильтр

- •13.11. Перестраиваемый универсальный фильтр

- •14. Широкополосные усилители

- •14.1. Зависимость коэффициента усиления по току от частоты

- •14.2. Влияние внутренних емкостей транзистора и емкостей монтажа

- •14.3. Каскодная схема

- •14.4. Дифференциальный усилитель как широкополосный усилитель

- •14.5. Симметричный широкополосный усилитель

- •14.6. Широкополосный повторитель напряжения

- •14.7. Широкополосный операционный усилитель

- •15. Усилители мощности

- •15.1. Эмоттерный повторитель как усилитель мощности

- •15.2. Комплементарный эмиттерный повторитель

- •15.3. Схемы ограничения тока

- •15.4. Комплементарный эмиттерный повторитель по схеме дарлингтона

- •15.5. Расчет мощного оконечного каскада

- •15.6. Схемы предварительных усилителей напряжения

- •15.7. Повышение нагрузочной способности интегральных операционных усилителей

- •16. Источники питания

- •16.1. Свойства сетевых трансформаторов

- •16.2 Выпрямители

- •Из соотношения (16.8) определим сначала

- •16.3. Последовательная стабилизация напряжения

- •Ограничение выходного тока

- •Повышение выходного тока стабилизатора

- •Стабилизация отрицательных напряжений

- •16.4. Получение опорного напряжения

- •Полевой транзистор как источник опорного напряжения

- •I кремниевый диод 2 два последовательно включенных кремниевых диода; з светодиод красного свечения;

- •5 Светодиод желтого свечения.

- •16.5. Импульсные регуляторы напряжения

- •Импульсный стабилизатор с повышением напряжения

- •Импульсный стабилизатор с инвертированием напряжения

- •17. Аналоговые коммутаторы и компараторы

- •17.1. Принцип действия

- •17.2. Электронные коммутаторы

- •Параллельный коммутатор

- •Последовательный коммутатор

- •Последовательно-параллельный коммутатор

- •17.3. Аналоговые коммутаторы на базе операционных усилителей

- •17.4. Аналоговые коммутаторы с памятью

- •Аналоговый коммутатор с памятью, выполненный на базе интегратора

- •17.5. Компараторы

- •17.6. Триггер шмитта

- •18. Генераторы сигналов

- •18.2. Кварцевые генераторы

- •18.3. Синусоидальные lс-генераторы

- •18.4. Генераторы сигналов специальной формы (функциональные генераторы)

- •Изменение скважности выходного напряжения

- •18.5. Мультивибраторы

- •Мультивибратор на базе прецизионного триггера Шмитта

- •Для времени, в течение которого транзистор открыт, получим выражение

- •19. Комбинационные логические схемы

- •19.1. Преобразователи кодов

- •Применение дешифраторов для программного управления

- •Преобразование кода «I из п» в двоичный

- •19.2. Мультиплексор и демультиплексор

- •Демультиплексор

- •19.3. Комбинационное устройство сдвига

- •Типы ис

- •19.4. Компараторы

- •Типы ис

- •19.5. Сумматоры

- •Определение переполнения

- •19.6. Умножители

- •19.7. Цифровые функциональные преобразователи

- •20. Интегральные схемы со структурами последовательностного типа

- •20.1. Двоичные счетчики

- •Счетчик с входами прямого и обратного счета

- •Устранение состязаний

- •20.2. Двоично-десятичный счетчик в коде 8421

- •Синхронный двоично-десятичный реверсивный счетчик

- •20.3. Счетчик с предварительной установкой

- •20.4. Регистры сдвига

- •20.4.1. Основная схема

- •20.5. Получение псевдослучайных последовательностей

- •20.6. Первоначальная обработка асинхронного сигнала

- •20.7. Систематический синтез последовательностньк схем

- •Входной мультиплексор

- •21. Микро-эвм

- •21.1. Основная структура микро-эвм

- •21.2. Принцип действия микропроцессора

- •21.3. Набор команд

- •Безусловные переходы

- •Маска прерываний

- •21.4. Отладочные средства

- •Язык ассемблера

- •21.5. Обзор микропроцессоров различного типа

- •21.6. Модульное построение микро-эвм

- •Микромощные запоминающие устройства

- •21.7. Периферийные устройства

- •Адаптер интерфейса периферийных устройств

- •Передача сигналов телетайпа

- •21.8. Минимальные система

- •22. Цифровые фильтры

- •22.1. Теорема о дискретизации (теорема о выборках)

- •Восстановление аналогового сигнала

- •22.2. Цифровая функция передачи фильтра

- •22.2.1. Описание во временной области

- •22.2.2. Описание в частотной области

- •22.3. Билинейное преобразование

- •22.4. Реализация цифровых фильтров

- •Простой пример реализации цифрового фильтра

- •Последовательная обработка сигнала

- •23. Передача данных и индикация

- •23.1. Соединительные линии

- •23.2. Защита данных

- •23.3. Статические цифровые индикаторы

- •23.4. Мультиплексные индикаторы

- •24. Цифро-аналоговые и аналого-цифровые преобразователи

- •24.1. Схемотехнические принципы ца-преобразователей

- •24.2. Построение ца-преобразователей с электронными ключами

- •Дифференциальный усилитель как токовый ключ

- •24.4. Основные принципы ац-преобразования

- •24.5. Точность ац-преобразоватю1ей

- •24.6. Построение ац-преобразователей

- •Компенсационный метод

- •Метод пилообразного напряжения

- •Метод двойного интегрирования

- •Автоматическая корректировка нуля

- •25. Измерительные схемы

- •25.1. Измерение напряжений

- •Увеличение диапазона управляемого напряжения

- •25.2. Измерение тока

- •Величина тока, вытекающего через точку 2, определяется соотношением

- •25.3. Измерительный выпрямитель

- •Двухполупериодный выпрямитель с заземленным выходом

- •Широкополосный Двухполупериодный выпрямитель

- •Измерение «истинного» эффективного значения

- •Термическое преобразование

- •Измерение мгновенных пиковых значений

- •26. Электронные регуляторы

- •26.1. Основные положения

- •26.2. Типы регуляторов

- •26.3. Управление нелинейными объектами

- •26.4. Отслеживающая синхронизация (автоподсгройка)

- •Динамическая характеристика

- •Расчет регулятора

Преобразование кода «I из п» в двоичный

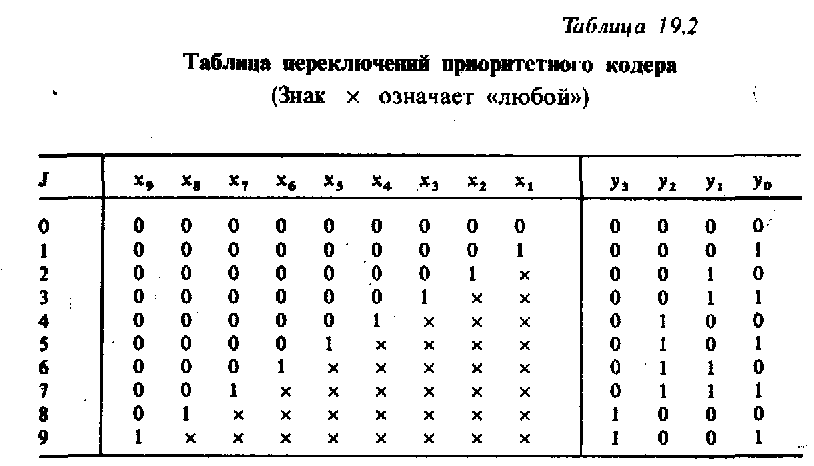

Для того чтобы преобразовать код «1 из n» в двоичный, можно использовать так называемый кодер (шифратор) с приоритетом. На его выходах формируется двоичное число, соответствующее наивысшему из входов, на которые подана единица. Значения входных переменных, расположенных ниже, не имеют значения. Поэтому эта схема и носит название «кодер с приоритетом». Такая схема позволяет преобразовывать не только код «1 из n», но и суммарный код, в котором единица стоит не в одном данном разряде, а во всех, расположенных за ним. Здесь приведена таблица переключении с приоритетом 19.2.

19.1.2. ДВОИЧНО-ДЕСЯТИЧНЫЕ КОДЫ

Ввод и вывод чисел в десятичной системе счисления невозможен с помощью обычного двоичного кода. Для этой цели был предложен двоично-десятичный код. В таком коде каждая отдельная десятичная цифра представлена с помощью двоичных знаков, в частности в виде соответствующего двоичного числа. В таком случае получим, например,

![]()

Записанное таким образом десятичное число более точно следует называть двоично-десятичным числом в коде 8421 или в натуральном двоично-десятичном коде. Десятичные цифры можно представить и с помощью других комбинаций двоичных знаков, содержащих 4 и более разрядов. Однако, поскольку двоично-десятичный код 8421 является самым распространенным, его называют просто двоично-десятичным кодом. Ниже используется этот термин, а отличные от натурального

Преобразование двоичного кода в двоично - десятичный

В предыдущем примере мы уже познакомились с процедурой преобразования четырехразрядного двоичного числа в двоично-десятичное: двоично-десятичные коды будем оговаривать особо.

Одно четырехразрядное двоичное число позволяет представить десятичные числа от 0 до 15. В случае двоично-десятичного кода из них используется только 10 комбинаций. Следовательно, для записи двоично-десятичного числа требуется больше разрядов, чем для записи двоичного.

При выполнении операций в десятичном коде можно получить результат, включающий десятичную «цифру» от 1010 до 1510 Подобные, не предусмотренные этим кодом цифры называются псевдотетрадами. Для исправления записи псевдотетрад следует уменьшить их на 1010 = 10102 и следующий по старшинству разряд увеличить на 1. Данный результат можно получить и другим способом, добавив к псевдотетраде число 6 = 01102 как показано в следующем примере:

Числа до 9 включительно остаются без изменения.

Числа свыше 9, представляющие собой псевдотетрады, подвергаются коррекции.

Двоичные числа, содержащие более 4 разрядов, можно преобразовать аналогичным образом. Для этого двоичное число, начиная со старшего разряда, «вдвигается» справа налево в двоично-десятичную разрядную сетку, как показано на рис. 19.5. Когда какая-либо единица пересекает границу между двоично-десятичными разрядами, возникает ошибка. Действительно, в случае двоичного числа разрядное значение этой единицы при сдвиге увеличивается с 8 до 16, тогда как для двоично-десятичного числа оно возрастает от 8 до 10. Поэтому на этом этапе двоично-десятичное число как бы уменьшается на 6. Следовательно, для коррекции необходимо прибавлять 6 к числу во всех случаях, когда единица пересекает границу между двоично-десятичными разрядами. К числу десятков надо прибавить 6, если единица перейдет в разряд сотен, и т.д. Составленное таким образом двоично-десятичное число имеет правильное значение, однако оно может еще содержать псевдотетрады. Чтобы этого не было, возникающие псевдотетрады корректируют непосредственно после каждого шага сдвига, прибавляя 6 к соответствующей декаде с переносом 1 в следующую.

Рис. 19.5. Преобразование двоичного кода в двоично-десятичный; в качестве примера взято число 218.

Следовательно, обе указанные коррекции производятся с помощью одной. и той же операции, а именно путем прибавления 6.

Вместо того чтобы прибавлять после сдвига 6, с тем же успехом можно перед сдвигом прибавлять 3. Необходимость такой коррекции можно также определить перед сдвигом. Если значение тетрады меньше или равно 4 = 01002, то при последующем сдвиге не произойдет перехода единицы через границу между декадами и не возникнут псевдотетрады. Таким образом, такую тетраду можно будет без изменений сдвигать влево. Если значение тетрады перед сдвигом равно 5, 6 или 7, то также не произойдет перехода единицы через границу, поскольку старший разряд равен нулю. Однако при этом возникнут псевдотетрады: десять, двенадцать, четырнадцать или одиннадцать, тринадцать, пятнадцать (в зависимости от того, будет ли в младший разряд сдвинут нуль или единица). Следовательно, в этих случаях необходима коррекция псевдотетрад путем прибавления 3 перед сдвигом.

Если значение тетрады составляет 8 или 9, необходимо корректировать переход единицы через границу между декадами. Поэтому после каждого сдвига появляются правильные тетрады 6 или 7 либо 8 или 9. При такой коррекции псевдотетрад полученное значение каждой тетрады не может быть более 9. Этим исчерпываются все возможности, и мы получим таблицу коррекции 19.3.

Преобразование двоичного числа в соответствующее двоично-десятичное можно реализовать, сдвигая влево двоичное число, записанное в регистре сдвига, разделенном на четырехразрядные секции. Каждая секция должна включать корректирующий элемент, который преобразует содержание регистра перед каждым последующим сдвигом в соответствии с таблицей переключении 19.3.

Наряду с подобным способом реализации преобразования кодов с помощью схем с памятью можно использовать комбинационные схемы, в которых операция сдвига проводится с помощью соответствующей логики. Эта схема представлена на рис. 19.6. Вместо сдвига числа справа налево здесь слева направо «сдвигаются» границы двоично-

десятичных разрядов, а каждая полученная тетрада корректируется в соответствии с табл. 19.3. Следовательно, для «сдвига» разрядной сетки с помощью комбинационной схемы на каждую декаду и каждый шаг сдвига необходимо по одному корректирующему элементу. Эта схема несколько упрощается, если исключить те корректирующие элементы, ко входам которых подключено менее трех двоичных разрядов, поскольку в этом случае коррекция

Рис. 19.6. Преобразование двоичного кода в двоично-десятичный с помощью комбинационной схемы. Приведенные значения соответствуют преобразованию числа 218.

не нужна. На рис. 19.6 приведена комбинационная схема для преобразования 8-разрядного двоичного числа. Эту схему легко распространить на любое число разрядов. Элементы, не используемые для преобразования 8-разрядного числа, показаны пунктиром. С помощью записанных здесь чисел можно проследить за процессом преобразования кода для примера, приведенного на рис. 19.5.

Корректирующие комбинационные схемы поставляются в виде программируемых изготовителем микросхем ПЗУ емкостью 32 байта. В одном корпусе размещаются три корректирующих элемента (рис. 19.7) Так как; согласно рис. 19.6, младший разряд не подается на корректирующую схему, то с помощью одной ИС можно преобразовать 6-разрядное двоичное число, а для 8-разрядного числа нужны три таких ИС.

Рис. 19.7. Структура интегральной микросхемы для преобразования двоичного кола в двоично-десятичный SN 74185.

Преобразование двоично-десятичного кода в двоичный

Во многих случаях двоично-десятичный код можно достаточно просто получить непосредственно, например с помощью двоично-десятичных счетчиков. Как будет показано ниже, в двоично-десятичном коде также можно выполнять многие вычислительные операции. Однако в некоторых случаях необходимо все же провести преобразование его в двоичный код. Это можно сделать путем последовательного деления числа на 2. Для этого десятичное число делится на 2. Если оно нечетное, то в остатке получится 1, т.е. в разряде 2° записывается 1. Затем частное от деления еще раз делится на 2, и, если остаток равен нулю, в разряде 21 записывается 0. Если остаток равен 1, то в этом разряде записывается 1. Аналогично получают и более старшие разряды двоичного числа. Деление двоично-десятичного числа на 2 очень просто можно провести путем сдвига вправо на один разряд, так как отдельные цифры уже представлены в двоичном коде. Самый правый бит, выдвинутый из двоично-десятичной разрядной сетки, и является искомым значением разряда. Но если при сдвиге единица пересекает границу между декадами, то возникает ошибка: при переходе от десятков к единицам значение разряда должно уменьшиться наполовину -от десяти до пятя. Однако в случае двоичного числа эта величина становится равной восьми. Поэтому, для коррекции нужно вычесть 3. Из этого вытекает следующее правило коррекции: если старший разряд в декаде равен единице, то необходимо данную декаду уменьшить на три. Таким образом можно непосредственно составить таблицу переключении для корректирующего элемента 19.4. Процесс преобразования заканчивается, если все двоично-десятичное число будет выдвинуто из разрядной сетки.

На

рис. 19.8 приведена комбинационная схема

для преобразования 2![]() -разрядного

двоично-десятичного числа. Здесь, так

же как и в схеме на рис. 19.6, сдвиг

двоично-десятичных разрядов достигается

путем соответствующего соединения

одинаковых комбинационных схем. Чтобы

наглядно продемонстрировать структуру

этой схемы, на рис. 19.8 изображены все

три корректирующих элемента для каждой

ступени кодопреобразователя. В

действительности если старший разряд

корректирующего элемента не используется,

то, согласно табл. 19.4, коррекция не нужна

и данный элемент можно исключить. На

рис. 19.8 такие элементы изображены

пунктирной линией.

-разрядного

двоично-десятичного числа. Здесь, так

же как и в схеме на рис. 19.6, сдвиг

двоично-десятичных разрядов достигается

путем соответствующего соединения

одинаковых комбинационных схем. Чтобы

наглядно продемонстрировать структуру

этой схемы, на рис. 19.8 изображены все

три корректирующих элемента для каждой

ступени кодопреобразователя. В

действительности если старший разряд

корректирующего элемента не используется,

то, согласно табл. 19.4, коррекция не нужна

и данный элемент можно исключить. На

рис. 19.8 такие элементы изображены

пунктирной линией.

Корректирующие схемы составляются из отдельных секций, содержащих по два элемента (рис. 19.9). Каждая секция представляет собой одну интегральную микросхему ПЗУ на 32 байта, программируемую изготовителем. Такая микросхема (типа SN 74184) имеет пять входов и пять выходов.

Рис. 19.8. Преобразование двончно-десятичиого кода в двоичный с помощью комбинационной схемы. Приведенные значения соответствуют преобразованию числа 218.

Рис. 19.9. Структура интегральной микросхемы для преобразования двоично-десятичного кода в двоичный.

19.1.3. КОД ГРЕЯ

Во многих случаях необходим числовой код, построенный таким образом, чтобы при переходе от одного числа к следующему изменялся всегда только один двоичный разряд. Этим свойством, в противоположность всем рассмотренным ранее кодам, обладает код Грея. На рис. 19.10 он сопоставлен с двоичным кодом.

Рис. 19.10. Сравнение кода Грея с двоичным.

Для его получения следует при переходе к следующему по старшинству разряду числа оставить без изменения все младшие разряды и приписать спереди единицу. При этом количество записанных нулей не должно увеличиваться.

Код Грея не позволяет выполнять арифметические операции. Поэтому его используют только в тех случаях, когда это дает существенные преимущества, и после этого снова переходят к двоичному коду.

Как можно видеть из рис. 19.10, для преобразования двоичного кода в код Грея можно использовать следующие операции:

Для старшего разряда gN N-разрядного числа эта операция упрощается, поскольку dN+1 = 0. В данном случае

![]()

Эта зависимость следует также и из рас. 19.10. Таким образом, для преобразо вания N-разрядного двоичного числа требуется N-1 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, включенных согласно рис. 19.11.

-

Рис. 19.11. Преобразование двоичного кода в код Грея.

Рис. 19.12. Преобразование кода Грея в двоичный.

Преобразование кода Грея в двоичный также производится с помощью элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Однако оно выглядит несколько сложнее. Для N-разрядного числа

Простейшая реализация этого выражения возможна с помощью последовательного соединения элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, как показано на рас. 19.12. Так же как и ранее, здесь используются N-1 элементов. Правда, в этом случае время задержки схемы значительно больше. Для младшего разряда оно составляет (N-1)tpd. Поэтому в случае многоразрядных чисел целесообразно, насколько возможно, выполнять необходимые логические операции параллельно. Для этого следует входы схемы подключить попарно к элементам ИСКЛЮЧАЮЩЕЕ ИЛИ. а их выходы также попарно соединить с входами следующих элементов.