- •Понятие о релейном устройстве. Примеры релейных устройств.

- •Понятие о фал. Связь между контактными схемами и предложениями человеческой речи. Особенности фал. Определение фал. Область определения и множество значений фал,

- •Способы задания фал. Таблица истинности. Геометрическая интерпретация. Задание фал с помощью 10-тичных чисел. Задание с помощью формул.

- •Общее число фал от n переменных. Фал от одной переменной.

- •Двоичная и десятичная системы счисления. Перевод из одной системы в другую. Задание фал с помощью десятичных чисел.

- •Аксиомы алгебры логики. Законы нулевого и единичного множества, повторения, двойного отрицания, логического нуля, логической единицы.

- •С уперпозиция фал. Переместительный, сочетательный и распределительный законы. Закон упрощения. Формулы де Моргана.

- •Стандартные формы фал.

- •Понятие о функционально полных системах фал. Минимально функционально полные системы. Доказательство того, что системы функций и,или,не ; или,не ; и,не образуют базис.

- •Логические схемы и и или на диодах при положительной и отрицательной логике.

- •Реализация функций не, и, или на транзисторах.

- •Теорема о том, что функция Вебба образует базис.

- •Теорема о том, что функция Шеффера образует базис.

- •Переход от задания фал в виде формулы к таблице истинности и от таблицы истинности к формуле.

- •Понятие о минимизации фал. Понятие о соседних конъюнкциях. Критерий минимизации.

- •Понятие о дснф, кснф, тднф, мднф. Особенности процесса минимизации.

- •Минимизация фал с помощью карт Карно.

- •Анализ многотактных схем. Общая структура мс. Понятие о внутреннем и полном состояниях схемы. Составление таблиц переходов и выходов. Закон работы многотактных схем.

- •Синтез многотактных схем по словесному заданию алгоритма работы. Этапы синтеза.

- •Состязания в многотактных схемах. Понятия о критических состязаниях.

- •Исключение критических состязаний за счет введения задержек и путем преобразования таблицы переходов.

- •Минимизация таблиц переходов.

- •Метод кодирования состояний по столбцам таблиц переходов.

- •Работа асинхронного rs-триггера. Синтез. Таблица переходов. Временная диаграмма.

- •Работа синхронного rs-триггера. Синтез. Таблица переходов. Временная диаграмма.

- •Структура синхронного автомата на rs- триггерах. Идея исключения критических состязаний.

- •Синтез синхронного автомата на rs- триггерах по заданным таблицам переходов и выходов.

- •Работа т-, d- и jk-триггера. Обозначение. Временная диаграмма.

Работа асинхронного rs-триггера. Синтез. Таблица переходов. Временная диаграмма.

S |

R |

Уn+1 |

0 |

0 |

Уn |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

безразличное |

Ассинхронным RS-триггером называется триггер, переходящий в новое состояние немедленно после поступления входного сигнала. S и R- информационные входы.

Работа синхронного rs-триггера. Синтез. Таблица переходов. Временная диаграмма.

S и R- информационные входы. С- синхровход (синхронизирующие сигналы), по ним происходит переключение триггера. Синхронный RS- триггер состоит их асинхронного RS- триггера и комбинационного цифрового устройства. При С=0 выходы =1 не зависят от R и S. При С=1 входные логические схемы 1 отрыты для сигналов R и S на вход.

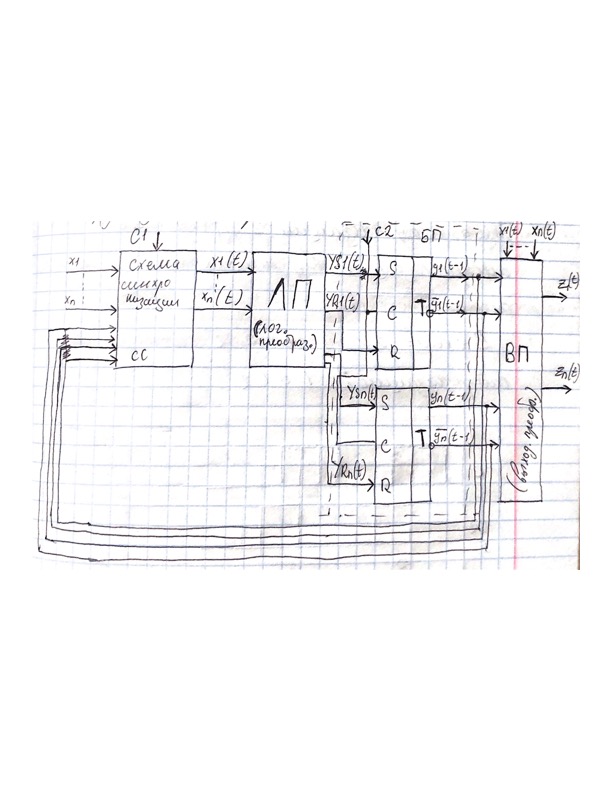

Структура синхронного автомата на rs- триггерах. Идея исключения критических состязаний.

БП-блок питания, содержит синхронные RS- триггеры

ЛП- логический преобразователь, формирует для каждого элемента памяти два сигнала воздействия Уs(t) на вход S и Yr(t) на вход R

ВП-выходной преобразователь, формирует выходные сигналы

СС- схема синхронная, осуществляет синхронизацию внешних и внутренних сигналов схемы.

В работе схемы можно выделить 2 этапа:

С1=1. Срабатывают СС и на выходе формируются входные сигналы и внутренние сигналы, которые характеризуют состояние схемы в предшествующий момент времени. В этом случае работает ЛП, который вычисляет функции Yr и Ys для каждого из триггеров

С2=1. Срабатывают элементы памяти в БП, когда все переходные процессы в первых 2х блоках завершены. Элементы памяти переходят в новое состояние с различным быстродействием, отсюда возможные критические состязания, но С2 наконец 1 этапа равен 0, когда С2=1 все триггеры находятся в устойчивом состоянии.

Синтез синхронного автомата на rs- триггерах по заданным таблицам переходов и выходов.

Алгоритм синеза:

Схема задается тп и тв

-

s

X

0

1

s

X

0

1

1

1

2

1

2

3

4

0

1

2

3

2

1

1

3

3

4

1

0

4

1

4

0

0

Произвольным образом кодируются строки ТП, т.к не требуется учитывать КС

s

У1

У2

1

0

0

2

0

1

3

1

0

4

1

1

Строится кодированная ТП и ТВ

s

X

0

1

s

X

0

1

00

00*

01

00

0*

1

01

10*

01

01

1*

1

10

10

11

10

1

0

11

00

11

11

0

0

Составляется ТИ, задающая все внутренние функции

Ху1у2

Уs1

Yr1

Ys2

Yr2

z

000

0

-

0

-

0

001

1

0

0

1

1

010

-

0

0

-

1

011

0

1

0

1

0

100

0

-

1

0

1

101

0

-

-

0

1

110

-

0

1

0

0

111

-

0

-

0

0

Осуществляется минимизация

По полученным функциям строится схема