- •Московский государственный институт электроники и математики

- •Архитектура эвм и систем

- •Содержание

- •Основные сокращения:

- •Введение

- •Конвейер команд

- •Архитектура эвм и языки программирования

- •Аппаратное и программное обеспечение для разработки системы контроля и управления объектами

- •Функциональная структура эвм Фон-Неймана

- •Каноническая структура эвм Фон-Неймана

- •Процессор

- •Вычислитель

- •Спецпроцессор

- •Определение эвм

- •Реализация моделей вычислителя

- •Понятие архитектуры эвм

- •Определение и понятия архитектуры эвм

- •Общее определение архитектуры средств обработки информации

- •Семейство эвм

- •Архитектурное сходство и родство представителей семейства

- •Поколения эвм

- •Показатель эффективности архитектурных свойств эвм.

- •Первое поколение (1949-1951[формирование поколений])

- •Второе поколение (1955-1966[формирование поколений])

- •Третье поколение эвм (1963 – 1965[формирование поколений])

- •О новшествах в машинах 3-его поколения:

- •Сравнительные характеристики эвм 1-3го поколения.

- •Конструктивно-технологический и функциональный признаки свт.

- •Признаки поколения свт.

- •Понятие архитектуры современного x86-процессора

- •Архитектура как совместимость с кодом

- •Архитектура как характеристика семейства процессоров

- •64-Битные расширения классической x86 (ia32) архитектуры

- •Процессорное ядро

- •Различия между ядрами одной микроархитектуты

- •Ревизии

- •Частота работы ядра

- •Микроархитектура процессоров Intel Itanium 2

- •Языки программирования

- •Поколения языков программирования

- •Первое поколение

- •Второе поколение

- •Третье поколение

- •Четвертое поколение.

- •Пятое поколение.

- •Классификация языков программирования

- •Парадигмы программирования.

- •Степень абстракции.

- •Распространенные языки программирования

- •Почему не существует «идеальных» языков программирования

- •Ассемблер

- •Архитектура микропроцессоров ia-32.

- •Введение.

- •Регистры и структура памяти ia-32

- •Команды ia-32

- •Литература

Частота работы ядра

Как правило, именно этот параметр в просторечии именуют «частотой процессора». Хотя в общем случае определение «частота работы ядра» всё же более корректно, так как совершенно не обязательно все составляющие CPU функционируют на той же частоте, что и ядро (наиболее частым примером обратного являлись старые «слотовые» x86 CPU — Intel Pentium II и Pentium III для Slot 1, AMD Athlon для Slot A — у них L2-кэш функционировал на 1/2, и даже иногда на 1/3 частоты работы ядра). Ещё одним распространённым заблуждением является уверенность в том, что частота работы ядра однозначным образом определяет производительность. На самом деле это дважды не так: во-первых, каждое конкретное процессорное ядро (в зависимости от того, как оно спроектировано, сколько содержит исполняющих блоков различных типов, и т.д. и т.п.) может исполнять различное количество команд за один такт, частота же — это всего лишь количество таких тактов в секунду. Таким образом (приведенное далее сравнение, разумеется, очень сильно упрощено и поэтому весьма условно) процессор, ядро которого исполняет 3 инструкции за такт, может иметь на треть меньшую частоту, чем процессор, исполняющий 2 инструкции за такт — и при этом обладать полностью аналогичным быстродействием.

Во-вторых, даже в рамках одного и того же ядра, увеличение частоты вовсе не всегда приводит к пропорциональному увеличению быстродействия. Здесь вам очень пригодятся знания, которые вы могли почерпнуть из раздела «Общие принципы взаимодействия процессора и ОЗУ». Дело в том, что скорость исполнения команд ядром процессора — это вовсе не единственный показатель, влияющий на скорость выполнения программы. Не менее важна скорость поступления команд и данных на CPU. Представим себе чисто теоретически такую систему: быстродействие процессора — 10'000 команд в секунду, скорость работы памяти — 1000 байт в секунду. Вопрос: даже если принять, что одна команда занимает не более одного байта, а данных у нас нет совсем, с какой скоростью будет исполняться программа в такой системе? Правильно: не более 1000 команд в секунду, и производительность CPU тут совершенно ни при чём: мы будем ограничены не ей, а скоростью поступления команд в процессор. Таким образом, следует понимать: невозможно непрерывно наращивать одну только частоту ядра, не ускоряя одновременно подсистему памяти, так как в этом случае начиная с определённого этапа, увеличение частоты CPU перестанет сказываться на увеличении быстродействия системы в целом.

Микроархитектура процессоров Intel Itanium 2

Общие сведения

64-битные процессоры семейства Itanium созданы на базе архитектуры EPIC.

Архитектура EPIC позволяет проводить программно достаточно серьезные оптимизации, при этом задействуя и ILP на аппаратном уровне, за счет чего существенно растет эффективность работы системы в целом. Сам подход EPIC (Explicitly Parallel Instruction Computing) сочетает в себе сильные стороны, как RISC, так и VLIW. Главное преимущество подхода состоит в том, чтобы максимально быстро загружать работой несколько исполняющих устройств. Схемы конвейеров Itanium и Itanium 2 приведены ниже.

Главный принцип EPIC - прежде всего, дать возможность программисту или компилятору явно указать на внутренний параллелелизм в программе прямо в последовательности инструкций, во вторую же очередь, все же позволить аппаратуре выявлять распараллеливаемые участки. Таким образом, ставка делается на программиста и компилятор, появляется возможность не уделять столь большое внимание логике проверки зависимостей и выявлениям внеочередных выполнений инструкций. Появляющееся же за этот счет место на чипе может быть использовано для увеличения числа ФУ и регистров, что дает возможность еще больше увеличить возможности параллельного выполнения кода.

В линейке процессоров есть примеры, как с технологией гипертрединга (выполнение нескольких контекстов на одном ядре), так и без нее. Семейство процессоров Itanium разрабатывалось совместно Intel и HP. Следует отметить обратную совместимость процессоров Itanium с процессорами Intel x86 и HP PA-RISC.

В процессорах Itanium 2 применяются 64-битные инструкции непосредственно на аппаратном уровне, чего не было на процессорах Itanium.

В целом, в Itanium 2 стало больше функциональных устройств, чем было у Itanium:

Всего в Itanium 2 есть 6 АЛУ, в то время как Itanium может использовать лишь 4 за цикл.

В Itanium 2 есть 4 порта памяти, позволяющие по 2 целочисленных загрузки и сохранения за цикл, в то время как в Itanium есть только 2 порта.

Itanium 2 может выполнить одну SIMD инструкцию с плавабщей точкой за цикл, в то время как Itanium - две.

При определенных условиях Itanium 2 может направить I-type инструкцию на функциональные устройства памяти, в то время, как Itanium - только на целочисленные же функциональные элементы.

При обработке операций, Itanium 2 учитывает многократно повторяющиеся операции.

В большинстве случаев латентности у Itanium 2 такие же или меньше, чем у Itanium. Более подробные сведения можно найти в документе Intel Itanium 2 Processor Reference Manual For Software Development and Optimization.

В случае промаха при чтении из кэша, в Itanium конвейер задерживается на 10 тактов, в Itanium 2 - на 8.

В случае неудачи chk.a, chk.s или fchkf, у Itanium шел вызов обработчика ОС, в случае же Itanium 2 обычно обходится без этого, а на аппаратном уровне, что снижает накладные расходы примерно с 200 до 18 тактов

Как у Itanium, так и у Itanium 2, кэш трехуровневый. В Itanium 2 размер строки вдвое больше, чем у Itanium. TLB у Itanium 2 не только больше, но и состоит из двух уровней, против одного у Itanium. Кэш третьего уровня у Itanium 2 располагается на самом чипе. Сравнительные характеристики кэшей можно найти в документе Intel Itanium 2 Processor Reference Manual For Software Development and Optimization.

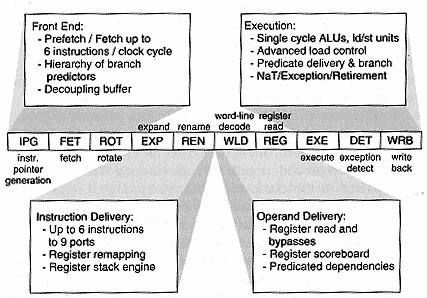

Конвейер в Itanium 2 стал на 2 ступени короче по сравнению с Itanium. Функции FET и WLD были перенесены на соседние ступени. На рисунках ниже показаны схемы конвейеров Itanium и Itanium 2, соответственно.

Принципиальная схема Intel® Itanium2® и Montecito

На рисунке

ниже показана принципиальная схема

Itanium

2.

С появлением

двухъядерных процессоров, один из первых

встает вопрос, какова взаимосвязь этих

ядер, какие общие элементы микроструктуры

используются, как это будет сказываться

на работе программы, и как ее вообще

разрабатывать. На рисунке ниже показана

принципиальная схема одноядерного

Itanium2

и двухъядерного Montecito.

Структура же самих ядер идентична и у каждого - свой кэш последнего уровня. Т.е. в Montecito всего существует 4 контекста: два ядра, в каждом - еще два, благодаря гипертредингу.

Синхронизаторы и арбитр в Montecito

Как видно из схемы выше, появляются два новых элемента - т.н. синхронизатр и арбитр. Арбитр - специальное устройство, позволяющее обеспечить доступ с низкой латентностью к интерфейсу FSB. На кадом ядре существует специальный служебный элемент, посредством которого арбитр связан с самим ядром - синхронизатор. Арбитр работает на фиксированной частоте, кратной частоте FSB.

Асинхронный интерфейс между арбитром и каждым ядром позволяет изменять частоту работы ядра и кэша по необходимости. Разумеется, наличие арбитра обуславливает появление соответствующей латентности при общении ядра и системного интерфейса. При прочих равных приоритет отдается запросам на чтение, как наиболее важным.

Альянс разработчиков решений на базе архитектуры Intel® Itanium® (Itanium Solutions Alliance, ISA)

Несколько наиболее известных компаний в области профессиональных вычислений объединились в альянс, чтобы проводить согласованную разработку и поддержку решений на базе процессоров Intel® Itanium®. Среди участников Альянса такие компании, как Bull, Fujitsu, Fujitsu Siemens Computers, Hitachi, HP, Intel, NEC, SGI, Unisys, BEA, Microsoft, Novell, Oracle, Red Hat, SAP, SAS и Sybase. Альянс предлагает обширные ресурсы для поставщиков ПО и корпоративных IT-организаций, заинтересованных в разработке и внедрении решений на базе процессоров Intel® Itanium®, в том числе:

Каталог решений с архитектурой Intel® Itanium® (The Itanium Solutions Catalog) – полный перечень приложений, оптимизированных для серверов на базе процессоров Intel® Itanium®.

Сеть решений на базе архитектуры Intel® Itanium® (The Itanium Solutions Network) – глобальная сеть центров содействия дистанционному переносу и тестированию приложений.

Дни разработчиков решений (Developers Days) – мероприятия, проводимые с целью предоставления разработчикам инструменты и техническую поддержку для переноса и оптимизации приложений.

Дополнительную информацию можно найти на Web-сайте альянса.

Семейство процессоров Intel Itanium 2 серии 9000

|

Процессор |

Частоста |

Кэш |

Частота шины |

Потребляемая мощность |

Гипертрединг |

|

Dual Core Intel Itanium 2 9050 |

1.60 |

24 МБ L3 |

400/533 |

104 Вт |

да |

|

Dual Core Intel Itanium 2 9040 |

1.60 |

18 МБ L3 |

400/533 |

104 Вт |

да |

|

Dual Core Intel Itanium 2 9030 |

1.60 |

8 МБ L3 |

400/533 |

104 Вт |

нет |

|

Dual Core Intel Itanium 2 9020 |

1.42 |

12 МБ L3 |

400/533 |

104 Вт |

да |

|

Dual Core Intel Itanium 2 9015 |

1.40 |

12 МБ L3 |

400 |

104 Вт |

да |

|

Intel Itanium 2 9010 |

1.60 |

6 МБ L3 |

400/533 |

75 Вт |

нет |

* У всех указанных процессоров серии 9000 имеется поддержка Intel Cache Safe и Intel Virtual