- •ВВЕДЕНИЕ

- •1. ОБЛАСТИ ПРИМЕНЕНИЯ ЦИФРОВЫХ УСТРОЙСТВ

- •1.1. Системы автоматического управления

- •1.2. Системы передачи информации (СПИ)

- •1.3. Системы обработки информации (вычислительные системы)

- •2. МАТЕМАТИЧЕСКИЕ ОСНОВЫ УСТРОЙСТВ ОБРАБОТКИ СИГНАЛОВ

- •2. 1. Спектральные методы обработки сигналов

- •2. 2. Пространственные методы обработки сигналов

- •3. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

- •3.1. Программируемые схемы со встроенным процессорным ядром

- •3. 2. Маршрут проектирования систем на кристалле

- •3.3. Примеры поведенческого описания и синтеза схем

- •4. СОВРЕМЕННЫЕ САПР СИСТЕМЫ НА КРИСТАЛЛЕ

- •4. 1. Проектирование в среде САР Active-HDL

- •4.1.1. Основы работы с Active-HDL

- •4.1.2. Технология автоматизированной верификации

- •4. 2. Проектирование в среде САПР Quartus II

- •4. 3. Проектирование в среде САПР Fastchip

- •Список использованной литературы

- •Список рекомендуемой литературы

- •СОДЕРЖАНИЕ

В этом случае в проект будет вставлена только ссылка на сгенерированный файл. Если щелкнуть на ссылке правой кнопкой мыши и выполнить команду Properties, то можно определить путь к этому файлу.

Во втором разделе Additional Files Options диалоговой панели IP Core Generator Configuration можно дополнительно разрешить генерацию графическогоизображениямодуля(Generate block diagram symbol) и создание макрофайла, чтобы поместить его в рабочую библиотеку (Generate macro).

Установив флажок Run macro after generation, вы разрешите программе завершить процесс генерации модуля компиляцией и вставкой его графического изображения в рабочую библиотеку.

В третьем разделе View Options рекомендуется установить флажок Show generated HDL file after generation, и тогда автоматически будет открываться для показа созданный IP Core-генератором файл.

4. 2. Проектирование в среде САПР Quartus II

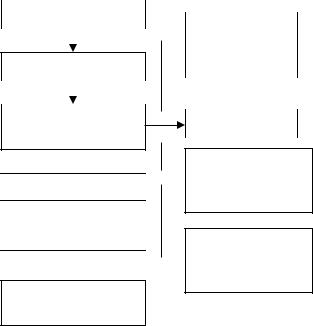

Фирма «Intel» предоставляет полную мультиплатформенную среду проектирования Quartus II, которая может быть легко перенастроена под конкретные требования. Это идеальная среда для проектирования на основе ПЛИС законченных реконфигурируемых систем на кристалле (РСнК). Программное обеспечение Quartus II включает в себя средства для всех фаз проектирования с применением ПЛИС различных структур. На рис. 4.14 представлена общая структурная схема проектирования в среде Quartus II [34]–[36].

Дополнительно Quartus II предо-

ставляет возможность использовать

ставляет возможность использовать

графический интерфейс пользователя или интерфейс командной строки в

графический интерфейс пользователя или интерфейс командной строки в

каждой фазе разработки схемы.

Можно использовать какой-либо ин-

Можно использовать какой-либо ин-

терфейс для всего процесса проекти-

терфейс для всего процесса проекти-

рованияилиразличныенастройкидля

рованияилиразличныенастройкидля

каждой отдельной фазы разработки.  Под термином «проект» в рам-

Под термином «проект» в рам-

ках пакета Quartus II понимается

набор файлов, связанных с проектируемым модулем, в котором выделяются две группы файлов:

набор файлов, связанных с проектируемым модулем, в котором выделяются две группы файлов:

81

1)логические файлы, описывающие алгоритм работы устройства (Design

Files);

2)вспомогательные файлы (Ancilary Files).

Проект может содержать один либо несколько логических файлов, образующихиерархическоеописаниепроектируемогомодуля.Прииерархическом описании среди множества логических файлов различают:

а) файл верхнего уровня в иерархии описаний (Top-level Design File); б) файлы нижних (одного или нескольких) уровней иерархии (Low-level

Design files).

В файле верхнего уровня задается архитектура модуля, определяется набормодулей,входящихвегосоставкаккомпоненты,иихвзаимосвязь.Описания этих модулей содержатся в логических файлах более низкого уровня иерархии.Вихсоставвсвоюочередьввидекомпонентовтакжемогутвходить модули,описания которыхприведены влогическихфайлахеще более низкого уровня иерархии, и т. д.

Имяпроектадолжносовпадатьсименеммодуляверхнегоуровнявиерархии описаний, а следовательно и именем логического файла, в котором хранится его описание.Имена модулей нижних уровней иерархии в своюочередь должны совпадать с именами файлов, в которых они описаны.

Логический файл − это файл одного из следующих типов:

•Block Design File (стандартное расширение − .bdf) – файл содержит блок-схему устройства, созданную в рамках пакета Quartus II;

•Graphic Design File (стандартное расширение − .gdf) – файл содержит принципиальную электрическую схему, созданную в рамках пакета Quartus II;

•AHDLText DesignFile(стандартноерасширение −.tdf)– файл содержит текстовое описание модуля на языке IntelHDL;

•WaveformDesign File (стандартное расширение − .wdf) – файл содержит временные диаграммы входных и выходных сигналов, созданные врамках па-

кета Quartus II;

•VHDLDesignFile(стандартноерасширение−.vdf)– файлсодержиттекстовое описание модуля на языке VHDL;

•Verilog Design File (стандартное расширение − .v) -файл содержит текстовое описание модуля на языке Verilog HDL;

•Orcad Schematic Files (стандартное расширение − .sch) -файл содержит схему, созданную в рамках пакета ORCAD;

82

•EDIF Input Files (стандартное расширение−.edf) -файл содержит список цепей;

•Xilinx Netlist Format File (стандартное расширение − .xnf) -файл содер-

жит описание модуля, полученное в рамках пакета фирмы Xilinx. Вспомогательныефайлыхранятдополнительнуюинформациюопроекте,

их имена совпадают с именем проекта.

Стратегия проектирования. Средапроектирования Quartus II позволяет реализовать либо стратегии восходящего, либо нисходящего проектирования.

Итаидругаястратегииподразумеваютиспользованиеповеденческихиструктурныхописаниймодулей.Приструктурномописаниимодульпредставляется в виде совокупности взаимосвязанных компонентов более низкого уровня в иерархии описаний. При поведенческом же описании задается алгоритм работы модуля.

Восходящеепроектированиеприменимовслучае,когдадлясоздаваемого

устройства имеется детальное структурное описание (обычно − принципиальная схема на микросхемах средней степени интеграции), выполненное в элементном базисе, отличном от имеющегося в распоряжении разработчика СБИС.

При этом разработчик решает следующие задачи:

•создание функциональных аналогов элементов, использованных в заданном структурном описании;

•отладка созданных компонентов;

•сборка созданных компонентов в единый модуль;

•моделирование и отладка устройства в целом.

Таким образом, в процессе проектирования разработчик сначала создает модулинижнегоуровнявиерархииописаний,азатеммодульверхнегоуровня. Отсюда и название стратегии проектирования.

Стратегия нисходящего проектирования применяется в случае, когда задан алгоритм работы (поведенческое описание) создаваемого устройства и набор системных требований (максимальная тактовая частота работы, задержка распространения сигналов от входов до выходов, потребление энергии, стоимостьи т.д.).При этом поведенческоеописание может бытькак формализованным (блок схема алгоритма, граф, таблица переходов и выходов и т. д.), так и неформализованным (словесное описание). Реализация нисходящего проектирования базируется на итерационном выполнении структурной декомпозиции.

83

Упрощенно, ориентируясь на возможности пакета Quartus II, процедура нисходящего проектирования выглядит следующим образом:

1.РазработкаархитектурыСБИС.Исходноеповеденческоеописаниепреобразуется в структурное (блок-схему), элементами которого являются архитектурные модули.

2.Архитектурные модули либо описываются на поведенческом уровне (например, с помощью языка Verilog), либо осуществляется их структурная декомпозиция и создается структурное описание, элементами которого являются функциональные модули. Далее процедура итерационно повторяется до тех пор, пока все функциональные модули не будут описаны на поведенческом уровне.

3.После этого осуществляется функциональное моделирование модулей, имеющих поведенческие описания.

Моделирование и отладка устройства в целом. В процессе проектиро-

вания разработчик опускается с верхнего уровня иерархии описаний, уровня СБИС, к нижним уровням. Отсюда и название стратегии проектирования.

Следует отметить, что стратегия нисходящего проектирования имеет безусловные преимущества как по временным затратам на разработку, так и по качеству проработки проекта.

Независимо от выбранной стратегии проектирования для задания структур и алгоритмов работы модулей целесообразно использование текстового описания, созданного на языках описания аппаратуры высокого уровня,

например IntelHDL (Verilog ).

Рассмотримпримерпроектированияцифровогоаппаратно-программного устройства, формирующего заданную последовательность выходных кодов; при этом рассматриваются основные этапы проектирования и особенности настроек системы Quartus II в каждой конкретной части разработки, а также общая методология проектирования.

В начале создается общая блок-схема верхнего уровня иерархии, далее выполняется описание отдельных модулей устройства, после чего файлы проекта объединяются, т. е. реализуется стратегия нисходящего проектирования.

Описание проекта

Рассматривается аппаратно-программный проект СнК в виде микропроцессорной системы, включающий в свой состав следующие компоненты:

• 32-й разрядный процессор;

• система коммуникационных соединений, позволяющая объединить все компоненты в единый проект;

84

•внутренняяпамятьдляформированияипередачинеобходимыхданных;

•порты ввода вывода для формирования программно-доступных регистров загрузки устройства вывода;

•устройство вывода, включающее набор светодиодов.

Под управлением процессора NIOSII на устройстве вывода (светодиоды LED8 LED1)схемы РСнК (рис. 4.15)отображаютсярезультатыработы 8-раз- рядного двоичного счетчика (двоичные коды чисел от 0 до 255), изменяющихся циклически.

|

32-й разрядный адрес |

|

|

|

|

|

|

||

|

коммуникационных соединений |

|

Внутренняя |

|

|

||||

|

|

ввода |

|

Порты ввода/ |

|

|

|||

|

|

Чтение |

|

|

память |

|

|

||

32-й разрядный |

|

Запись |

|

Коммуникационные соединения |

|||||

|

|

|

|

||||||

процессор |

|

32-разрядная шина |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

(Nios II) |

|

|

|

|

|

|

|

||

|

|

|

Система |

|

|

|

|

|

|

|

|

|

|

|

вывода |

|

|||

|

|

|

|

|

|

||||

|

|

32-разрядная шина |

|

|

|||||

|

|

|

|

|

|||||

|

|

вывода |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Устройства |

|

||

|

|

|

|

|

|||||

|

|

|

|

|

|

вывода |

|

||

|

|

|

|

|

|

|

|

|

|

Рис.4.15. Структура проекта

Маршрут проектирования включает следующие основные этапы:

Этап 1. Подготовка проекта

В начале необходимо создать сам проект в среде САПР, а для этого необходимо выполнить следующие шаги:

1.Запустить пакет QuarusII.

2.В меню File менеджера пакета выбрать New Project Wizard.

3.На экране появится окно введения – Introduction (если оно не было отключено). Нажать кнопку next.

4.В появившемся окне введите следующие данные (табл. 4.9).

5.Нажать кнопку Next.

6.В окне Add Files [page 2 of 5] нажать кнопку Next.

7.В окне Family & Device Setting [page3 of 5]:

–в разделе Family укажите Cyclone III.

–в разделе Available devices укажите СБИС EP4CE6E22C8.

–нажать кнопку Next.

85

|

Таблица 4.9 |

Список конструкций формирования проекта |

|

|

|

What is the working directory for this project? |

Папка инсталляции\ |

Рабочая папка (с помощью браузера найдите |

\Sok_Fah_Proekty\Proj_1\ |

рабочую папку проекта) |

|

|

|

What is the name of this project? |

Proj1 |

Имя проекта |

|

|

|

What is the name of the top-level design entity for this |

Proj1 |

project? |

|

Имя модуля верхнего уровня в иерархии проекта. |

|

|

|

8. В окне EDA Tool Setting [page 4 of 5] оставить все без изменения и нажать кнопку Next.

Рис. 4.16. Окно выбора режима работы редактора

9. Появится окно Summary [page 5 of 5], в котором указаны установки, заданные для создаваемого проекта. Если все они правильны, то на этом завершается данный этап и нужно нажать кнопку Finish.

Этап 2. Создание аппаратной части проекта

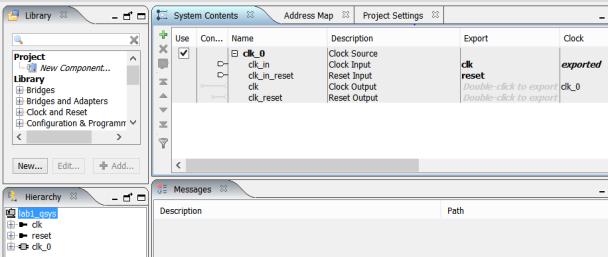

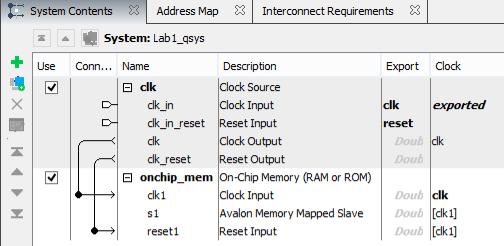

1.ВыполнитькомандуTools Qsys.Будетзапущенамикропроцессорная система РСнК (Qsys) и откроется закладка System Contents, в которую по умолчанию будет добавлен компонент source clock (рис. 4.16).

2.Выполните команду File Save as и сохраните систему под именем

Proj1_qsys.

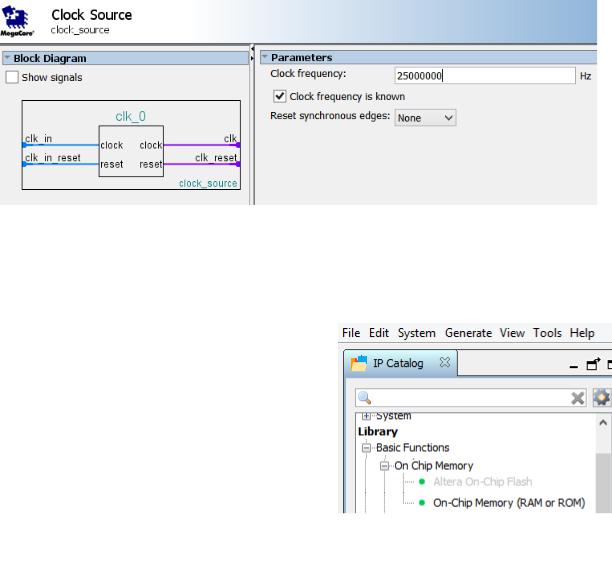

3.После двойного щелчка по модулю генератора тактовых импульсов (clock Source) откроется окно задания параметров модуля. Задать частоту тактового сигнала = 25 МГц, что соответствует частоте кварцевого генератора на плате QuarSapr II (рис. 4.17).

86

Рис. 4.17. Окно выбора режима работы редактора

Переименовать компонент в закладке System Contents и выбрать новое имя компонента (т. е. нажать правую клавишу мыши и выбрать команду

Rename): clk.

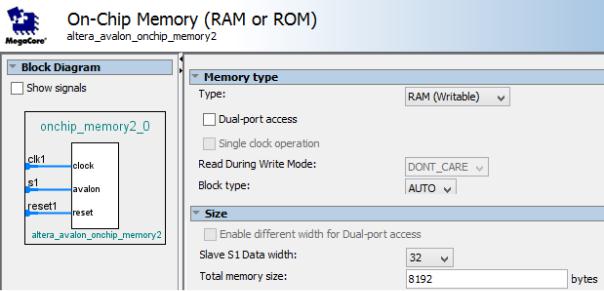

4. Создание на основе встроенных |

|

модулей М9К памяти для команд и дан- |

|

ных процессора. В списке доступных ком- |

|

понентов (рис. 4.18.) выбрать блок памяти |

|

из библиотеки On-Chip Memory (RAM and |

|

ROM); дважды щелкнуть по нему левой |

|

клавишей мыши. Появится окно On-Chip |

|

Memory (RAM and ROM) (рис. 4.19). |

|

В разделе memory type задайте тип |

Рис. 4.18. Окно выбора режима |

памяти RAM. |

работы редактора |

Вразделе Size задайте размер памяти 8192 байт (рис. 4.19).

Вразделеmemory Initialization оставитьвсезначенияпоумолчанию, после чего автоматически будет создан файл инициализации памяти, имя которого указано внизу страницы с настройками.

Процедуразавершена,ипамятьдлякомандиданныхпроцессорасоздана. Так как для нормальной работы модуль должен быть подключен к тактовому сигналу – сигналу сброса внутренних регистров и мастеру на шине Avalon-ММ – появятся сообщения об ошибках и предупреждение. Появляю-

щиеся ошибки и предупреждения пока можно проигнорировать.

Для переименования созданного модуля памяти в закладке System Contents необходимо выбрать имя созданного компонента памяти, далее нажать правую клавишу мыши и выбрать команду Rename. Пусть, например, новое имя будет onchip_mem.

87

Рис. 4.19. Окно выбора режима работы редактора

Двойным щелчком в поле компонента нужно открыть окно настройки и установить опцию Enable non-default initialization file (имя файла должно быть onchip_mem.hex).

Следующий шаг – соединить выход clk компонента clk с входом clk1 компонента onchip_mem. Затем нажать кнопку Finish.

Таким образом будет создана память для команд и данных процессора. Таккакдлянормальнойработыкомпонентдолженбытьподключенктактовому сигналу – сигналу сброса внутренних регистров и Мастеру на шине Avalon-ММ – появятся сообщения об ошибках и предупреждение. Появляю-

щиеся ошибки и предупреждения пока можно проигнорировать. Переименовать созданный модуль памяти: в закладке System Contents:

выбрать имя созданного модуля памяти, нажать правую клавишу мыши и выбрать команду Rename, а также поменять имя на новое: onchip_mem.

Двойным щелчком в поле компонента необходимо открыть окно настройки и установить опцию Enable non-default initialization file (имя файла должно быть onchip_mem.hex).

Соединить выход clk компонента clk с входом clk1 компонента onchip_mem, а выход clk_reset компонента clk source с входом reset1 компонента onchip_mem (рис. 4.20).

5. Конфигурация и подключение к системе ядра процессора NIOSII.

В списке доступных компонентов выбрать раздел Processors NIOSII Processor и дважды щелкнуть левой клавишей мыши. Появится окно конфигурации процессора.

88

Рис. 4.20. Установка связи памяти с генератором импульсов

На закладке Core NIOSII установить тип процессора NIOSII/e – (простейший вариант процессорного ядра). Переключить на закладку JTAG Debug Module и установить параметр Select a debugging level соответствующим No Debugger.

Нажать кнопку Finish. Ядро процессорного модуля создано и включено в систему. Появляющиесяошибкиипредупрежденияпока можно проигнорировать.

Переименовать созданный процессорный модуль: в закладке System Contents выбратьимя созданного модуля, нажать правую клавишу мыши идалее выбрать команду Rename. Новое имя nios2_qsys.

Соединить вход clk компонента nios2_qsys с выходом clk1 компонента clk, а выход clk_reset компонента clk с входом reset_n компонента nios2_qsys.

Соединить вход s1 компонента onchip_mem с выходами data_master и instruction_master компонента nios2_qsys.

Открыть окно настройки процессора NIOS дважды щелкнув левой клавишей мыши по компоненту nios2_qsys.

На закладке Core NiosII указать память для вектора сброса. На закладке Core NiosII указать память для вектора exception.

На закладке JTAG Debug Module указать соответствующий вывод системы и затем нажать кнопку Finish.

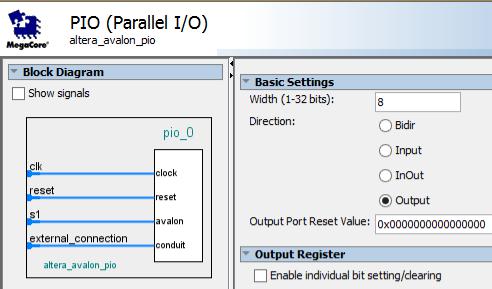

6. Конфигурация и подключение к системе модуля PIO (параллельного ввода-вывода):

а) в списке доступных компонентов выбрать раздел PIO (Parallel I/O) и дважды щелкнуть левой клавишей мыши (рис. 4.21);

89

Рис. 4.21. Окно выбора режима работы редактора

б) открыть окно настройки и в закладке Basic Settings установить следующие параметры:

•разрядность width = 8;

•направление передачи – Direction = Output;

•Reset value = 0;

•нажать кнопку Finish;

•появляющиеся ошибки и предупреждения пока можно проигнорировать. Переименовать созданный компонент: в закладке System Contents вы-

брать имя созданного компонента и нажать правую клавишу мыши, выбрав команду Rename. Новое имя pio.

Соединить вход clk компонента pio с выходом clk1 компонента clk, а выход clk_reset компонента clk с входом reset компонента pio.

Соединить вход s1 компонента pio с выходами data_master и instruction_master компонентаnios2_qsys. Появляющиесяошибкиипредупреждения пока можно проигнорировать.

Дважды щелкнуть в строке external_connection столбца Export, ввести имя внешнего вывода создаваемой системы led. Модуль PIO настроен и подсоединен к системе.

7.Выполнить автоматическое распределение адресного пространства си-

стемы: System Assign base Addresses

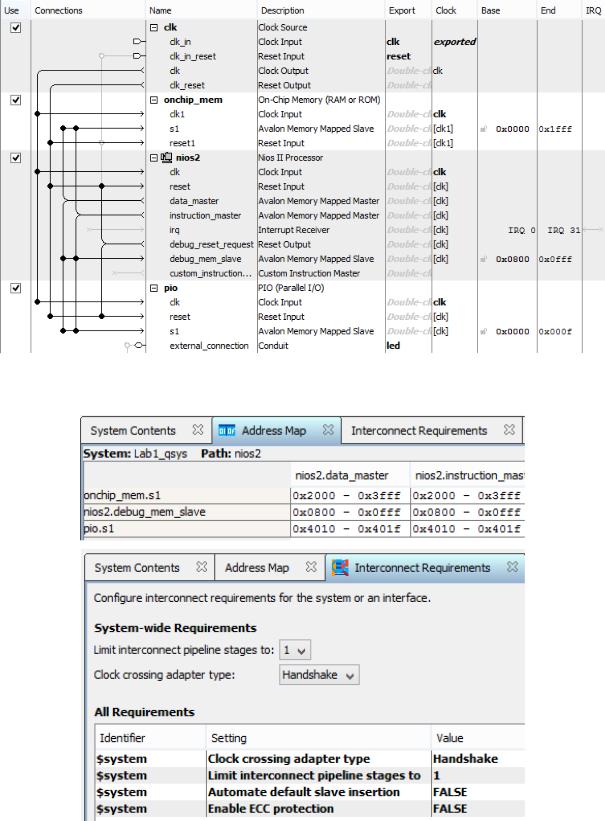

8.Внешний вид созданной РСнК, закладка System Contents (рис. 4.22).

9.Внешний вид созданной системы, закладка Address Map (рис. 4.22).

10.Внешний вид созданной системы, закладка Interconnect Requirements (рис. 4.23).

90

Рис. 4.22. Соединение блоков проекта РСнК

Рис. 4.23. Окно выбора режима работы редактора

11.Закладка Messages не содержит никаких предупреждений.

12.Выполнить команду File Save и открыть окно настройки формирования описания системы Generate Generate.

91

13. Оставить все значения по умолчанию и нажать кнопку Generate.

Этап 3. Интеграция аппаратной части проекта

На данном этапе существует два варианта интеграции аппаратной части системы на кристалле:

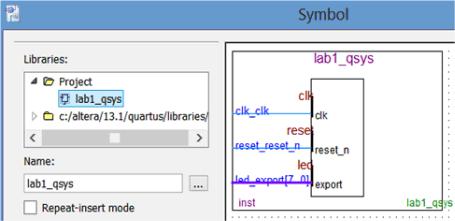

1. Создать в графическом редакторе файл верхнего уровня в иерархии проекта:

• выполнить команду File New, указать Block Diagram/schematic file и

нажать кнопку OK. Откроется окно графического редактора;

Рис. 4.24. Окно подключения выводов проекта

•дважды щелкнуть левой клавишей мыши в рабочем поле графического редактора. Откроется окно ввода символов Symbol;

•в разделе Libraries открыть папку Project. В ней находится символ созданной на кристалле системы Proj1_qsys;

•выбрать этот символ, нажать кнопку ОК, затем разместить его в поле графического редактора, нажав левую клавишу мыши;

•подключение внешних выводов проекта (рис. 4.24).

•сохранить схему под именем Proj1.bdf.

Второй вариант реализации данной процедуры осуществляется с помощью текстового редактора.

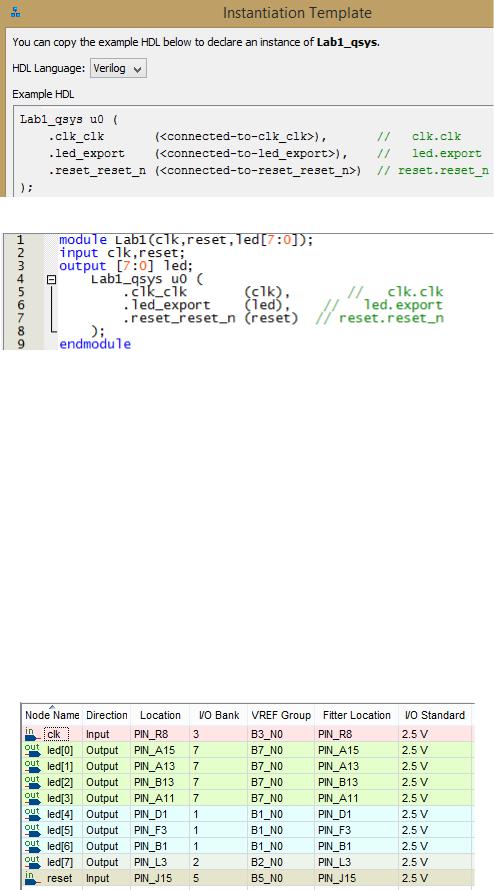

Разработаем код программы основного проекта top level file. Для этого необходимо выполнить следующее:

•определить внешний интерфейс сконфигурируемой системы на кристалле (по пункту 8);

•определить шаблон функции внешнего интерфейса проекта (рис. 4.25);

•вставить шаблон внешних выводов в главную программу Lab1.v;

В результате получим общий вид программы с подключением к выводам системы на кристалле (рис. 4.26).

92

Рис. 4.25. Окно с шаблоном функции внешнего интерфейса проекта

Рис. 4.26. Вставка шаблона функции внешнего интерфейса проекта

2. Проверка синтаксиса проекта

Подключить файл с описанием созданной в Qsys системы к проекту:

а) выполнить команду Project Add\Remove Files in Project;

б) в появившемся окне, в разделе File Name выбрать (с помощью брау-

зера) файл … \labs\Proj1\Proj1_qsys\synthesis\Proj1_qsys.qip, а затем нажать кнопку Add. Далее нажать кнопку ОК и выполнить команду Processing=>Start=>Start Analysis and Elaboration.

3. Назначение выводов проекта:

•запустить редактор назначения выводов Pin Planner: Assignment=>Pin Planner;

•назначить выводы так, как показано на рис. 4.27;

•закрыть редактор назначения выводов.

Рис. 4.27. Вид физического подключения выводов проекта к кристаллу ПЛИС

93

4. Назначение опции проекта:

•выполнить команду Assignment Device;

•в появившемся окне нажать кнопку Device and Pin Options;

•в окне Device and Pin Options выбрать закладку Unused pin, в которой нужно установить опцию As input tri-stated with weak pull-up resistor;

•нажать кнопку ОК. В следующем окне нажать кнопку ОК.

Интеграцияаппаратнойчастипроектаизаданиеустановокпроектазавершено.

Этап 4. Создание программной части проекта

1. Запустить оболочку для разработки/отладки программ NIOSII IDE:

а) Start (пуск) Programms (все программы) Intel NiosII EDS NIOSII IDE.

б) в оболочке NIOSII IDE выполнить команду Window OpenPerspective

other (рис. 4.28);

Рис. 4.28. Окно создания программной части проекта

94

в) в появившемся окне указать NIOS II, затем нажать кнопку ОК.

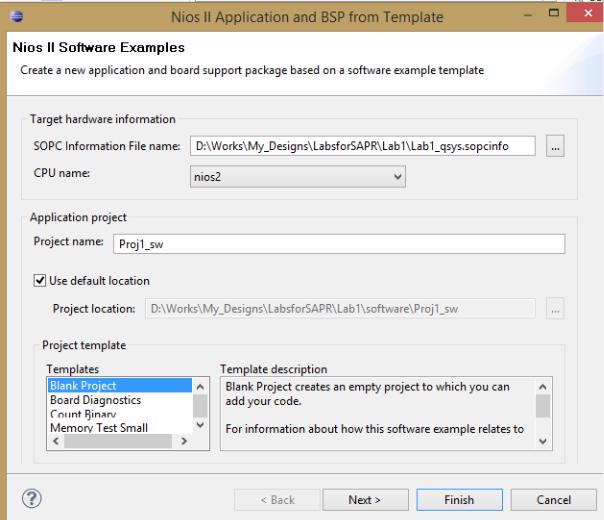

г) выполнить команду File New NIOS II Application and BSP from Tempate. Будет запущен помощник создания нового проекта New Project Wizard;

д) в окне помощника ввести:

•в разделе Select Target Hardware с помощью браузера найти в рабочей папке и указать путь к файлу Proj1_qsys.sopcinfo – файл с описанием созданной системы;

•в разделе Project Name ввести название проекта Proj1_sw;

•вразделеSelect Project Template выбратьBlank Project QuartusII ver (рис.

4.28).

•нажать кнопку Finish;

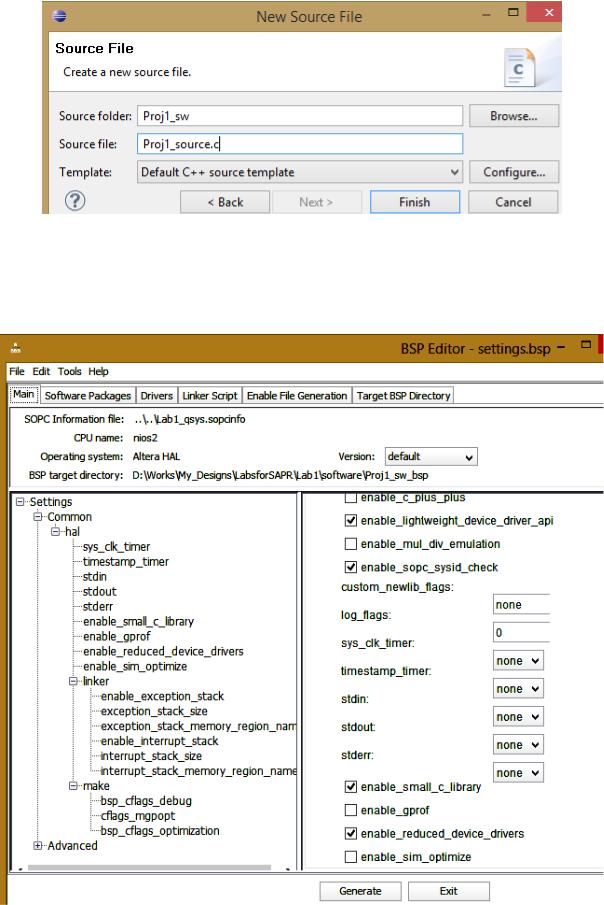

а) выполнить команду File New Other. В появившемся окне выбрать Source File в категории C/C++, затем нажать кнопку Next;

б) вокнеNewsourcefileспомощьюбраузерауказатьпапкуProj1_sw,вве-

сти название файла Proj1_source.c; Template Default C source template

(рис. 4.29);

в) нажать кнопку Finish;

г) будет создан и открыт в текстовом редакторе новый файл. Введите текст программы на языке Си:

#include "alt_types.h"

#include "Intel_avalon_pio_regs.h" #include "system.h"

#include <stdio.h> #include <unistd.h> static int count;

int main(void) { count = 255; while( 1 ) { usleep(500000);

IOWR_INTEL_AVALON_PIO_DATA( PIO_BASE, ~count ); count++; /* Continue 0-ff counting loop. */ }

return 0;

}

•сохранить изменения;

•выбрать папку Proj1_sw_bsp, нажать правую клавишу мыши и выбрать

команду NIOS II BSP Editor.

95

Рис. 4.29. Окно формирования нового ресурса программной части проекта

• в появившемся окне на закладке Main выбрать категорию Settings (все настройки) и установить опции как показано на рис. 4.30 (это поможет сократить объем порождаемого файла с исполняемым кодом программы);

Рис. 4.30. Окно установки соответствующих опции программной части проекта

96

•нажать кнопку Generate. Затем кнопку Exit;

•выбрать папку Proj1_sw, нажать правую клавишу мыши и указать команду Build Project. Будет запущен компилятор;

•при успешном завершении процесса в окнеConsole появится сообщение;

•выбрать папку Proj1_sw, нажать правую клавишу мыши и указать ко-

манду Make Targets Build. В появившемся окне выбрать mem_init_generate

инажмите Build. Будет запущена генерация файла инициализации памяти.

Этап 5. Полная компиляция проекта

1. В пакете QuartusII подключить файл с описанием созданной в Qsys си-

стемы к проекту:

•выполнить команду Project Add\Remove Files in Project;

•в появившемся окне в разделе File Name выбрать (с помощью браузера)

файл …

• нажать кнопку Add, затем кнопку ОК.

2.В окне менеджера пакета QuartusII с помощью команды Processing => Start Compilation осуществить полную компиляцию проекта.

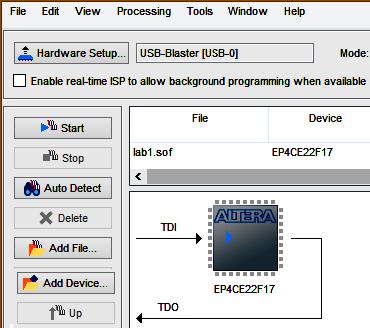

Этап 6. Конфигурирование СБИС

1.Подсоединить USB-Blaster к JTAG разъему платы QuarSapr II.

2.Включить питание платы.

3.Выполнить команду Tools Programmer.

4.Откроется окно управления конфигурированием СБИС (рис. 4.31).

Рис. 4.31. Окно конфигурации ПЛИС

97