- •ВВЕДЕНИЕ

- •1. ОБЛАСТИ ПРИМЕНЕНИЯ ЦИФРОВЫХ УСТРОЙСТВ

- •1.1. Системы автоматического управления

- •1.2. Системы передачи информации (СПИ)

- •1.3. Системы обработки информации (вычислительные системы)

- •2. МАТЕМАТИЧЕСКИЕ ОСНОВЫ УСТРОЙСТВ ОБРАБОТКИ СИГНАЛОВ

- •2. 1. Спектральные методы обработки сигналов

- •2. 2. Пространственные методы обработки сигналов

- •3. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ

- •3.1. Программируемые схемы со встроенным процессорным ядром

- •3. 2. Маршрут проектирования систем на кристалле

- •3.3. Примеры поведенческого описания и синтеза схем

- •4. СОВРЕМЕННЫЕ САПР СИСТЕМЫ НА КРИСТАЛЛЕ

- •4. 1. Проектирование в среде САР Active-HDL

- •4.1.1. Основы работы с Active-HDL

- •4.1.2. Технология автоматизированной верификации

- •4. 2. Проектирование в среде САПР Quartus II

- •4. 3. Проектирование в среде САПР Fastchip

- •Список использованной литературы

- •Список рекомендуемой литературы

- •СОДЕРЖАНИЕ

when x"3" => data <= (others=>'0');

when x"4" => data <= conv_std_logic_vector(1,8); when x"5" => data <= x"ff"; when x"6" => data <= x"11";

when x"7" => data <= x"01"; when x"8" => data <= x"10"; when x"9" => data <= x"00"; when x"A" => data <= x"10"; when x"B" => data <= x"15"; when x"C" => data <= x"60"; when x"D" => data <= x"90"; when x"E" => data <= x"70"; when x"F" => data <= x"90"; when others => data <= x"00"; end case;end if;end process;end architecture.

4. СОВРЕМЕННЫЕ САПР СИСТЕМЫ НА КРИСТАЛЛЕ

Программируемые логические интегральные схемы (ПЛИС) являются ИС высокого уровня интеграции для разработки на их базе специализированных устройств. ПЛИС соединяют достоинства массового заводского производства ИС с возможностью гибкого подбора структуры ИС для малосерийных специализированных устройств. На базе ПЛИС могут быть изготовлены логические блоки и системы, преобразователи кодов, периферийные контроллеры, микропрограммные устройства управления, конечные автоматы, умножители, небольшие процессоры, в том числе для быстрого преобразования Фурье. Проектирование устройства на ПЛИС заключается в составлении схемы соединений, входящих в ее состав логических элементов и последующем программировании матрицы специальным программатором, которое может быть выполнено самим пользователем.

Основное преимущество ПЛИС перед другими специализированными схемами– малоевремя изготовления требуемых заказных вариантов схем. ИсчезаетнеобходимостьобращатьсякизготовителямИМСдлянанесенияметаллической маски и установки кристалла вкорпус. Времяполучения нужной ИС из стандартной ПЛИС измеряется секундами и минутами. Широкое распространение ПЛИС стало возможным благодаря множеству автоматизированных систем проектирования (САПР). Разными производителями для решения собственных задач было разработано множество САПР.

САПР Aldec HDL. В отличие от компаний-гигантов небольшие фирмыпроизводителиСАПР,такиекакAldec[32],специализируютсявопределенной области проектирования и, обладая несколькими первоклассными продуктами, не могут обеспечить поддержкувсех этаповпроектирования. Рецепт вы-

58

живания таких компаний в конкурентной борьбе обычно включает поддержание невысоких цен при постоянном совершенствовании и обеспечении максимальнойгибкостипродуктов.Этопозволяетсостыковыватьихспопулярными продуктами других компаний, встраивать в существующие маршруты проектирования, а также организовывать на их базе новые маршруты, ориентированные на индивидуальные требования разработчиков.

Компания «Aldec» (Automated Logic Design Company, inc) специализиру-

ется на средствах моделирования, верификации и отладки проектов ИС. Первой в линейке продуктов компании быласистема моделирования SUSIE, которая работала еще в операционной системе DOS. Появившаяся затем система Active-CAD (последняя версия Active-HDL), реализованная в системе Windows, приобрела большую популярность и была лицензирована компанией Xilinx для своего маршрута проектирования. Только за первые два года продаж было поставлено более десяти тысяч копий системы.

СейчасварсеналекомпанииAldecиспользуются:системамоделирования ПЛИС и ASIC на любых вычислительных платформах; средства совместной программно-аппаратной верификации проектов, содержащие процессорные ядра; аппаратные ускорители моделирования. Традиционно особое внимание уделяется поддержке проектирования ПЛИС.

Система Active-HDL – продукт, ориентированный на максимальную гибкость при разработке сложных проектов на базе любых типов современных ПЛИС различных компаний-производителей. Важно, что помимо развитых встроенных средств моделирования и отладки, Active-HDL также предоставляет разработчикам единую среду для построения собственных маршрутов проектирования ПЛИС в зависимости от характера решаемых задач и используемых программных средств.

Центральное место в структуре системы Active-HDL занимает средство управления маршрутом проектирования. Оно позволяет разработчику определить набор средств, используемых на каждом этапе проектирования ПЛИС (моделирование, синтез, проектирование топологии, специальные средства), которые в дальнейшем будут работать в рамках единого маршрута и среды проектированиясистемыActive-HDL.Всистемевлюбыхкомбинацияхмогут быть использованы все доступные на сегодняшний день производители ПЛИС и большинство популярных продуктов компаний – производителей САПР.

59

Состав средств, которые могут быть встроены в маршрут проектирования, постоянно расширяется [32]. Интеграция различных продуктов в единой среде позволяет полностью контролировать процесс проектирования на всем его протяжении от спецификации до физической реализации. Разработчик может настроить маршрут проектирования именно на тот состав программных средств, которые наиболее полноотвечают требованиям конкретногопроекта. Помимо собственных технологически независимых библиотек Active-HDL включает полные библиотеки всех производителей ПЛИС с перекомпилированными и готовыми к использованию компонентами.

Средство проектирования предусматривает следующий набор операций:

•добавление, удаление, просмотр, модификация файлов ресурсов проекта;

•просмотр содержимого рабочей библиотеки, библиотеки результатов логического синтеза и библиотеки временных параметров текущего проекта;

•просмотр структуры моделируемого проектного модуля;

•просмотр заданных объектов внутри моделируемого проектного модуля. Для работы с библиотеками предусмотрены операции:

•подключение, отключение, удаление библиотек;

•редактирование логических имен библиотек;

•сжатие и удаление содержимого библиотек;

•просмотр содержимого библиотек;

•просмотр библиотечных модулей;

•удаление библиотечных модулей;

•поиск модулей в библиотеках.

Документированиепроекта– однаизсамыхтрудоемкихиутомительных задач. В системе Active-HDL поддерживается методология описания проектов, которая обеспечивает их самодокументируемость (рис. 4.1). Экспорт проектов и отдельных документов в различных графических форматах, форматах HTML и Adobe PDF значительно облегчает создание сопроводительных документов.

Экспорт в формат PDF позволяет подготовить проектную документацию в печатном виде с отображением структуры проекта в содержании. В электронной версии документа предусматривается возможность навигации по содержанию. При экспорте в формат HTML воспроизводится точная копия структуры проекта, вид и поведение среды проектирования; текстовые доку-

60

менты сохраняют оригинальное форматирование, шрифты и выделение синтаксических конструкций используемых языков. С таким документом можно работать в любом Web-браузере. Режимы экспорта структуры и графического представления проекта можно настроить таким образом, чтобы скрыть детали реализации.

Рис. 4.1. Окно среды САПР Active-HDL

Система Active-HDL, как и большинство современных САПР СнК, поддерживаетразнообразныесредствасозданияиредактированияпроектаПЛИС, которые включают текстовый редактор аппаратных спецификаций на базе языков VHDL, Verilog, SystemC, а также C/C++, Matlab (HDE), графические редакторы диаграмм автоматов конечных состояний (FSM) и блок-диаграмм

(ВОЕ).

Текстовый редактор распознает и выделяет синтаксические конструкции, в нем предусмотрены функции автозаполнения, а также поддержка полных наборов шаблонов используемых языков в соответствии со стандартами. Поддерживается описание схемы в формате EDIF, импорт схемных символов, иерархическая визуализация описания проекта, генерация графического представления в виде блок-диаграмм и диаграмм автоматов конечных состояний по описанию HDL. Генератор IP-блоков позволяет автоматически создавать синтезируемые модели для различных арифметических функций, последовательной логики, блоков памяти, фильтров, конверторов кодов, элементов системы тестирования, а также для некоторых специальных промышленных и коммуникационных приложений.

61

Моделирование смешанных проектов, включающих описания на языках VHDL, Verilog, списки цепей в формате EDIF и модели SystemC, поддерживается на уровне самого ядра моделирования Active-HDL. Встроенные интерфейсы моделирования позволяют дополнительно использовать поведенческие модели на языке C/C++, функциональные модели SWIFT, модели памяти Denali, а также встроенные М-функции системы Matlab. Механизм совместного моделирования дает возможность подключить к Active-HDL систему Matlab/Simulink компании «Mathworks» для верификации аппаратных блоков

вих системном окружении.

Всистему также входит генератор тестовых воздействий, который руководит последовательностью действий инженера в диалоговом режиме и создаетшаблонтеста.Одинитотжетестможетиспользоватьсяналюбомуровне абстракций (поведенческом, уровне регистровых передач или временном). Возможна также генерация тестов из графических временных диаграмм или диаграмм автоматов конечных состояний.

Набор инструментов отладки включает: встроенный отладчик С-кода; трассировку кодов VHDL/ Verilog и диаграмм автоматов состояний; просмотр и редактирование(внесение временныхзначенийдляотладки) текущихсостояний сигналов, переменных, процессов и состояний памяти; просмотр стека вызовов подпрограмм; анализ потоков данных; анализ тестового покрытия; профилирование проекта.

Впроцессе моделирования также можно генерировать графическое представление потоков данных в модели, которое позволяет исследовать связность моделиипровестианализобменаданнымимеждулюбымиееобъектами(компонентами, регистрами, сигналами, операторами). Визуализация путей распространения сигнала с помощью диаграмм потоков данных позволяет легче определить потенциальные источники ошибок на внутренних сигналах.

Спомощью профилирования проекта можно получить информацию о времени моделирования каждого оператора, процесса и блока, определить и провести оптимизацию наиболее критичных фрагментов.

Средства анализа тестового покрытия, интегрированные в ядро моделирования, помогают разработчику выявить части проекта, которые не были задействованы во время выполнения теста. Данные можно получить как по тестовомупокрытию строк кода, так и по переключениям, а также по интегральному покрытию на множестве тестов.

62

САПР фирмы Synplicity. Разработчики ПЛИС по всему миру используют программные средства компании «Synplicity». Образованная в 1994 г., «Synplicity» сразу выпустила ряд успешных продуктов, ориентированных на решение задачи логического синтеза для ПЛИС. Учитывая, что электронные устройства на базе современных ПЛИС − один из наиболее активно развивающихся секторов микроэлектроники, можно утверждать, что «Synplicity» сегодня входит в число самых заметных игроков на рынке средств автоматизированного проектирования микроэлектронных компонентов.

Компания «Synplicity» интенсивно развивается, осваивает новые направления системного и физического синтеза. Особенно трудная задача при разработке систем синтеза [33] −обеспечитьвозможность эффективнойреализации исходного RTL-описания во всех доступных элементных базисах. В полной мере решить эту задачу, как впрочем и для компиляторов, тяжело, но «Synplicity», пожалуй, продвинулась в ее решении дальше всех. Одно из интереснейших направлений развития компании – разработка аппаратного отладчика RTL-кода на базе ПЛИС.

Сегодня отладка и функциональная верификация RTL-кода в отличие от разработки программ осуществляется в искусственной среде средств логического моделирования. Понятно, что при реализации в виде ASIC отладку на аппаратном уровне не сделаешь, а вот решения для перепрограммируемых FPGA весьма интересны.

Сегоднякомпания«Synplicity»предоставляетсредствадлярешенияпрактическивсехзадачсинтезакакдляПЛИС,такидляASIC иструктурныхASIC. Линейка продуктов компании включает пакеты:

•Synplify DSP − автоматический синтез RTL-кода для систем цифровой обработки сигналов (Digital Signal Processing, DSP);

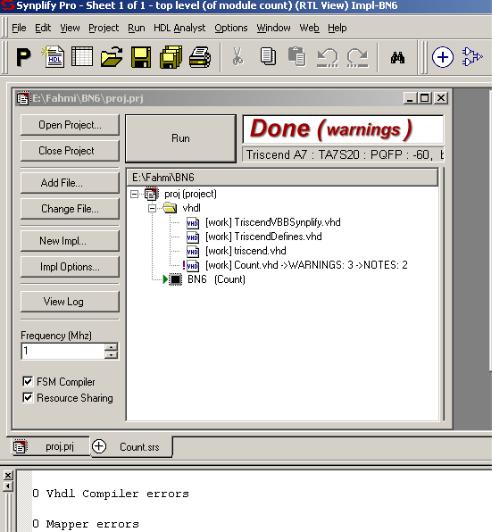

•Synplify Pro, Synplify ASIC − логический синтез для FPGA и заказных СБИС соответственно (рис. 4.2).

•AmplifyFPGA,AmplifyASIC −физическийсинтездляFPGAизаказных СБИС соответственно. Существуют также специальные версии Amplify ASIC для таких структурных ASIC, как RapidChip фирмы «LSI Logic», ISSP фирмы

«NEC», AccelArray фирмы «Fujitsu»;

•Certify − прототипирование ASIC-проектов на FPGA;

•dentify − отладчик RTL-кода.

Fortify −проектирование системы питания для ASIC с учетом влияния таких факторов, как электромиграция, падение напряжения в шинах питания и

63

др. Поскольку компания «Synplicity» стартовала как разработчик средств логического синтеза, в этой области накоплен наибольший опыт.

Рис. 4.2. Окно среды САПР Synplify Pro

Fortify −проектирование системы питания для ASIC с учетом влияния таких факторов, как электромиграция, падение напряжения в шинах питания и др. Поскольку компания Synplicity стартовала как разработчик средств логического синтеза, в этой области накоплен наибольший опыт.

Synplify Pro ориентирована на работу с современными ПЛИС емкостью в несколько миллионов вентилей, работающих с частотами свыше 100 МГц. Благодаря алгоритмам, заложенным в систему, можно выделять крупные функциональные блоки (конечные автоматы, память, арифметические блоки) и проводить высокоуровневую оптимизацию. Использование метода ретайминга (retiming), при котором оптимизируется расположение регистров внутри комбинационной логики, позволяет добиваться 25-процентного увеличения производительности.

64

Инкрементный синтез, базирующийся на собственной технологии компании «Multipoint» и использующий установленные пользователем в компиляторе RTL-кода точки, обеспечивает возможность за счет оптимизации интерфейсов скомпилированных блоков добиться высокого уровня стабильности проекта и избежать ухудшения производительности, что свойственно другим инкрементным методам.

Для самых сложных проектов полезны будут такие возможности Synplify Pro, как управление вариантами реализации, интеграция IP и повторное использование ранее разработанных блоков (design reuse). Система логического синтеза для ASIC (Synplify ASIC), появившаяся несколько позже, была разработана на основе идеологии и алгоритмов, заложенных в Synplify Pro, таких кактехнологиясинтезаB.E.S.T., котораяпозволяетприкомпиляцииизвлекать поведенческую информацию из RTL-кода и проводить высокоуровневую оптимизацию всего проекта. А уникальная технология прямого отображения проекта в элементный базис производителя («Direct Mapping Technology», «D.M.T.»)даетвозможностьминоватьсвойственныедругимсистемамсинтеза этапыпреобразованияпроектавбазисвнутреннейбиблиотекиипоследующей оптимизации в базисе производителя.

Система сразу видит и использует все доступные элементы, а не элементарные логическиефункции. Благодаря этому, в Synplify ASIC высокая производительность синтеза сочетается с глубокой оптимизацией проекта (в среднемприпятикратномуменьшениивременисинтезарезультирующаясхемаполучается на 15 % компактнее, чем в традиционных системах логического синтеза заказных СБИС).

Получение более компактной схемы облегчает задачу размещения/трассировки на последующих этапах и повышает качество всего проекта в целом.

В системе Synplify ASIC обеспечена возможность поддержки единой иерархии проекта и системы проектных ограничений на этапах синтеза и размещения/трассировки. Методология проектирования сверху вниз позволяет проводить синтез с учетом временных ограничений при размерах отдельных блоков до двух миллионов вентилей.

Как Synplify ASIC, так и Synplify Pro включают в себя систему отладки HDL Analyst, которая обеспечивает удобные средства анализа и отладки про- екта.Здесьподдерживаетсявозможностькросс-ссылокмеждуисходнымRTL- текстом, его схемным графическим представлением, синтезированной схемой в библиотечном базисе и диагностическими листингами. В среде HDL Analyst

65

также выполняется анализ критических путей и различные виды фильтрации схемных диаграмм, так что разработчик может полностью контролировать проект во всех его представлениях.

Надо заметить, что сложность проектов на FPGA возрастает вслед за ASIC, и те проблемы, с которыми уже столкнулись разработчики ASIC, становятся актуальными и для разработчиков FPGA. Имея полную линейкупродуктов синтеза для различных технологий, компания «Synplicity» видит весь спектр проблем проектирования в этой области. Поэтому многие технологии проектирования, изначально разработанные и апробированные в Synplify ASIC, сейчас реализуются в SynplifyPro.

С ростом степени интеграции и переходом на технологические нормы проектирования ниже 0,18 мкм усиливается влияние топологии на временные параметры логических схем. Задержки в линиях связей начинают преобладать над задержками логических элементов. В этих условиях приобретает актуальность создание систем физического синтеза, где одновременно с логическим синтезом производится размещение элементов и оптимизация синтезированной схемы по его результатам. Возникновение систем физического синтеза было инициировано прежде всего требованиями разработчиков ASIC. Но сегодня потребность в таких системах возрастает и для разработчиков FPGA.

СистемаAmplify ASIC вединойоболочкеподдерживаетвесьпроцесслогического и физического синтеза, включая планировку кристалла, размещение, предварительнуютрассировку,оценкузагруженностиивременнойанализ.Средствапланировкидаютвозможностьавтоматическисгенерироватьвесьпланкри- сталланепосредственноизRTL-кодалибозавершитьпредварительносделанную частичную планировку. Быстрые средства автоматического размещения позволяют проводить синтез и одновременное размещение компоненов, а предварительная глобальная трассировка и временной анализ обеспечивают достоверное прогнозирование результатов проектирования. Предусмотрены также средства учета при размещении требований к трассировке тактовых сигналов.

Следует заметить, что Amplify ASIC – один из первых продуктов на зарождающемся перспективном рынке средств физического синтеза для структурных ASIC. Сегодня уже поддерживается синтез для кристаллов ISSP

фирмы «NEC», RapidChip фирмы «LSI Logic» и Luminance компании

«Lightspeed Semiconductor».

В ближайшее время будет обеспечена поддержка серии AccelArray фирмы «Fujitsu» и ряда других производителей структурных ASIC. Базовый продукт Amplify ASIC − универсальный, он обеспечивает проектирование

66

любых ASIC, включая и структурные. В то же время аналогично версиям Synplify и Synplify Pro для различных производителей FPGA разработаны специальные версии Amplify для каждого производителя структурных ASIC, в полной мере учитывающие возможности конкретных типов кристаллов.

Компания «Synplicity» − пионер в области физического синтеза для ПЛИС. Ее системаAmplify FPGA на протяжениинескольких лет используется крупными электронными компаниями по всему миру, являясь фактически стандартом в этой области.

Для современных ПЛИС недостаточно средств логического синтеза, в котором анализируются только статистические модели межсоединений и задержкипереключениявентилей,посколькуреальныезадержкивомногомопределяются топологией и могут резко отличаться от предварительных оценок.

В отсутствие средств, учитывающих топологическую реализацию, процесспроектированиясовременныхПЛИСимеетшансстатьнепредсказуемым, поскольку исправление ситуации в одном месте может повлечь за собой возникновение проблем в других частях схемы. Использование системы Amplify FPGA позволяет достичь в автоматическом режиме работы результатов, сопоставимых с полностью ручными режимами размещения и трассировки, и в среднем увеличить производительность разрабатываемых устройств на 20 %, а в некоторых случаях – до 45 % по сравнению с результатами, полученными при использовании обычного логического синтеза. Улучшение достигается за счет одновременной оптимизации размещения и синтезируемой логики. Используются методы оптимизации, учитывающие межсоединения логических элементов,проводитсяавтоматическаярепликация(replication)логикииоптимизация критических путей.

Сегодня появилось уже третье поколение системы Amplify FPGA, в котором реализованы новейшие методы физического синтеза для самых современных архитектур ПЛИС, таких как Virtex-4 компании «Xilinx» и Stratix II компании «Altera». Для FPGA фирмы «Xilinx» в Amplify FPGA реализованы все этапы автоматического синтеза вплоть до размещения, причем с гарантией соблюдения временных параметров. Остается только выполнить трассировку. Надоотметить,чтосамиразработчикиПЛИС– компании«Xilinx»и«Altera» – при разработке своих библиотек IP-блоков применяют системы Amplify и Synplify Pro.

Система Identify позволяет на практике реализовать концепцию верификации проекта на основе отладки. Суть этой концепции в том, что с помощью

67