- •1. АССОЦИАТИВНАЯ ПАМЯТЬ. ОПРЕДЕЛЕНИЯ И КОНЦЕПЦИИ

- •1.2. Определение и модель ассоциативной памяти

- •Непрямые (или косвенные) ассоциации

- •Отношение

- •1.3.4. Классические законы ассоциаций

- •Обобщая наблюдения над явлениями человеческой памяти, греческий философ Аристотель (384–322 гг. до н.э.) выдвинул ряд постулатов, впоследствии послуживших основой при построении классических законов ассоциаций [3].

- •2.1. Основные принципы хеширования

- •2.1.2. Функции хеширования

- •Перевод ключевых слов в числовую форму

- •Преобразование числовых значений в хеш-адреса

- •2.2.4. Методы ускорения процедур поиска

- •2.3. Структура и форматы таблиц хеширования

- •2.3.1. Непосредственная и косвенная адресация

- •2.3.2. Форматы таблиц хеширования

- •2.4.2. Списки и списочные структуры

- •2.4.5. Применение методов хеширования для поиска по соответствию

- •3.1.2. Логические основы организации АЗУ

- •Таблица 3.1

- •параллельного действия

- •3.2.2. Анализатор многократных совпадений

- •Приоритетные анализаторы последовательного типа

- •Структурная схема АЗУ с поиском, параллельным по словам и разрядам, приведена на рис. 3.8.

- •Построение АЗУ на базе ЗУ с линейной выборкой

- •Процедура записи в память разрядного столбца

- •Считывание разрядного столбца

- •3.6. АЗУ, параллельные по записям и последовательные по байтам

- •3.8. Схемотехническая база АЗУ

- •4. МЕСТО АССОЦИАТИВНОЙ ПАМЯТИ

- •4.2. Программируемая логика

- •4.2.2. Программирование логики при помощи ассоциативной памяти

- •функциональной памяти

- •4.2.4. Другие способы реализации программируемой логики

- •4.3. Применение АЗУ для выполнения различных

- •управляющих функций

- •5. АССОЦИАТИВНЫЕ ПРОЦЕССОРЫ

- •5.1. Основные тенденции развития ассоциативной памяти

- •5.3. Ассоциативные процессоры с высоким уровнем параллелизма

- •5.4.1. Базовая структура матричного процессора

- •Рассмотрим связи между ячейками МП.

- •5.4.3. Ассоциативный управляющий переключатель

- •5.4.4. Ассоциативный матричный процессор RADCAP

- •5.4.5. Ассоциативный групповой процессор PEPE

- •5.5.1. Вычислительная система STARAN

- •Отличие этого уровня от предыдущих:

5.4.Ассоциативные процессоры с операционными устройствами высокого уровня

Параллелизм в рассмотренной выше памяти с распределенной логикой (ПРЛ, или DLM) реализован на уровне выполнения поразрядных операций (если говорить об обработке числовой информации), для которых последовательности микроопераций задаются при помощи внешних устройств глобального управления.

Другой подход характеризуется практически независимым выполнением операций в отдельных ячейках. Параллельный процессор формируется из массива ячеек, хранящих каждая в своей локальной памяти (ЛП) небольшое количество (до нескольких сотен) операндов. Процессор снабжен гибким АЛУ.

Если в ПРЛ логика управления концентрируется в каждой ячейке памяти, в результате чего ячейка может оперировать только с разрядной информацией, то в рассматриваемых далее примерах другого подхода каждый модуль, используя локальную систему управляющих сигналов, может схемно (аппартно) выполнять арифметические и логические операции. Кроме того, связь между ячейками рассматриваемого типа осуществляется при помощи машинных команд и числовых переменных, что важно с точки зрения программирования при решении сложных задач.

Представителями такого типа ассоциативных процессоров являются матричные процессоры.

5.4.1. Базовая структура матричного процессора

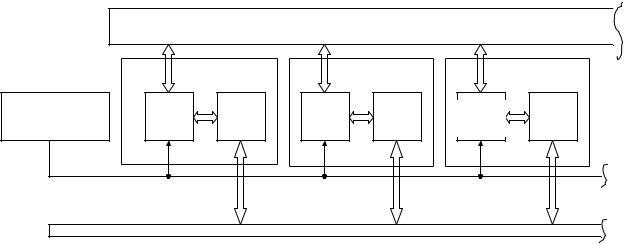

Структура простейшего матричного процессора приведена на рис. 5.3.

В зависимости от конфигурации сети линий связи матричный процессор

(МП) может быть бесструктурным, линейным, прямоугольным и т.д. Если связь между ячейками (элементарными процессорами – ЭП) осуществляется только при помощи управляющей шины или шины ввода-вывода, систему называют групповым процессором. В каждый ЭП входит операционный блок (ОБ) и па-

мять операционного блока (ПОБ) для хранения данных в процессе вычислений. Работа всех ЭП осуществляется под общим программным управлением, содержащимся в памяти, управление ОБ – при помощи содержащихся в нем фиксированных микропрограмм.

114

|

|

|

Сеть связи |

|

|

||

|

|

ЭП |

|

|

|

|

|

Блок |

ОБ |

ПОБ |

ОБ |

ПОБ |

ОБ |

ПОБ |

|

управления |

|||||||

|

|

|

|

|

|

||

Шина ввода – вывода

Рис. 5.3 Упрощенная структура матричного процессора

Для управления МП можно также использовать универсальную ведущую ЭВМ, для которой матричный процессор является периферийным устройством (ПФУ). В приведенной на рис. 5.3 структуре МП можно применить АЗУ небольшого объема в каждом устройстве обработки для получения ответа на символически заданные команды или данные.

Рассмотрим связи между ячейками МП.

При независимом друг от друга функционировании ЭП взаимодействуют лишь с ведущей ЭВМ по каналам ввода-вывода.

При решении пространственных задач, а также задач, требующих вычисления многократных интегралов и задач решения дифференциальных уравнений, для которых переменные задаются в узлах решетчатой функции, вычислительные алгоритмы ориентируются на описание взаимосвязи между соседними узлами.

Для решения специальных задач можно задавать фиксированную топологическую структуру массива, для решения широкого круга задач связь между ячейками может задаваться программно, как, например, в процессоре RADCAP, который будет рассмотрен ниже.

Ячейки могут связываться непосредственно или через линии связи, образованные при помощи мультиплексоров.

Отметим, что структура микропроцессоров часто соответствует топологии решаемых вычислительных задач.

115

5.4.2.Трехканальный процессор

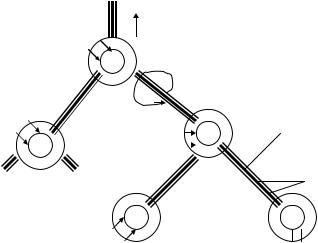

Впроцессорах, представляющих собой очень большие массивы ячеек, задержка при передаче информации между отдаленными ячейками с использованием пошаговых операций (как например в ПРЛ) может оказаться ощутимой. Один из вариантов решения, позволяющего значительно сократить задержки, приведен на рис. 5.4.

|

Корень |

|

|

n |

А |

|

|

В |

|

Канал связи |

|

n-1 |

3 |

||

|

|||

|

|

Рельсы |

|

2 |

|

1 |

Рис. 5.4. Структура связей в трехканальном процессоре – древовидная

Для ассоциативной выборки каждая ячейка этого процессора, названного трехканальным, должна содержать регистр сравнения, цепи сравнения и триг-

гер совпадения. Для определения режима работы ячейки (передачи, приема, обработки информации или свободного состояния) необходимы другие триггеры состояния.

Для глобальных операций передачи информации, например, при одновременной передаче аргумента поиска во все ячейки, используется канал связи. Для передачи промежуточных результатов и локального взаимодействия между ячейками предназначены две вспомогательные линии связи, называемые рельсами. Рельсы всегда используются для двухсторонней связи ячеек, имеющих последовательные индексы.

Чтобы сократить время передачи сигналов, особенно в случае, когда массив разбит на небольшие поддеревья, можно ввести сокращающие линии связи для сигналов, например, линию, соединяющую точки A и B на рис. 5.4.

116