- •1. АССОЦИАТИВНАЯ ПАМЯТЬ. ОПРЕДЕЛЕНИЯ И КОНЦЕПЦИИ

- •1.2. Определение и модель ассоциативной памяти

- •Непрямые (или косвенные) ассоциации

- •Отношение

- •1.3.4. Классические законы ассоциаций

- •Обобщая наблюдения над явлениями человеческой памяти, греческий философ Аристотель (384–322 гг. до н.э.) выдвинул ряд постулатов, впоследствии послуживших основой при построении классических законов ассоциаций [3].

- •2.1. Основные принципы хеширования

- •2.1.2. Функции хеширования

- •Перевод ключевых слов в числовую форму

- •Преобразование числовых значений в хеш-адреса

- •2.2.4. Методы ускорения процедур поиска

- •2.3. Структура и форматы таблиц хеширования

- •2.3.1. Непосредственная и косвенная адресация

- •2.3.2. Форматы таблиц хеширования

- •2.4.2. Списки и списочные структуры

- •2.4.5. Применение методов хеширования для поиска по соответствию

- •3.1.2. Логические основы организации АЗУ

- •Таблица 3.1

- •параллельного действия

- •3.2.2. Анализатор многократных совпадений

- •Приоритетные анализаторы последовательного типа

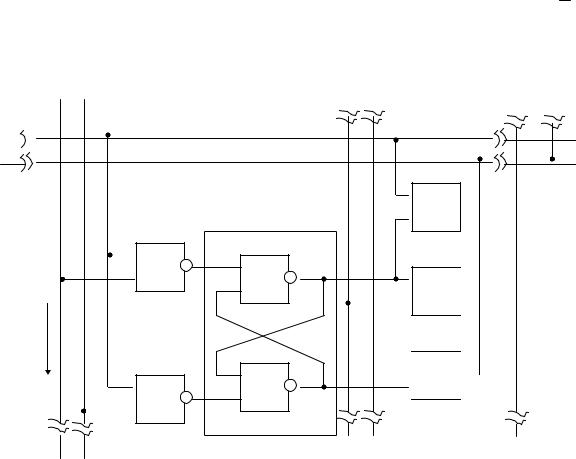

- •Структурная схема АЗУ с поиском, параллельным по словам и разрядам, приведена на рис. 3.8.

- •Построение АЗУ на базе ЗУ с линейной выборкой

- •Процедура записи в память разрядного столбца

- •Считывание разрядного столбца

- •3.6. АЗУ, параллельные по записям и последовательные по байтам

- •3.8. Схемотехническая база АЗУ

- •4. МЕСТО АССОЦИАТИВНОЙ ПАМЯТИ

- •4.2. Программируемая логика

- •4.2.2. Программирование логики при помощи ассоциативной памяти

- •функциональной памяти

- •4.2.4. Другие способы реализации программируемой логики

- •4.3. Применение АЗУ для выполнения различных

- •управляющих функций

- •5. АССОЦИАТИВНЫЕ ПРОЦЕССОРЫ

- •5.1. Основные тенденции развития ассоциативной памяти

- •5.3. Ассоциативные процессоры с высоким уровнем параллелизма

- •5.4.1. Базовая структура матричного процессора

- •Рассмотрим связи между ячейками МП.

- •5.4.3. Ассоциативный управляющий переключатель

- •5.4.4. Ассоциативный матричный процессор RADCAP

- •5.4.5. Ассоциативный групповой процессор PEPE

- •5.5.1. Вычислительная система STARAN

- •Отличие этого уровня от предыдущих:

3.2. Структура и основные функции АЗУ параллельного действия 3.2.1. Логическая структура одноразрядной ячейки АЗУ

параллельного действия

Рассмотрим структуру памяти (АЗУ), рассчитанную на непосредствен-

ную схемную реализацию выражений (3.3) – (3.6). Одноразрядная ячейка такой памяти представлена на рис. 3.3.

Ячейка АЗУ включает в себя узел записи (И1, И2), запоминающий элемент

(И3, И4), узел считывания (И5) и узел ассоциативного сравнения по критерию «равно», реализующий функцию «Исключающее ИЛИ» (И6, И7), а также схемы для реализации функции « Встроенное И» (например, схемы с разомкнутым коллектором, если используются биполярные транзисторы).

Кроме логики, предназначенной для выполнения операции сравнения, в каждой ячейке имеются адресные линии для считывания и записи информации.

Обозначения на рис. 3.3: Аj – адресный сигнал j-го слова; Wi (1) – запись “1” в разряд i; Wi (0) – запись “0” в разряд i; Сi(1) – сравнение с “1” i-го разряда;

Сi(0) – сравнение с “0” i-го разряда; Mj – сигнал совпадения j-го слова; Bi – вы-

ход информации (разряда i).

Wi(1) Wi(0)

(Адрес слова j)

Aj Mj

Mj

слов |

И1 |

|

|

Номера |

И3 |

||

|

|||

|

|

||

|

И2 |

И4 |

|

|

|

|

|

|

1 1 |

|

|

|

|

|

Ci(0) Ci(1) |

R |

R |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Мj

И5

И6

И7

И7

Запоминающая Ci(0),Ci(1) |

B |

i |

ячейка |

|

|

71

Рис. 3.3. Схема одноразрядной ассоциативной ячейки Рассмотрим выполнение операций записи / чтения в АЗУ.

Запись

Запоминающий элемент (триггер) предназначен для хранения одного бита информации. Этот триггер устанавливается и сбрасывается сигналами Wi (1) и Wi (0), поступающими с вентилей И1 и И2, при условии, что на адресную линию Aj подан сигнал с логическим уровнем “1”.

Значением записанного бита является выход И3. Оно равно 1, если

Wi (0) = 0, Wi (1) = 1 и Aj = 1, а при Wi (0) = 1, Wi (1) = 0 и Aj = 1– равно 0.

Чтобы содержимое данного разряда в ходе записи не изменялось, запись маскируется путем задания Wi (1) = Wi (0) = 0.

Считывание

Считывание информации из разрядной ячейки в режиме обычной адресации производится путем подачи на линию Aj сигнала с логическим уровнем “1”, в результате инвертированное значение бита с выхода И5 непосредственно поступает на общую для всех слов памяти линиюBi .

Считывание в режиме адресации по содержанию (сравнение бита поискового аргумента с содержимым ассоциативной ячейки) с учетом маскирования производится при помощи линий Сi(0) и Сi(1), проходящих через i-й разряд всех слов памяти.

При сравнении с единицей подаются сигналы Сi(0) = 0, Сi(1) =1, при сравнении с нулем – Сi(0) = 1, Сi(1) =0, чтобы разряд не участвовал в операции сравнения при маскировании, на линии Сi(0) и Сi(1) подается “0”. При совпадении сравниваемых значений потенциалы на выходах схем И6 и И7 отличны от 0 (оба ключа разомкнуты) и на линии Mj появляется сигнал “1”; при несовпадении – выход одного из вентилей И6 или И7 замыкается на “землю” и потенциал линии Mj становится равным 0; при маскировании – выходы И6 и И7 размыкаются независимо от записанного бита.

3.2.2. Анализатор многократных совпадений

В АЗУ может храниться несколько слов, ассоциативные признаки которых по незамаскированным разрядам совпадают с поисковым аргументом. Задача анализатора заключается в выявлении таких слов и их приоритетной выборке.

72