- •А.Н. Компанейц

- •Введение

- •1. Устройства числового программного управления

- •1.1. Задачи, решаемые учпу

- •Функции учпу

- •Структура учпу

- •Интерфейс магистральный параллельный

- •2.1. Назначение, принцип действия, основные характеристики

- •2.2. Одиночный адресный обмен

- •2.3. Одноуровневая процедура прерывания

- •3. Интерфейс и41

- •3.1. Назначение, принцип действия и характеристика интерфейса

- •3.2. Порядок обмена сообщениями

- •3.3. Операции прерывания

- •3.4. Операции смены задатчика

- •4. Устройство числового программного управления мс2101

- •4.1. Технические данные учпу

- •4.2. Устройство и работа учпу

- •Список литературы

- •Содержание

3.2. Порядок обмена сообщениями

При обмене информацией с памятью или устройствами ввода-вывода используются линии сигналов данных /DATF- /DAT0. В случае выполнения операции записи сигналы данных вырабатываются задатчиком, а при чтении - адресуемым исполнителем, т.е. памятью или устройством ввода-вывода.

На рис. 3.1 показана схема организации адресного обмена в интерфейсе И41.

Существует три типа передачи данных по магистрали: передача четного байта по линиям /DAT7 - /DAT0; передача нечетного байта по линиям /DAT7 - /DAT0 с использованием усилителей пересылки байтов; передача 16-разрядного слова по линиям /DATF- /DAT0.

Передачей данных управляют два сигнала /BHENи /ADR0. Активный сигнал разрешения старшего байта /BHENуказывает, что магистраль работает в 16-разрядном режиме, а нулевой разряд адреса /ADR0 определяет передачу четного или нечетного байта.

При передаче четного байта (рис. 3.2,а) /BHENи /ADR0 являются неактивными (BHEN=1,ADR0=1). Передача осуществляется по линиям /DAT7 - /DAT0. При передаче нечетного байта (рис. 3.2,б) /BHENявляется неактивным (BHEN=1), а /ADR0 активным (/ADR0=0). В этом случае нечетный байт выдается по усилителям пересылки байта на линии /DAT7 - /DAT0.

Данный тип передачи используется для совмещения 8- и 16-разрядных задатчиков и исполнителей.

Рис. 3.1. Схема организации адресного обмена

Рис. 3.2. Операции передачи данных: а - передача чётного байта;

б - передача нечетного байта; с - передача слова

В случае передачи 16-разрядного слова (рис. 3.2,с) /BHENявляется активным (/BHEN=0), а /ADR0 неактивным (ADR0=1).При этом типе передачи четный байт передаётся по /DAT7 - /DAT0, а нечетный - по /DATF- /DAT8.

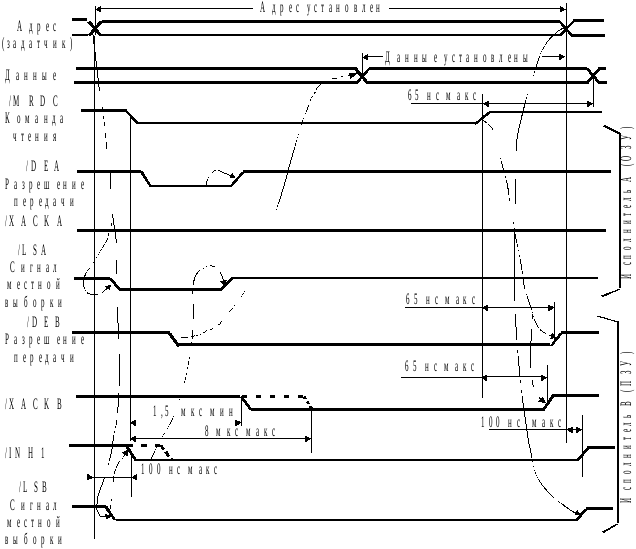

Операция чтения информации. При выполнении операции чтения из памяти (/MRDC) или устройства ввода-вывода (/IORC) команды инициируют один и тот же тип операции, которая выполняется в следующей последовательности (рис. 3.3.):

- задатчик выдает адрес ячейки памяти или устройства ввода-вывода;

- через 50 нс задатчик вырабатывает команду /MRDCили /IORC;

- после появления команды чтения исполнитель (память или устройство ввода-вывода) выставляет информацию на линии данных и выдает сигнал подтверждения передачи /XACK, который указывает, что данные находятся на магистрали;

- задатчик, получив сигнал /XACK, принимает данные и снимает /MRDCили /IORCс магистрали. Адрес исполнителя удерживается не менее 50 нс после снятия команды;

- задатчик, сбросив команду, снимает адрес исполнителя;

- исполнитель в течение 65 нс после снятия команды /MRDCили /IORCдолжен снять /XACKи данные.

Рис. 3.3. Временная диаграмма операции чтения

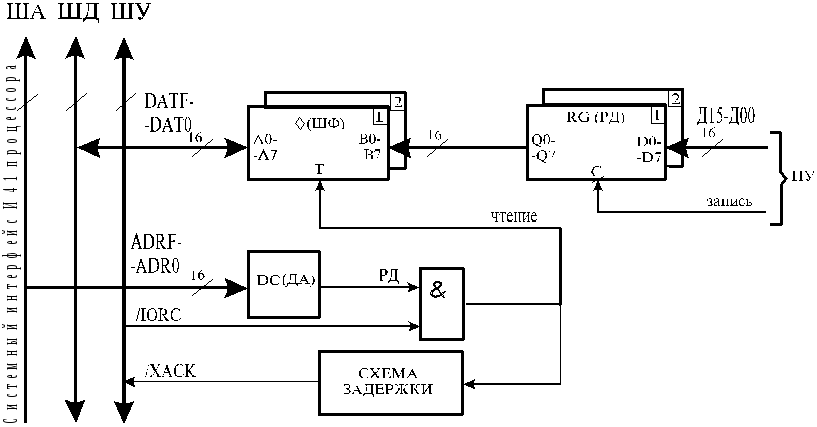

На рис. 3.4 приведен модуль ввода информации с периферийного устройства, который реализует данную операцию. Работа модуля заключается в следующем.

Периферийное устройство устанавливает данные на линиях Д15-Д00 и записывает их в регистр данных РД. Процессор, обращаясь к РД, устанавливает на ША (ADRF-ADR0) его адрес. Адрес поступает на дешифраторы адресов всех устройств системы управления. Устройство, распознавшее адрес, формирует на выходе дешифратора сигнал РД (сигнал обращения к регистру данных), который открывает схему &.

Рис. 3.4. Модуль ввода информации с периферийного устройства

Операция записи информации. При выполнении операции записи в память или устройство ввода/вывода команды /MWTCили /IOWCинициируют один и тот же тип операции (рис. 3.5).

Порядок выполнения операции записи следующий:

-задатчик выдает адрес памяти или устройства ввода-вывода и данные, которые должны быть достоверны за 50 нс до выдачи команды записи;

-задатчик выставляет команду записи /MWTCили /IOWC. Команда говорит о том, что данные установлены;

-исполнитель, получив данные, выдаёт задатчику сигнал подтверждения передачи /XACK, что позволяет задатчику снять с магистрали команду, адрес и данные;

-исполнитель снимает сигнал /XACKв течение 65 нс после снятия команды записи.

Операция записи завершена.

Рис. 3.5. Временная диаграмма операции записи информации

На рис. 3.6 приведена структурная схема модуля, поясняющая реализацию операции вывода данных на периферийное устройство.

Процессор, выполняя данную операцию, устанавливает на линиях связи ADRF-ADR0 адрес устройства, а также передаваемые данные на шинеDATF-DAT0. Адрес поступает на дешифратор адреса ДА, дешифрируется и в виде сигнала выбора РД выдаётся на схему &. Данные проходят через ШФ и поступают на входыD7-D0 РД. Затем процессор выставляет сигнал записи /IOWC, который проходит через открытую схему & и поступает на вход С регистра РД, записывая данные в регистр данных. Данные выдаются на шину периферийного устройства Д15-Д00. Одновременно сигнал с выхода схемы & поступает на схему задержки, с выхода которой выдаётся на линию подтверждения передачи /XACK. Получив сигнал /XACK, процессор сбрасывает /IOWCи снимает адрес и данные. Сброс сигнала /IOWCприводит к снятию /XACK. Вывод данных на периферийное устройство завершён.

Рис. 3.6. Модуль вывода данных на периферийное устройство

Операции запрета. При выполнении операции чтения памяти или записи в память могут использоваться операции запрета. В данных операциях используются сигналы запрета /INH1 и /INH2, вырабатываемые исполнителями. Исполнители, участвующие в операциях запрета, подразделяются на три класса: высшего, среднего и низшего приоритета запрета. При этом исполнитель высшего приоритета является запрещающим для исполнителей среднего и низшего приоритета. Исполнитель среднего приоритета является запрещающим для исполнителя низшего приоритета. Исполнители среднего приоритета в первом случае и низшего во втором случае являются запрещаемыми исполнителями.

На рис. 3.7 приведена временная диаграмма операции запрета. В данном случае модули ПЗУ и ОЗУ имеют одни и те же адреса памяти.

Сигнал запрета, выдаваемый запрещающим исполнителем, образуется путем дешифрации адреса памяти (время задержки запрета tIDне более 100 нс). Запрещающий исполнитель может дешифрировать одиночный адрес, блок адресов или любую комбинацию из них. Когда запрещающий исполнитель распознает адрес во время активной команды /MRDCили /MWTC, он вырабатывает сигнал запрета, который воспринимается исполнителем, подлежащим запрету. Данный исполнитель, приняв такой запрет, делает пассивными все свои формирователи на линиях адреса и может продолжать выполнение внутренних операций.

Сигнал /INH1 выдается (во время присутствия соответствующего адреса) исполнителем среднего приоритета (например, модулем ПЗУ или модулем ввода/вывода, работающем в адресном пространстве памяти), для того чтобы предотвратить работу на магистрали исполнителя низшего приоритета (как, например, модуля ОЗУ). Сигнал /INH2 выдается (во время присутствия соответствующего адреса) исполнителем высшего приоритета, например, модулем вспомогательного ПЗУ или модулем ПЗУ начальной загрузки, для того чтобы предотвратить работу на магистрали исполнителя среднего приоритета. Следовательно, модуль ПЗУ запрещает работу модуля ОЗУ. Исполнитель высшего приоритета также должен выдавать сигнал /INH1, чтобы исполнитель низшего приоритета тоже подлежал запрету. Сигналы запрета должны формироваться усилителями с открытым коллектором.

При активных исполнителях среднего и высшего приоритета сигнал /INH1 формируется усилителями на обоих модулях. Если вырабатываются сигналы запрета, то они должны выдаваться в течение 100 нс после установки адреса.

Рис. 3.7. Временная диаграмма выполнения операции запрета при чтении

В многопроцессорных системах с единой системной магистралью взаимное исключение работы на магистрали (например, чтение или запись информации в память) обеспечивает сигнал занятости /BUSY. Сигнал блокировки /LOCKобеспечивает расширение этого взаимного исключения, например, в многопроцессорных системах с обменом информации между процессорами через многопортовую память (рис. 3.8).

Рис. 3.8. Пример использования сигнала блокировки /LOCK

Сигнал /LOCK(рис. 3.9) должен выдаваться за 100 нс до снятия сигнала чтения или записи и должен оставаться активным не менее 100 нс после снятия сигнала команды в последнем блокированном цикле памяти.

Рис. 3.9. Временная диаграмма операции блокировки /LOCK

Исполнитель блокирует доступ к другим портам своей многопортовой памяти и подключает её к своей системной магистрали, когда он адресован и сигнал блокировки активен. Сигнал блокировки не должен выдаваться непрерывно более 12 мкс. Это обеспечивает задатчику на другой стороне многопортовой памяти доступ к этой памяти через приемлемый отрезок времени. Сигнал занятости /BUSYдолжен быть активен всегда, когда активен сигнал /LOCK.