- •А.Н. Компанейц

- •Введение

- •1. Устройства числового программного управления

- •1.1. Задачи, решаемые учпу

- •Функции учпу

- •Структура учпу

- •Интерфейс магистральный параллельный

- •2.1. Назначение, принцип действия, основные характеристики

- •2.2. Одиночный адресный обмен

- •2.3. Одноуровневая процедура прерывания

- •3. Интерфейс и41

- •3.1. Назначение, принцип действия и характеристика интерфейса

- •3.2. Порядок обмена сообщениями

- •3.3. Операции прерывания

- •3.4. Операции смены задатчика

- •4. Устройство числового программного управления мс2101

- •4.1. Технические данные учпу

- •4.2. Устройство и работа учпу

- •Список литературы

- •Содержание

2.3. Одноуровневая процедура прерывания

При одноуровневой системе прерываний приоритет устройств задаётся аппаратно и определяется его положением на линии "Разрешение прерывания" /ПРР4 относительно других устройств. Приоритет устройства убывает по мере удаления устройства от процессора в направлении распространения сигнала /ПРР4 (рис. 2.10).

Все устройства, которым необходимо прерывать работу процессора, подключаются к линии запроса прерывания /ЗПР4 . Прерывание осуществляется в соответствии с временной диаграммой, представленной на рис. 2.11, в следующей последовательности:

- устройство, готовое прервать процессор, устанавливает сигнал /ЗПР4;

- процессор в каждом рабочем цикле анализирует состояние линии /ЗПР4. При появлении на ней сигнала и после завершения выполнения текущей команды устанавливает сигналы /ДЧТ и /ПРР4. Сигнал /ДЧТ поступает на все устройства, а /ПРР4 последовательно обходит устройства, подключённые к интерфейсу (рис. 2.10). На входе в устройство сигнал /ПРР4 обозначается /ПРРП (приёмник), а на выходе - /ПРРИ (источник);

Рис. 2.10. Схема организации одноуровневого прерывания в МПИ

Рис. 2.11. Временная диаграмма одноуровневой процедуры прерывания

*- безразличное состояние

- ближайшее по линии /ПРР4 устройство, имеющее наивысший приоритет из запросивших, при получении сигнала /ПРРП блокирует его дальнейшее распространение, сбрасывает сигнал /ЗПР4, устанавливает сигнал /ОТВ и адрес вектора прерывания на линиях АД;

- процессор читает адрес вектора прерывания с линий АД, сбрасывает сигналы /ДЧТ и /ПРР4 и приступает к обслуживанию прерывания;

-устройство, запросившее прерывание, снимает адрес вектора прерывания с линий АД и сбрасывает сигнал /ОТВ.

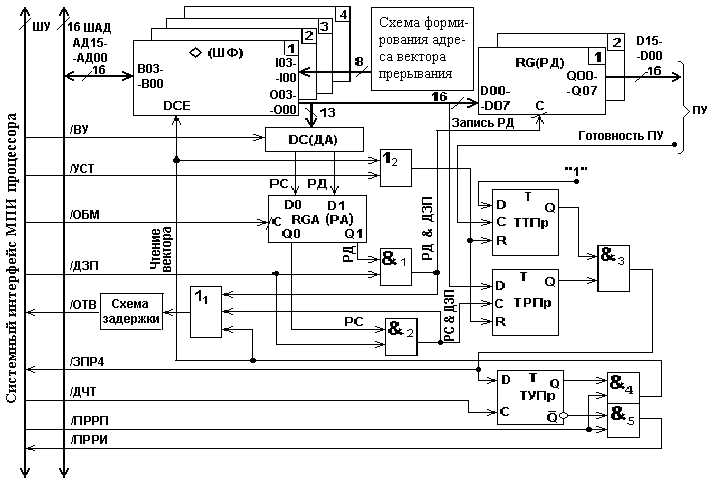

На рис. 2.12 приведена схема модуля, иллюстрирующего организацию одноуровневого прерывания. Модуль предназначен для вывода информации на периферийное устройство по его готовности. В модуле имеется два адресуемых регистра:регистр данных (РД) и регистр состояния (РС). В состав регистра состояния входят триггер требования прерывания (ТТПр), триггер разрешения прерывания (ТРПр), триггер управления прерыванием (ТУПр). Триггер ТРПр предназначен для программного управления прерыванием. Если триггер ТРПр не установлен, то запрос прерывания от периферийного устройства через схему &3 не пройдёт. Прерывание от данного устройства запрещено.

Работу модуля поясним тремя процедурами: процедурой установки триггера ТРПр, процедурой прерывания, процедурой обслуживания прерывания. Процессор при начальной инициализации системы устанавливает сигнал /УСТ, который сбрасывает в данном модуле триггеры ТТПр и ТРПр.

Рис. 2.12. Модуль вывода информации на ПУ в режиме прерывания программы

Установка триггера ТРПр осуществляется командой вывода по отношению к регистру состояния в соответствии с процедурой "запись" в следующей последовательности:

- процессор на линиях АД12-АД00 выставляет адрес регистра состояния и сигнал /ВУ. Адрес, прошедший через шинный формирователь ШФ, и сигнал /ВУ поступают на дешифратор адреса ДА. На выходе дешифратора формируются сигналы РС=1 и РД=0;

- процессор устанавливает сигнал /ОБМ, которым состояние сигналов РС и РД записывается в регистр РА. Сигнал РС=1 с выхода Q0 регистра адреса открывает схему &2;

- процессор на линии АД06 устанавливает активный уровень, который через ШФ поступает на вход Dтриггера ТРПр (линия АД06 взята в качестве примера, т.к. в стандарте не определена);

- процессор устанавливает сигнал /ДЗП. Он проходит через схему &2на вход С триггера ТРПр и устанавливает его. Одновременно сигнал с выхода схемы &2 проходит через схему ИЛИ (11), схему задержки и поступает на линию /ОТВ;

- процессор сбрасывает сигналы /ДЗП и АД06. Снимается сигнал /ОТВ;

- процессор, завершая процедуру установки триггера ТРПр, сбрасывает /ОБМ. Сигнал с выхода Qтриггера ТРПр открывает схему &3. Прерывание разрешено.

Периферийное устройство, готовое принимать данные, формирует сигнал, который, поступая на вход С триггера ТТПр, устанавливает его. Сигнал с выхода Qтриггера ТТПр проходит через схему &3и поступает на входDтриггера ТУПр и на линию /ЗПР4, запрашивая прерывание.

Процессор, получив /ЗПР4, реализует процедуру прерывания в соответствии с временной диаграммой рис. 2.11 для определения устройства запросившего прерывание. Результатом выполнения данной процедуры является чтение адреса вектора прерывания из схемы формирования.

Выполняется процедура в следующей последовательности:

- процессор выставляет сигнал /ДЧТ, который поступает на вход Cтриггера ТУПр, и устанавливает его. Сигнал с выходаQтриггера открывает схему &4, а с выхода /Qзакрывает схему &5;

- процессор формирует сигнал /ПРР4. Сигнал последовательно обходит устройства, подключённые к интерфейсу. В устройстве, не запрашивавшем прерывание, сигнал /ПРРП проходит через схему &5и поступает на линию /ПРРИ, т.к. триггер ТУПР не установлен. В устройстве, запросившем прерывание, сигнал /ПРРП проходит через схемы &4, ИЛИ (11), задержки и поступает на линию /ОТВ. Одновременно сигнал с выхода схемы &4поступает на входDCEшинных формирователей, а также проходит через схему ИЛИ (12), сбрасывая триггеры ТТПр и ТРПр (снимается сигнал /ЗПР4). ШФ сигналом на входеDCEпереключаются на ввод. Адрес вектора прерывания со схемы формирования проходит через ШФ и поступает на линии АД07-АД00;

- процессор читает адрес вектора прерывания, сбрасывает сигналы /ДЧТ и /ПРР4. Соответственно снимается сигнал /ОТВ и шинные формирователи переводятся в исходное состояние. Адрес вектора прерывания снимается с линий АД07-АД00. Триггер ТУПр будет сброшен при следующей установке сигнала /ДЧТ.

Процессор, получив адрес вектора прерывания, обслуживает устройство, запросившее прерывание. Подпрограмма обслуживания прерывания в данном примере предусматривает вывод информации в регистр данных РД. Вывод осуществляется аналогично рассмотренной выше процедуре "запись". Завершив обслуживание устройства, процессор возвращается к выполнению прерванной программы.