- •А.Н. Компанейц

- •Введение

- •1. Устройства числового программного управления

- •1.1. Задачи, решаемые учпу

- •Функции учпу

- •Структура учпу

- •Интерфейс магистральный параллельный

- •2.1. Назначение, принцип действия, основные характеристики

- •2.2. Одиночный адресный обмен

- •2.3. Одноуровневая процедура прерывания

- •3. Интерфейс и41

- •3.1. Назначение, принцип действия и характеристика интерфейса

- •3.2. Порядок обмена сообщениями

- •3.3. Операции прерывания

- •3.4. Операции смены задатчика

- •4. Устройство числового программного управления мс2101

- •4.1. Технические данные учпу

- •4.2. Устройство и работа учпу

- •Список литературы

- •Содержание

4.2. Устройство и работа учпу

В состав УЧПУ входят блоки дисплейно-пультовый (микроЭВМ "Электроника 12401.3") и управляющий (микроЭВМ "Электроника НМС 12402.2").

МикроЭВМ "Электроника НМС 12401.3" является основной микроЭВМ и осуществляет координацию работы всех составных частей УЧПУ. Структурная схема микроЭВМ приведена на рис. 4.1.

В состав микроЭВМ "Электроника НМС 12401.3" входят: вычислитель (ВЧС), универсальный контроллер, контроллер кассеты и кассета ЦМД, видеомонитор и пульт управления.

ВЧС является основным процессорным модулем и входит также в состав микроЭВМ "Электроника НМС 12402.2".

Вычислитель предназначен для выполнения программ функционального, тестового и другого математического обеспечения. ВЧС осуществляет приём, обработку, хранение и выдачу информации на другие устройства УЧПУ. В состав вычислителя входят: модуль процессорный, ПЗУ, ОЗУ и модуль телеграфных каналов (МТК) обмена информацией. Процессор выполнен на основе БИС К1801ВМ1Г.

Модуль телеграфных каналов предназначен для организации обмена по трём телеграфным каналам и выполнен на БИС КР1801ВП1-065. БИС является контроллером внешних устройств, работающих на линию связи с последовательной передачей информации в дуплексном режиме, и предназначена для преобразования параллельной информации в последовательную и наоборот. Модуль позволяет объединять микроЭВМ в различные распределённые микропроцессорные структуры типа кольцо, радиальная, радиально-кольцевая и т.д.

Универсальный контроллер выполнен как многоканальный интерфейс радиальный параллельный модернизированный (ИРПМ) и предназначен для программного управления видеомонитором, пультом управления (клавиатурой), фотосчитывающим устройством (ФСУ), перфоратором ленточным (ПЛ).

Контроллер кассеты содержит в своём составе энергонезависимое запоминающее устройство на основе цилиндрических магнитных доменов (ЦМД) ёмкостью 32Кбайта (18 Кбайт доступно потребителю) и контроллер дополнительной кассеты энергонезависимой памяти (кассета ЦМД) ёмкостью 32 Кбайта. Кассета ЦМД, подключаемая к контроллеру кассеты, используется для долговременного хранения библиотеки управляющих программ.

Рис. 4.1. Структура микроЭВМ "Электроника НМС 12401.3"

МикроЭВМ "Электроника НМС 12402.2" является исполнительной и осуществляет управление приводами и цикловой автоматикой станка. Структурная схема микроЭВМ приведена на рис. 4.2.

В состав данной микроЭВМ входят: вычислитель, который аналогичен ВЧС микроЭВМ "Электроника 12401.3", модуль управления приводами и два модуля цикловой автоматики.

Модуль управления приводами предназначен для формирования и выдачи сигналов управления следящими приводами координатных перемещений и приводом главного движения (БУП), а также приёма сигналов с фотоэлектрических импульсных датчиков (ИП): преобразователей координатных перемещений, датчика скорости вращения шпинделя, датчика оперативного управления.

Рис. 4.2. Структура управляющей микроЭВМ "Электроника НМС 12401.2"

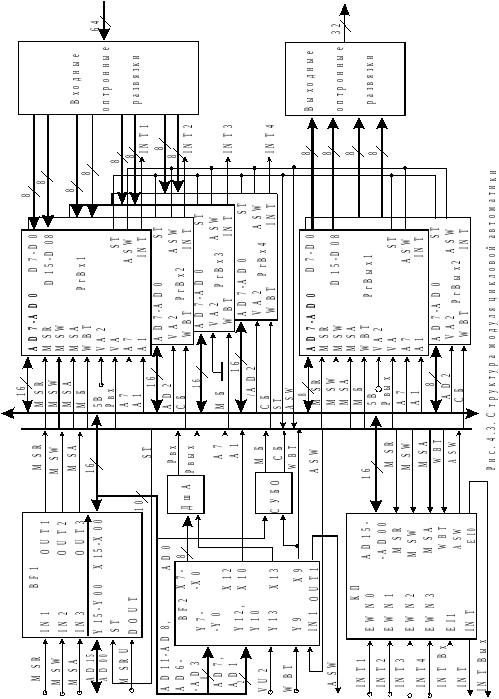

Модуль цикловой автоматики предназначен для формирования сигналов ТК управления электроавтоматикой (32 выхода) и приёма сигналов состояния электроавтоматики управляемого оборудования (64 входа). Структурная схема модуля приведена на рис. 4.3.

В состав модуля входят следующие блоки: буферы BF, дешифратор адреса регистров ДшА, схема управления байтовым обменом СУБО, контроллер прерываний КП, четыре входных регистра РгВх1-РгВх4, входные оптронные развязки, два выходных регистра и выходные оптронные развязки.

Буферы BF- это двунаправленные приемопередатчики.

Предназначены для развязки системной

магистрали УЧПУ от внутренних схем

модуля. В составBFвходят

три неуправляемых однонаправленных

каналаIN1,IN2,IN3. Направление передачи

данных черезBFпо входамY![]() Xопределяется сигналами

на входахSTиDOUT.

ПриST=DOUT="0"

направлениеX(15-00)

Xопределяется сигналами

на входахSTиDOUT.

ПриST=DOUT="0"

направлениеX(15-00)![]() Y(15-00), а при всех остальных

комбинациях -Y(15-00)

Y(15-00), а при всех остальных

комбинациях -Y(15-00)

![]() X(15-00).BF2

включен постоянно в направленииY

X(15-00).BF2

включен постоянно в направленииY![]() X.

X.

ДшА выполнен на цифровых компараторах и предназначен для выбора группы входных или выходных регистров при обращении к ним процессора.

СУБО выполнена на логических элементах и в зависимости от состояния сигналов WBTиA0 формирует сигналы "младший байт" (МБ) либо "старший байт" (СБ). Состояние этих сигналов сохраняется в триггере до окончания текущего цикла обмена.

Контроллер прерываний (БИС КР1801ВП1-031) предназначен для формирования сигнала INT("Запрос на прерывание") при поступлении запросов на прерывание по линиям состояния электроавтоматики (D0,D1,D8 иD9 каждого входного регистра), а также для выдачи соответствующего адреса вектора прерывания по сигналу чтение ("MSR"). Последовательность выполнения операции прерывания в УЧПУ аналогична прерыванию в интерфейсе МПИ (раздел 2).

Выходные регистры (БИС КР1801ВП1-16) предназначены для приёма информации от процессора в соответствии с процедурой вывода данных, хранения полученной информации и передачи её через выходные оптронные развязки на электроавтоматику оборудования.

Входные регистры (БИС КР1801ВП1-16) предназначены для приёма информации по линиям состояния электроавтоматики и формирования запросов на прерывание по соответствующим входам, если они разрешены. Разрешение на прерывание осуществляется записью "1" в соответствующие разряды регистра управления (РУ) входного регистра.

Выходные оптронные развязки выполняют гальваническую развязку цепей УЧПУ и управляемого оборудования, а также преобразуют и усиливают сигналы управления до напряжения 24 В с допустимым током до 200 мА.

Таблица

4.1

Сигналы интерфейса

УЧПУ МС2101.05-02

Сигналы интерфейса

МПИ

/MSR

/ДЧТ

/MSW

/ДЗП

/MSA

/ОБМ

/VU

/ВУ

/ASW

/ОТВ

/WBT

/ПЗП

/INT

/ЗПР4

/INTвх

/ПРР4

Обмен информацией процессора с модулями осуществляется в соответствии с протоколами, функционально совместимыми с протоколами интерфейсов "Общая шина" и "Электроника 60". Дальнейшим развитием этих интерфейсов является интерфейс МПИ, описание которого приведено в разделе 2. Соответствие сигналов интерфейса МПИ и сигналов, используемых в УЧПУ, приведено в табл. 4.1.

Рассмотрим работу модуля цикловой автоматики.

При включении питания либо в процессе работы процессор формирует сигнал /CLR, устанавливающий все регистры в исходное состояние. При этом на выходах модуля устанавливается высокий уровень напряжения +24В.

Вывод данных может осуществляться в байтовом формате либо словами. При выводе информации словами младший байт слова записывается в регистр информации РИ1 (разряды D7-D0 ) РгВх1, а старший байт в РИ1 (D7-D0) РгВх2. Младший байт следующего слова в РИ2 (разрядыD15-D08) РгВх1, а старший байт в РИ2 (D15-D08) РгВх2. При выводе данных байтами управление обменом осуществляется СУБО, на выходе которой формируются сигналы "Старший байт" (СБ=1) или "Младший байт" (МБ=1). Передача слов сопровождается сигналами СБ=1 и МБ=1.

Вывод информации осуществляется в следующей последовательности. Процессор выставляет адрес, который проходит через буфер BF1 и поступает на буферBF2. Сюда же поступает сигналVU2. Разряды адресаAD11-AD8,AD6-AD3 иVU2 проходят на дешифратор адреса, где сравниваются с уставками. При совпадении кода этих разрядов с уставками выходных регистров на выходе ДшА формируется сигнал Рвых, который поступает на входыVAрегистров РгВых1 и РгВых2 и выбирает их. Разряд А1 определяет выбор регистров РИ1 или РИ2 (D7-D0 илиD15-D8) выходных регистров, а разряд А7 определяет обращение к регистрам РИ либо к регистрам управления РУ БИС. Обращение к регистрам воспринимается приVA=1 иVA2=1. Таким образом, РгВх1 всегда выбирается при наличии сигнала Рвых, РгВых2 только при Рвых=1 иAD2=1. Данное состояние сигналов соответствует формированию сигналаST=0. С задержкой, необходимой для дешифрации адреса, процессор выставляет сигнал /MSA, который проходит черезBF1 на входыMSAвыходных регистров и записывает обращение в них. Затем адрес и сигнал /VU2 снимаются и выставляются данные, которые проходят черезBF1 на входы выходных регистров. Процессор выдаёт сигнал /MSW, который проходит черезBF1, записывает данные в выбранные регистры. Информация, записанная в регистры, преобразуется оптронными развязками в сигналы управления электроавтоматикой оборудования. Процессор, завершая процедуру вывода, снимает /MSW, данные и /MSA.

Обращение к входным регистрам при вводе данных осуществляется в той же последовательности что и при выводе данных. Выбранный регистр на выходе формирует сигнал ST=0, который поступает на входSTбуфераBF1. После записи адреса процессор выставляет сигналы /MSRUи /MSR/. СигналыST=0 и /MSRUпереключают буфер на ввод данных в процессор. Сигнал /MSRпроходит черезBF1 на соответствующие входы РгВх1-РгВх4. Данные из выбранных регистров поступают на шину АД. Вводимые данные сгруппированы в слова и передаются на линииAD15-AD00 в соответствии с таблицей 4.2.

Последовательность чтения слов из регистров определяется программой. Снятие сигнала MSRиMSAзавершает цикл ввода данных. Введённая информация о состоянии устройств электроавтоматики анализируется процессором. В соответствии с проведённым анализом и выполняемой управляющей программой принимаются необходимые решения по выполнению задач технологического процесса.

Таблица 4.2

|

Регистры, читаемые за один цикл обмена |

Разряды регистров, передаваемые на AD15-AD08 процессора в данном цикле |

Разряды регистров, передаваемые на AD07-AD00 процессора в данном цикле |

|

РгВх1 РгВх2 |

- D7 -D0 |

D7 -D0 - |

|

РгВх1 РгВх2 |

- D15 -D08 |

D15 -D08 - |

|

РгВх3 РгВх4 |

- D7 -D0 |

D7 -D0 - |

|

РгВх3 РгВх4 |

- D15 -D08 |

D15 -D08 - |