- •Этапы развития микропроцессорной техники.

- •Классификация микропроцессоров.

- •Виды обменов в микроЭвм.

- •Обмен по прямому доступу в память.

- •Обмен по прерыванию.

- •Микропроцессор 580вм80.

- •Intr – вход запроса прерывания.

- •Inta – сигнал подтверждения обработки прерывания. Он говорит о том, что микропроцессор начал обрабатывать прерывание. Обработки прерывания начинается на границе между двумя командами.

- •Синхронизация работы микропроцессора. Микросхема 580гф24.

- •Типы машинных циклов микропроцессора 580вм80. Микросхема 58вк28/38.

- •Построение разрядно-модульных микропроцессоров.

- •Микропроцессорная секция 1804вс1.

- •Микропроцессорный комплект бис 1815 для конвейерных систем цос.

- •Универсальный процессорный элемент 1815вф1.

- •Сумматор последовательных числе 1815им1.

- •Бис ортогональной регистровой памяти 1815ир1.

- •Цифровая фильтрация на микропроцессорном комплекте 1815.

- •Микропроцессор 1815 вф3.

- •Особенности реализации систем цос на бис 1815вф3.

- •Микропроцессор 1810вм86/88.

- •Inta – сигнал подтверждения прерывания.

- •Модель процессора 1810вм86 для программистов.

- •Программный счётчик и регистр флагов. Флаги, входящие в младший байт повторяют флаги 580-ого процессора.

- •Сопроцессор 1810вм87.

- •Системный контроллер 1810вг88.

- •Включение процессора 1810вм86 в максимальном режиме.

- •Арбитр шин 1810вб89.

- •Организация приоритетного арбитража.

- •2.На системной магистрали располагается память, на резидентной магистрали только увв.

- •Программируемый контроллер прерываний 1810вн59.

- •Контроллер пдп 1810вт37.

- •Процессоры 2, 3 и 4 – ого поколения.

- •Процессор 80386.

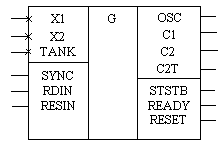

Синхронизация работы микропроцессора. Микросхема 580гф24.

Процессор выполняет программу, состоящею из отдельных команд. Во время выполнения команды происходит извлечение кода команды из памяти ЭВМ, дешифрация команды, подготовка данных для выполнения команды, выполнение команды и запись результата. Очевидно, что все эти действия должны выполняться в строгой последовательности. Для выполнения последовательности действий микропроцессору необходимо наличие тактовых сигналов, которые синхронизируют работу отдельных блоков.

Код команды и данные располагаются в памяти. Для извлечения их оттуда необходимо произвести обмен по магистрали. Обмен также необходим и при записи результата.

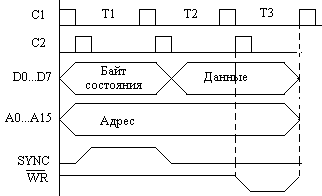

Машинный цикл – это время в течении которого происходит извлечение или запись одного байта информации из памяти и выполнение команды, если команда однобайтная. Для выполнения одной команды необходимо от одного до пяти машинных циклов. В течении одного машинного цикла происходит выдача процессором адреса ячейки памяти с которой он хочет обменяться, байта состояния, далее производится обмен данными и дешифрация кода команды, если читается код команды. Это множество действий требует машинных тактов.

Микропроцессор требует 2 сдвинутые во времени последовательности синхросигналов С1 и С2. На формирование этих последовательностей сигналов накладываются строгие ограничения. Первоначально тактовые сигналы формировались с использованием «россыпи» (логических микросхем и триггеров). Позднее была создана специальная микросхема, формирующая тактовые сигналы. Она генерирует одну из возможных последовательностей синхросигналов.

Схема формирования синхросигналов занимала не очень много места в микросхеме, поэтому на микросхему были возложены ещё 3 функции:

Выработка синхросигнала для считывания байта состояния.

Схема привязки сигнала готовности к тактовой последовательности микропроцессора.

Формирование сигнала начального сброса.

х – означает, что сигнал не 0 или 1, а другой

формы (не логической).

– означает, что сигнал не 0 или 1, а другой

формы (не логической).

Х1, Х2 – входы для подключения кварца.

TANK – сигнал для подключения внешнего колебательного контура, если кварц работает не на основной гармонике (задача подавить первую гармонику и выделить например третью).

OSC – выход генератора (частота F на диаграмме). Эта частота в 9 раз выше чем С1 и С2.

C1, C2 – тактовые сигналы, поступающие на микропроцессор с уровнем +12В. Все остальные имеют уровень ТТЛ.

C2T – сигнал С2, только уровня ТТЛ. Этот сигнал поступает на магистраль и бывает нужен некоторым устройствам.

SYNC – сигнал синхронизации адреса, который (сигнал) поступает от микропроцессора.

STSTB – синхросигнал байта состояния.

RDIN – сигнал готовности, поступающий от внешних устройств.

READY – это тот же сигнал, но привязанный к тактовой сетке.

RESIN – аналоговый сигнал начального сброса.

RESET – цифровой сигнал начального сброса привязанный к тактовой частоте.

Типы машинных циклов микропроцессора 580вм80. Микросхема 58вк28/38.

При обмене по магистрали микропроцессор использует 10 различных типов машинных циклов:

Извлечение кода команды – цикл М1.

Чтение данных из памяти.

Запись данных в память.

Чтение данных из стека.

Запись данных в стек.

Чтение данных из устройства ввода вывода.

Запись данных в устройство ввода вывода.

Цикл обслуживания прерывания.

Цикл останова.

Цикл обслуживания прерывания в останове.

Для того, чтобы устройства, взаимодействующие с микропроцессором знали какую операцию выполняет микропроцессор в данном машинном цикле в начале каждого машинного цикла микропроцессор формирует байт состояния. Байт состояния выдаётся по шине данных. Байт состояния имеет следующее назначение разрядов:

Д0 – обслуживание сигнала запроса прерывания.

Д1- направление передачи информации (от/в микропроцессор).

Д2 – обмен со стеком.

Д3 – обслуживание останова.

Д4 – обмен с портом ввода вывода.

Д5 – цикл М1.

Д6 – ввод или вывод из внешнего устройства.

Д7- обмен с памятью.

Для того, чтобы разряды байта состояния использовались для управления работой других устройств, их необходимо зафиксировать и сформировать из них управляющие сигналы. Первоначально это делалось с помощью простых логических схем. В последствии появилась микросхема 580ВК28/38. Попутно с этой функцией микросхема 580ВК28/38 выполняет умощнение сигналов шины данных.

Д 0…Д7

– магистраль данных, поступает от

микропроцессора.

0…Д7

– магистраль данных, поступает от

микропроцессора.

ДВ0…ДВ7 – умощнённая магистраль данных.

STSTB – синхросигнал считывания байта состояния, идёт с микросхемы 580ГФ24.

DBIN – синхросигнал чтения данных, поступает от микропроцессора, управляет направлением передачи.

WR – синхросигнал записи, идёт от микропроцессора, управляет направлением передачи, но в обратную сторону (в отличии от DBIN): данные с шины Д идут в ДВ.

HLDA – сигнал подтверждения ПДП, идёт от микропроцессора. В данной микросхеме он переводит выходы в третье состояние.

BUSEN – отключает выходную шину данных (вспомогательный сигнал).

MEMR – синхросигнал чтения их памяти.

MEMW – синхросигнал записи в память.

I/OR - синхросигнал чтения из устройства ввода вывода.

I/OW – синхросигнал записи в устройство ввода вывода.

INTA - сигнал подтверждения прерывания.

Обмен микропроцессора 580ВМ80 по магистрали.

Цикл М1.

В первом такте по адресной шине выдаётся адрес ячейки памяти в которой хранится код команды, по шине данных выдаётся байт состояния. Выдача этих сигналов синхронизируется сигналом SYNC.

Во втором такте инициируется процессором чтение данных. Для этого формируется сигнал DBIN. Происходит проверка сигнала READY. Если процессор взаимодействует с медленным устройством, то сигнал READY отсутствует и процессор вставляет во временную диаграмму один или несколько тактов ожидания до появления сигнала READY (он проверяется только в начале такта). При выполнении тактов ожидания процессор формирует сигнал WAIT. В такте Т3 по заднему фронту DBIN процессор считывает код команды пришедший по шине Д0…Д7.

Последующие 1,2 или 3 такта процессор дешифрирует команду и выполняет её, если у него есть все необходимые данные.

Цикл чтения данных из ОЗУ или УВВ.

В первом такте выдаётся адрес и байт состояния, во втором такте инициируется чтение сигналом DBIN, в третьем такте процессор считывает данные по заднему фронту сигнала DBIN. Байт состояния указывает откуда будет считываться информация.

Циклы записи в память и записи в УВВ.

В первом такте читается байт состояния, во втором такте процессор выставляет данные, в третьем такте выдаётся сигнал записи WR.

Цикл прерывания.

Весь обмен состоит из 3-х или 5 циклов. В первом цикле процессор вырабатывает сигнал INTA. В ответ на это устройство снимает сигнал INTR. В первом такте выдаётся байт состояния или адрес, а далее на шине Д0…Д7 то устройство, которое вызвало прерывание формирует код команды RST или код команды CALL. При коде команды CALL процессор формирует ещё 2 цикла чтения в которых устройство вызвавшее прерывание передаёт в процессор адрес подпрограммы обработки прерывания. На рисунке эти 2 цикла не показаны. В следующих 2-х циклах происходит запись в стек содержимого счётчика команд. процессор уменьшает на 1 содержимое указателя стека и выдаёт это значение по шине адреса. По шине данных в стек выдаётся старший байт счётчика команд. В следующем цикле содержимое указателя стека уменьшается ещё раз на 1. А в качестве данных выдаётся младший байт счётчика команд. После этого в счётчик команд заносится новое значение и начинается программа обработки прерывания.

Организация микропроцессорной системы на основе микропроцессора 580ВМ80.

Микропроцессор 1821ВМ85А. Отличия от микропроцессора 580ВМ80.

Данный микропроцессор является приемником микропроцессора 580ВМ80, поэтому в нём сохранены основные черты предшественника:

Разрядность шины адреса и данных.

Система команд.

Вместе с тем дальнейшее развитие технологии позволило повысить степень интеграции микросхем. Поэтому процессор серии 1821 полностью помещается в одной микросхеме. Кроме самого процессора в микросхеме разместились: схема задающего генератора, схема контроллера прерываний, системный контроллер и несколько более простых схем. Это позволяет на 3-х микросхемах создать работоспособную микроЭВМ с процессором, ОЗУ, ПЗУ и портами ввода вывода. Микропроцессор выполнен по КМОП технологии, но сигналы совместимы с ТТЛ уровнем. В схеме одно напряжение питания +5В.

X 1,X1

– входы для подключения кварца.

1,X1

– входы для подключения кварца.

TRAP – немаскируемые прерывания в наивысшим приоритетом.

RST 7.5 – маскируемые прерывания.

RST 6.5 – маскируемые прерывания.

RST 5.5 – маскируемые прерывания.

Приоритет также понижается.

INTR – немаскируемые прерывания самого низкого уровня.

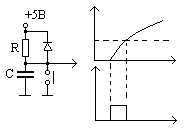

RESIN – вход начального сброса (аналоговый). Схема с резистором и конденсатором.

READY – сигнал готовности, поступает от медленно действующих устройств.

HOLD – сигнал запроса режима ПДП.

AD0…AD7 – совмещённая шина адреса и данных.

A7…A15 – шина адреса.

ALE – синхросигнал передачи адреса или синхросигнал начала цикла.

WR – синхросигнал записи данных.

RD – синхросигнал чтения данных.

IO/M – данный сигнал показывает с каким устройством ведётся обмен (или с УВВ(0) или с памятью(1) ).

CLK – сигнал тактовой частоты.

RESET – выходной сигнал начального сброса.

INTA – сигнал подтверждения прерывания.

HLDA – сигнал подтверждения режима ПДП.

S0,S1 – сигналы состояния микропроцессора. Они показывают какую операцию выполняет микропроцессор в данном цикле.

SID - последовательный вход данных. По этому входу можно в последовательном коде вводить в микропроцессор информацию.

SOD – выходной последовательный сигнал. В последовательном коде можно выводить данные. Управление этим выходом осуществляется программно.

Максимальная тактовая частота в этом микропроцессоре повышена до 3МГц (в микропроцессоре 580ВМ80 она была 2МГц).

По сравнению с микропроцессором 580ВМ80 можно отметить следующие отличия:

Тактовый генератор помещён внутрь микропроцессора.

Схема начального сброса помещена также внутрь микропроцессора.

Вместо nМОП технологии использована КМОП (малое потребление, но при большой частоте потребление увеличивается и может обогнать ТТЛ).

Один источник питания.

Появилась развитая система прерываний.

Появились две новые команды SIM и RIM для работы в прерываниями.

Появились выводы последовательного ввода и последовательного вывода.

Совмещены шины адреса и данных. За счёт этого освободились 8 выводов.

состояние процессора определяется по сигналам S0 и S1 вместо байта состояния. Эти сигналы находятся на шине в течении всего цикла.

В регистре флагов признак С заменён на 3: С – признак переноса, V – признак переполнения, XS – признак потери значимости.

Циклы обмена.

Цикл М1 или цикл считывания кода команды.

В первом такте осуществляется выдача адреса и она сопровождается синхросигналом ALE. Во втором такте выдаётся сигнал RD и проверяется готовность устройство (READY). При отсутствии сигнала READY вставляется такт ожидания. В третьем такте происходит считывание кода команды или данных. Последующие один или два такта используются для дешифрации команды и её выполнения, если это возможно.

Цикл чтения.

Тот же цикл М1, только требует 3 такта.

Цикла записи.

Ц икл

записи отличается только одним: вместо

RD

используется WR.

Куда производится запись (чтение) в УВВ

или в память определяется сигналом

IO/M.

Данный сигнал висит на шине в течении

всего цикла обмена.

икл

записи отличается только одним: вместо

RD

используется WR.

Куда производится запись (чтение) в УВВ

или в память определяется сигналом

IO/M.

Данный сигнал висит на шине в течении

всего цикла обмена.

В данной серии есть также микросхема ПЗУ - 1821РУ55 и микросхема ОЗУ – 1821РФ10. На этих трёх микросхемах можно построить работающую машину.

Обработка прерываний микропроцессором 1821ВМ85А. Команды SIM и RIM.

TRAP – это немаскируемые прерывания наивысшего приоритета. Активный уровень – высокий. Это значит, что по 1 процессор будет обрабатывать сигнал. От данного прерывания замаскироваться не возможно, поэтому данный вход обычно используется для обработки фатальных ситуаций. Пример: выключение питания. Подпрограмма обработки прерываний располагается по строго определённому адресу – 24h.

RST 7.5 – маскируемые прерывания более низкого уровня. Прерывание обрабатывается и по фронту и по высокому уровню. При появлении переднего фронта сигнала RST 7.5 он фиксируется во внутреннем триггере микропроцессора, поэтому сигнал RST 7.5 будет обрабатываться микропроцессом даже если входной сигнал уже снят.

RST 6.5 – маскируемые прерывания ещё более низкого уровня по сравнению с RST 7.5. Обрабатываются по высокому уровню.

RST 5.5 - маскируемые прерывания ещё более низкого уровня по сравнению с RST 6.5.

Для всех этих прерываний программы обработки располагаются в строго определённом месте.

RST |

0 |

0000 |

|

1 |

0008 |

|

2 |

0010 |

|

3 |

0018 |

|

4 |

0020 |

|

5 |

0028 |

|

6 |

0030 |

|

7 |

0038 |

0024 |

TRAP |

0034 |

RST 6.5 |

002С |

RST 5.5 |

003С |

RST 7.5 |

Наряду с командами EI и DI, которые разрешают или запрещают сразу все маскируемые прерывания в данном микропроцессоре появляются две новых команды SIM и RIM, которые управляют каждым из маскируемых прерываний по отдельности. Кроме этого данные команды управляют последовательным вводом и выводом.

Перед выполнение команды SIM в А должна быть записана следующая информация:

![]()

0,1,2 – Маски прерываний RST 5.5, RST 6.5, RST 7.5.

3 – Разрешение установки масок.

4 – Сброс триггера RST 7.5

5 – Не используется

6 – Разрешение SOD.

7 – SOD (микропроцессора).

После выполнения команды RIM А содержит следующую информацию:

0,1,2 – Маски.

3 – EI/DI

4,5,6 - Состояния входов RST 5.5, RST 6.5, RST 7.5.

7 – SID – показывает что было на выводе SID микропроцессора.