- •Этапы развития микропроцессорной техники.

- •Классификация микропроцессоров.

- •Виды обменов в микроЭвм.

- •Обмен по прямому доступу в память.

- •Обмен по прерыванию.

- •Микропроцессор 580вм80.

- •Intr – вход запроса прерывания.

- •Inta – сигнал подтверждения обработки прерывания. Он говорит о том, что микропроцессор начал обрабатывать прерывание. Обработки прерывания начинается на границе между двумя командами.

- •Синхронизация работы микропроцессора. Микросхема 580гф24.

- •Типы машинных циклов микропроцессора 580вм80. Микросхема 58вк28/38.

- •Построение разрядно-модульных микропроцессоров.

- •Микропроцессорная секция 1804вс1.

- •Микропроцессорный комплект бис 1815 для конвейерных систем цос.

- •Универсальный процессорный элемент 1815вф1.

- •Сумматор последовательных числе 1815им1.

- •Бис ортогональной регистровой памяти 1815ир1.

- •Цифровая фильтрация на микропроцессорном комплекте 1815.

- •Микропроцессор 1815 вф3.

- •Особенности реализации систем цос на бис 1815вф3.

- •Микропроцессор 1810вм86/88.

- •Inta – сигнал подтверждения прерывания.

- •Модель процессора 1810вм86 для программистов.

- •Программный счётчик и регистр флагов. Флаги, входящие в младший байт повторяют флаги 580-ого процессора.

- •Сопроцессор 1810вм87.

- •Системный контроллер 1810вг88.

- •Включение процессора 1810вм86 в максимальном режиме.

- •Арбитр шин 1810вб89.

- •Организация приоритетного арбитража.

- •2.На системной магистрали располагается память, на резидентной магистрали только увв.

- •Программируемый контроллер прерываний 1810вн59.

- •Контроллер пдп 1810вт37.

- •Процессоры 2, 3 и 4 – ого поколения.

- •Процессор 80386.

2.На системной магистрали располагается память, на резидентной магистрали только увв.

Чёткое разделение памяти и УВВ по разным магистралям позволяет использовать один системный контроллер ВГ88 для 2-х магистралей. При этом сигналы управления, управляющие обменом с памятью поступают на системную магистраль, а сигналы управления, управляющие обменом с УВВ поступают на резидентную магистраль. Схема будет выглядеть следующим образом:

Сигналы MRDC и MWTC (чтение/запись в память) поступают на системную магистраль, а сигналы IORC и IOWC поступают на резидентную магистраль. На каждой магистрали располагаются регистры ИП82 для выдачи адреса и усилители ВА86 для обмена данными. Однако управление этими схемами происходит по разному. Схемам на системной магистрали разрешается работа при появлении сигнала AEN. Схемам на резидентной магистрали работа разрешена всегда. С обоих магистралей приходят сигналы готовности RDY1, RDY2. Сигналу с резидентной магистрали всегда разрешается прохождение на процессор. Сигнал AEN1=0. Сигнал RDY2 может пройти на процессор только при активном сигнале AEN. Это связано с тем, что данный сигнал готовности на системной магистрали может быть сформирован для другого процессора, а принят нашим процессором.

3.На обоих магистралях и системной и резидентной располагаются и память и УВВ. Поэтому для каждой магистрали необходим свой системный контроллер. Процессор обращается к памяти и УВВ по адресам. При этом он понятия не имеет на какой магистрали они расположены. Чтобы определить на какой магистрали располагается память или УВВ в схему вводится дешифратор адреса. При этом часть адресов принадлежит системной магистрали, а часть резидентной магистрали.

В данной схеме используется дополнительный сигнал SYSB/RESB, который включает арбитр шин в момент, когда нужен обмен по системной магистрали.

4.Наличие в схеме резидентной шины памяти и резидентной шины ввода вывода требует интерфейсных схем для каждой из этих шин. Однако заметных преимуществ в быстродействии данная схема не даёт.

Программируемый контроллер прерываний 1810вн59.

Микросхема предназначена для реализации системы прерываний в сложных микропроцессорных системах при наличии приоритетов прерываний с несколькими уровнями. Микросхема может работать с микропроцессорами серии 1810, 580 и 1821.

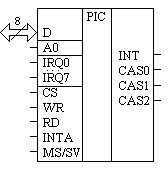

D – шина данных.

– шина данных.

A0 – адресный разряд.

IRQ0…IRQ7 – входы прерываний.

CS – выборка кристалла.

WR – синхросигнал записи.

RD –синхросигнал чтения.

INTA – сигнал подтверждения прерывания.

MS/SV – сигнал переключения «ведомый/ведущий».

INT – сигнал прерывания, идущий в сторону процессора.

CAS0, CAS1, CAS2 – сигналы каскадирования.

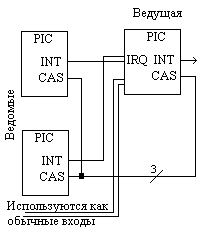

Микросхема может работать в нескольких режимах, которые задаются программно. Одна микросхема может обслуживать до 8 входов прерываний. При большем числе источников прерывания используется каскадное включение схем. Это позволяет обслуживать до 64 входов прерываний. Схема позволяет распределять приоритеты при одновременном поступлении нескольких входных сигналов. Это осуществляется программно. В процессе работы приоритеты входов можно переопределить. Также программно задаётся адрес подпрограммы обработки прерывания для каждого входа.

В режиме взаимодействия с процессором 580ВМ80 контроллер в ответ на сигнал процессора INTA выдаёт в первом цикле обмена код команды CALL, а в 2-х последующих циклах адрес подпрограммы обработки прерывания. Все необходимые адреса загружаются программно в контроллер до начала его использования. При работе контроллера с процессором 1810 обмен происходит за 2 цикла. В ответ на первый сигнал INTA микросхема ничего не выдаёт. В ответ на второй сигнал INTA контроллер выдаёт 8-ми разрядный вектор прерывания. Если число входов прерываний больше 8, то используется каскадная схема включения контроллера. Для взаимодействия контроллеров между собой используются сигналы CAS0, CAS1,CAS2.

При

взаимодействии с процессором серии 580

на вход MS/SV

ведущего контроллера подаётся «1»,

ведомых – «0». При работе с процессором

серии 1810 разделение ведущие и ведомые

происходит программно. Перед началом

использования каждая из микросхем

заряжается всей необходимой информацией

требующейся ей для работы. Каждая ведомая

микросхема программно получает свой

код равный номеру линии IRQ

ведущего контроллера к которому она

подключена.

При

взаимодействии с процессором серии 580

на вход MS/SV

ведущего контроллера подаётся «1»,

ведомых – «0». При работе с процессором

серии 1810 разделение ведущие и ведомые

происходит программно. Перед началом

использования каждая из микросхем

заряжается всей необходимой информацией

требующейся ей для работы. Каждая ведомая

микросхема программно получает свой

код равный номеру линии IRQ

ведущего контроллера к которому она

подключена.

При взаимодействии с процессором серии 580 в первом цикле ведущий контроллер выдаёт код команды CALL. Также ведущий и ведомые контроллеры знают, какой вход прерывания имеет в данный момент наивысший приоритет и который будет обслуживаться в данном цикле обмена. Ведущий контроллер по шинам CAS выдаёт код ведомого контроллера имеющего в данный момент наивысший приоритет. Именно этот ведомый контроллер в последующих 2-х циклах обмена выдаст адрес подпрограммы обработки прерывания.

При работе с процессором 1810 в первом цикле обмена ведущий контроллер формирует сигналы CAS, а во втором цикле ведомый контроллер, чей код выведен на шину CAS выдаёт вектор прерывания. Программно можно:

Блокировать любой вход прерывания.

Программно считать сигнал на любом входе прерывания.

Программно определить номер входа прерывания имеющего в данный момент наивысший приоритет.

Задать реакцию контроллера прерывания по уровню или по фронту.