- •Этапы развития микропроцессорной техники.

- •Классификация микропроцессоров.

- •Виды обменов в микроЭвм.

- •Обмен по прямому доступу в память.

- •Обмен по прерыванию.

- •Микропроцессор 580вм80.

- •Intr – вход запроса прерывания.

- •Inta – сигнал подтверждения обработки прерывания. Он говорит о том, что микропроцессор начал обрабатывать прерывание. Обработки прерывания начинается на границе между двумя командами.

- •Синхронизация работы микропроцессора. Микросхема 580гф24.

- •Типы машинных циклов микропроцессора 580вм80. Микросхема 58вк28/38.

- •Построение разрядно-модульных микропроцессоров.

- •Микропроцессорная секция 1804вс1.

- •Микропроцессорный комплект бис 1815 для конвейерных систем цос.

- •Универсальный процессорный элемент 1815вф1.

- •Сумматор последовательных числе 1815им1.

- •Бис ортогональной регистровой памяти 1815ир1.

- •Цифровая фильтрация на микропроцессорном комплекте 1815.

- •Микропроцессор 1815 вф3.

- •Особенности реализации систем цос на бис 1815вф3.

- •Микропроцессор 1810вм86/88.

- •Inta – сигнал подтверждения прерывания.

- •Модель процессора 1810вм86 для программистов.

- •Программный счётчик и регистр флагов. Флаги, входящие в младший байт повторяют флаги 580-ого процессора.

- •Сопроцессор 1810вм87.

- •Системный контроллер 1810вг88.

- •Включение процессора 1810вм86 в максимальном режиме.

- •Арбитр шин 1810вб89.

- •Организация приоритетного арбитража.

- •2.На системной магистрали располагается память, на резидентной магистрали только увв.

- •Программируемый контроллер прерываний 1810вн59.

- •Контроллер пдп 1810вт37.

- •Процессоры 2, 3 и 4 – ого поколения.

- •Процессор 80386.

Организация приоритетного арбитража.

Для координации доступа к системной шине нескольких процессоров арбитры шин каждого из этих процессоров совместно определяют порядок доступа процессоров к шине. Принцип арбитража основан на концепции приоритета согласно которой в любой промежуток времени одно ведущее устройство будет иметь приоритет над всеми остальными ведущими устройствами. В соответствии с этим, каждому арбитру на шине присваивается свой приоритет. Арбитр имеющий наивысший приоритет захватывает управление шиной в тот момент, когда арбитр с более низким приоритетом заканчивает цикл обмена. арбитр с более низким приоритетом может захватывать шину в тот момент, когда она не требуется арбитру с более высоким приоритетом. Захватив магистраль арбитр добровольно не отдаёт её. сдать системную магистраль арбитр может в следующих случаях:

по требованию арбитра с более высоким приоритетом.

По команде HALT.

Если процессора данного арбитра магистрали обращается к резидентной шине.

Процессор не имеет информации о наличии в схеме арбитра шин и выполняет команды так, как будто он имеет исключительное право на системную магистраль. Поэтому если процессору не предоставлено право использовать в данный момент системную шину, арбитр шины сигналом AEN переводит в третье состояние выходы адресных регистров, усилителей данных, управляющих выходов системного контроллера и через микросхему ГФ84 запрещает выдачу сигнала READY на процессор. при отсутствии сигнала READY процессор переходит в состояние ожидания до того момента, когда арбитр шины не захватит системную магистраль. Это предотвращает столкновение сигналов от нескольких процессоров на системной магистрали. Арбитр определяет занятость магистрали по сигналу BUSY. Данный сигнал выходит из арбитра шин через каскад с открытым коллектором

.

.

Данный вывод арбитра шин одновременно является и входом и выходом. Если ни один из арбитров шин не захватил магистраль, то их выходные каскады становятся закрытыми. В результате на шине BUSY появляется сигнал единичного уровня. Арбитр шин, которому необходимо захватить магистраль, проверяет линию BUSY и при наличии на ней единицы, осуществляет процесс захвата магистрали. Параллельно с этим он открывает выходной каскад сигнала BUSY, переводя сигнал BUSY в нулевое состояние.

В микропроцессорных системах чаще всего используется 3 схемы, распределения приоритетов между арбитрами шин:

Параллельная.

Последовательная.

Циклическая.

В параллельной схеме можно задать любое распределение приоритетов между арбитрами шин. Данная схема содержит приоритетный контроллер, который и распределяет приоритеты.

При большом количестве арбитров шин приоритетный контроллер проще строить на микросхеме ПЗУ. Недостаток данной схемы заключается в том, что приоритеты распределены жёстко.

Схема с циклическим приоритетом.

Отличие от предыдущей схемы заключается в том, что в схему введён счётчик, который периодически изменяет приоритеты.

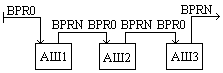

Схема последовательного распределения приоритетов.

Первый арбитр шин имеет наивысший приоритет. Ему всегда разрешается выход на магистраль. Если ему магистраль не нужна, то он представляет её следующему арбитру шин и т.д. Достоинство: простота. Недостатки:

Последний арбитр шин имеет самый низкий приоритет, поэтому магистраль ему может не достаться.

Заключается в том, что сигнал по всей цепочке арбитров шин должен успеть переместиться в течении одного такта частоты BCLK. Это накладывает ограничение на количество арбитров шин, участвующих в такой схеме.

Типовая схема включения арбитра шин.

В зависимости от конфигурации микропроцессорной системы могут быть применены 4 различных режима работы арбитра шин. Они определяются основными сигналами IOB и SYSB, а также дополнительным сигналом SYSB/RESB:

Работа только с системной шиной.

Работа с системной шиной памяти и резидентной шиной ввода вывода.

Работа с системной шиной и резидентной шиной.

Работа с системной шиной, резидентной шиной памяти и резидентной шиной ввода вывода.

1.Работа с системной шиной.

И к памяти и к УВВ процессор может обращаться только выйдя на системную магистраль, куда выходят и другие процессоры. Все ресурсы у данного процессора находятся на магистрали. Выйти на магистраль ему помогает арбитр шин.

Когда процессор ходче выполнить какую-то операцию на системной магистрали, он сообщает об этом сигналами состояния S0,S1,S2. Арбитр шин ВБ9 обмениваясь сигналами BPR0 и BPRN с другими арбитрами шин пытается захватить системную магистраль. Когда ему это удаётся, он выдаёт сигнал AEN на системный контроллер. Системный контроллер начинает работу, формируя управляющие сигналы и сигналы при помощи которых он управляет работой микросхем ИР82 и ВА86. Эти сигналы также зависят от сигналов состояния S0,S1,S2.