- •Этапы развития микропроцессорной техники.

- •Классификация микропроцессоров.

- •Виды обменов в микроЭвм.

- •Обмен по прямому доступу в память.

- •Обмен по прерыванию.

- •Микропроцессор 580вм80.

- •Intr – вход запроса прерывания.

- •Inta – сигнал подтверждения обработки прерывания. Он говорит о том, что микропроцессор начал обрабатывать прерывание. Обработки прерывания начинается на границе между двумя командами.

- •Синхронизация работы микропроцессора. Микросхема 580гф24.

- •Типы машинных циклов микропроцессора 580вм80. Микросхема 58вк28/38.

- •Построение разрядно-модульных микропроцессоров.

- •Микропроцессорная секция 1804вс1.

- •Микропроцессорный комплект бис 1815 для конвейерных систем цос.

- •Универсальный процессорный элемент 1815вф1.

- •Сумматор последовательных числе 1815им1.

- •Бис ортогональной регистровой памяти 1815ир1.

- •Цифровая фильтрация на микропроцессорном комплекте 1815.

- •Микропроцессор 1815 вф3.

- •Особенности реализации систем цос на бис 1815вф3.

- •Микропроцессор 1810вм86/88.

- •Inta – сигнал подтверждения прерывания.

- •Модель процессора 1810вм86 для программистов.

- •Программный счётчик и регистр флагов. Флаги, входящие в младший байт повторяют флаги 580-ого процессора.

- •Сопроцессор 1810вм87.

- •Системный контроллер 1810вг88.

- •Включение процессора 1810вм86 в максимальном режиме.

- •Арбитр шин 1810вб89.

- •Организация приоритетного арбитража.

- •2.На системной магистрали располагается память, на резидентной магистрали только увв.

- •Программируемый контроллер прерываний 1810вн59.

- •Контроллер пдп 1810вт37.

- •Процессоры 2, 3 и 4 – ого поколения.

- •Процессор 80386.

Inta – сигнал подтверждения прерывания.

MIN |

MAX |

HLD |

RQ/E0 |

HLDA |

RQ/E1 |

W |

LOCK |

M/IO |

ST2 |

OP/IP |

ST1 |

DE |

ST0 |

STB |

QS0 |

INTA |

QS1 |

LOCK – сигнал блокировки. Он необходим для работы с разделяемыми ресурсами. Сигнал LOCK порождается командой LOCK. Назначение данного сигнала заключается в том, что ни одно другое устройство не имеет права захватывать магистраль, пока присутствует данный сигнал. Это позволяет процессору выполнить несколько связанных команд без освобождения магистрали между ними.

ST2,ST1,ST0 – сигналы состояния микропроцессора. эти 3 сигнала определяют какую операцию осуществляет процессор.

QS0,QS1 – определяют состояние очереди команд. Они необходимы для работы сопроцессора. Они отражают 4 состояния:

Из очереди ничего не выбирается.

Из очереди выбирается первый байт команды.

Из очереди выбирается последующий байт команды.

Очередь сбрасывается.

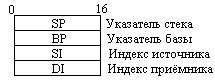

Модель процессора 1810вм86 для программистов.

Процессор имеет в своём составе 14 16-ти разрядных программно-доступных регистра, которые удобно рассматривать разделив их на 4 группы:

Регистры общего назначения.

Указатели и индексные регистры. Они необходимы для определения внутри сегментного смещения при косвенном методе адресации.

Сегментные регистры. Они определяют базу в 20-ти разрядном адресе.

В данном микропроцессоре мы имеет 20-ти разрядную адресацию. Полный 20-ти разрядный адрес состоит из 2-х частей: базового адреса и смещения.

При таком формировании адреса содержимое базового адреса и смещения определены неоднозначно.

![]()

В пределах адресного пространства адресуется каждый байт, т.е. каждый байт имеет свой адрес и свой номер. Любые 2 смежных байта образуют 16-ти разрядное слово.

![]()

Данные адресуемые в пределах неизменных старших 16-ти разрядов образуют параграф (FFFFX, где Х – любой). Под сегментом понимается область памяти, адресуемая при неизменном базовом адресе. Максимальный размер сегмента 64К. Минимальный размер сегмента 1. Сегмент имеет переменную величину.

Программный счётчик и регистр флагов. Флаги, входящие в младший байт повторяют флаги 580-ого процессора.

Прерывания в данном процессоре могут быть внешними и внутренними. Каждое прерывание имеет свой вполне определённый номер, называемый вектором прерывания. Связь между прерываниями и программами осуществляющими обработку прерываний происходит через таблице прерывания, имеющую размер 1К и занимающую адресное пространство начиная с нулевой ячейки. Всего возможно 256 видов прерываний, т.е. под каждое прерывание выделено 4 байта (база и смещение для программы обработки прерывания).

Прерывания разделены по приоритетам. Одни и те же прерывания можно вызвать и аппаратно и программно.

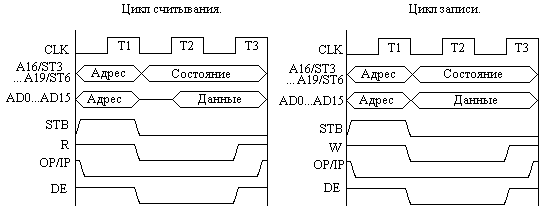

Основные циклы шины процессора 1810.

В данном процессоре выборка данных производится с опережением по сравнению с их обработкой, поэтому в момент выборки неизвестно, что выбирается ко команды или данные.

В данном процессоре 2 типа циклов: цикл записи и цикл считывания.

Использование сигналов состояния ST3 и ST4, которые отражают используемый базовый регистр позволяют увеличить адресное пространство до 4Мб.

Генератор тактовых импульсов 1810ГФ84.

Функциональный генератор формирует сигнал готовности и начального сброса (?).

X1,X2 – входы для подключения кварца.

OSC – выход генератора.

TANK – служит для подключения внешнего колебательного контура, если кварц работает на третьей гармонике.

F/C – переключатель между внутренним генератором и внешним.

EFI – вход внешнего генератора.

CSYN – сигнал синхронизации внутреннего генератора с внешним сигналом. Используется в многопроцессорных системах.

CLK – выходной сигнал тактовой частоты. Частота в 4 раза ниже, чем на выходе ОSC.

PCLK – тактовая частота ещё в 2 раза ниже, чем в CLK. Данная частота используется в системных целях.

RDY1, RDY2 – сигналы готовности, поступающие от ВУ. Предполагается, что RDY1 и RDY2 поступают с разных магистралей.

Сигналы AEN1 и AEN2 разрешают реагировать на сигналы RDY1 и RDY2 соответственно.

RES – аналоговый вход начального сброса.

RESQ – цифровой сигнал начального сброса, который поступает в систему.

Структура однопроцессорной системы на микропроцессоре 1810ВМ86.

Особенности процессора ВМ88.

Первым был выпущен процессор ВМ88 и только через год ВМ86.

Данный процессор был переходным от 8-ми разрядного к 16-ти разрядному. Процессор ВМ88 осуществлял обмен данными по магистрали данных используя 8 разрядов, т.е. с AD0 по AD7.

В процессоре Вм88 отсутствует BHE, а вместо него используется SS0. В минимальном режиме сигнал SS0 отображает сигнал состояния ST0, а в максимальном режиме по SS0 всегда передаётся уровень «1». Это позволяет ПО определить тип процессора.

По сравнению с ВМ86 инвертирован сигнал IO/M. Предполагалось, что таким образом процессор ВМ88 станет ближе к процессору ВМ85. Однако в остальном временные диаграммы ВМ88 и ВМ86 не совпадают.

Длина очереди сокращена с 6 байт до 4-х.