- •Этапы развития микропроцессорной техники.

- •Классификация микропроцессоров.

- •Виды обменов в микроЭвм.

- •Обмен по прямому доступу в память.

- •Обмен по прерыванию.

- •Микропроцессор 580вм80.

- •Intr – вход запроса прерывания.

- •Inta – сигнал подтверждения обработки прерывания. Он говорит о том, что микропроцессор начал обрабатывать прерывание. Обработки прерывания начинается на границе между двумя командами.

- •Синхронизация работы микропроцессора. Микросхема 580гф24.

- •Типы машинных циклов микропроцессора 580вм80. Микросхема 58вк28/38.

- •Построение разрядно-модульных микропроцессоров.

- •Микропроцессорная секция 1804вс1.

- •Микропроцессорный комплект бис 1815 для конвейерных систем цос.

- •Универсальный процессорный элемент 1815вф1.

- •Сумматор последовательных числе 1815им1.

- •Бис ортогональной регистровой памяти 1815ир1.

- •Цифровая фильтрация на микропроцессорном комплекте 1815.

- •Микропроцессор 1815 вф3.

- •Особенности реализации систем цос на бис 1815вф3.

- •Микропроцессор 1810вм86/88.

- •Inta – сигнал подтверждения прерывания.

- •Модель процессора 1810вм86 для программистов.

- •Программный счётчик и регистр флагов. Флаги, входящие в младший байт повторяют флаги 580-ого процессора.

- •Сопроцессор 1810вм87.

- •Системный контроллер 1810вг88.

- •Включение процессора 1810вм86 в максимальном режиме.

- •Арбитр шин 1810вб89.

- •Организация приоритетного арбитража.

- •2.На системной магистрали располагается память, на резидентной магистрали только увв.

- •Программируемый контроллер прерываний 1810вн59.

- •Контроллер пдп 1810вт37.

- •Процессоры 2, 3 и 4 – ого поколения.

- •Процессор 80386.

Особенности реализации систем цос на бис 1815вф3.

Основной алгоритм линейной обработки цифровой информации в системах ЦОС может быть описан уравнением: Y=W*X, где

Х – вектор входных воздействий, представляющих собой или комплексные переменные или их квадратурные составляющие;

Y – это вектор выходных переменных, представленных таким же образом;

W – это матрица комплексных весовых коэффициентов.

A=ReA+jImA;

A=|A|ej![]() ;

;

Коэффициенты

матрицы W

представляют собой передаточные функции

цифровых фильтров, задаваемых обычно

в виде отношения полиномов к z

плоскости.![]()

Точно также, как и ранее мы можем

представить передаточную функцию H(z)

в виде трёх различных форм:

Точно также, как и ранее мы можем

представить передаточную функцию H(z)

в виде трёх различных форм:

Прямая структура.

Параллельная структура.

Последовательная структура.

Для

реализации Hij(z)

необходимо уметь реализовать схему

фильтра первого порядка. А схемы фильтров

более высоких порядков получатся из

них путём параллельного или последовательного

включения простейших фильтров.

Элементарный рекурсивных фильтр первого

порядка описывается передаточной

функцией вида:

Параметры с индексом 0, т.е. r0

и

0

- это

амплитуда и фазовый сдвиг нуля передаточной

функции. Если

Параметры с индексом 0, т.е. r0

и

0

- это

амплитуда и фазовый сдвиг нуля передаточной

функции. Если![]() , то H(z)=0.

Параметры с индексом p,

т.е. rp

и

p

- это

амплитуда и фазовый сдвиг полюса

передаточной функции. Если

, то H(z)=0.

Параметры с индексом p,

т.е. rp

и

p

- это

амплитуда и фазовый сдвиг полюса

передаточной функции. Если![]() , то H(z)=

, то H(z)=![]() .

.

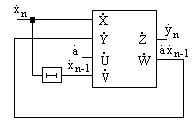

С хема

простейшего фильтра содержит сумматоры,

схемы умножения и элемент задержки.

Задержка будет осуществляться с

использованием микросхемы ИР1, а сложение

и умножение необходимо выполнить на

микросхеме ВФ3. При этом надо учитывать,

что в общем случае переменные являются

комплексными числами.

хема

простейшего фильтра содержит сумматоры,

схемы умножения и элемент задержки.

Задержка будет осуществляться с

использованием микросхемы ИР1, а сложение

и умножение необходимо выполнить на

микросхеме ВФ3. При этом надо учитывать,

что в общем случае переменные являются

комплексными числами.

Предположим,

что надо сложить:

![]()

![]() ReZ=ReX+ReY;

ReZ=ReX+ReY;

![]() ImZ=ImX+ImY;

ImZ=ImX+ImY;

![]()

W=UV;

W=ReW+jImW;

U=ReU+jImU;

V=ReV+jImV;

ReW+jImW=(ReU+jImU)(ReV+jImV)=ReUReV+jImUReV+jReUImV-ImUImV;

ReW=ReUReV-ImUImV;

ImW=ImUReV+ReUImV;

Для вычитания схема настраивается.

Количество схем можно сократить до 3-х, если введём следующие преобразования:

ReW=ReUReV-ImUImV+ReUInV-ReUInV;

ImW=ImUReV+ReUImV+ImUImV-ImUImV;

ReW=ReU(ReV-ImV)+ImV(ReV-ImU);

ImW=ImV(ReU-ImU)+ImU(ReV+ImV);

Уравнение

для нерекурсивного фильтра выглядит

следующим образом:

![]()

При формировании отсчёта xn-1 необходимо задержать xn на длину одного слова. Для этого вводится элемент задержки. Однако необходимо учесть, что часть необходимой задержки получается за счёт прохождения отсчётом xn-1 схемы умножения. Реальный элемент задержки осуществляет задержку на длину отсчёта минус задержка схемы умножения. Элемент задержки формируется не схеме 1815ИР1.

Рекурсивный

фильтр:

![]()

При реализации задержки необходимой для получения Yn-1 из Yn неоходимо учитывать здержку схем.

На 48 микросхемах ВФ3 реализуется 8-ми точечное быстрое преобразование Фурье.

Ускорение в обработке по сравнению с реализацией на универсальных микропроцессорах достигается за счёт:

Параллельной обработки.

За счёт микропрограммного управления.

Микропроцессор 1810вм86/88.

I8086, I8088.

Данный процессор является 16-ти разрядным и может работать в 2-х режимах:

Минимальном (предназначенном для однопроцессорных систем).

Максимальном (предназначенном для многопроцессорных систем и сложных однопроцессорных систем).

В этих режимах часть выводов микропроцессора меняет своё назначение.

Второй особенностью данного микропроцессора является опережающая выборка данных (прообраз кэш памяти).

H LD

– сигнал запроса ПДП.

LD

– сигнал запроса ПДП.

NMI – немаскируемый сигнал запроса прерывания.

INT - маскируемый сигнал запроса прерывания.

RDY – сигнал готовности для работы с медленно действующими устройствами.

TEST – сигнал проверки. При появлении данного сигнала микропроцессор вставляет холостые такты ожидания и проверяет повторно вход TEST через 5 тактов.

CLK – вход тактовой частоты.

CLR – сигнал начального сброса.

MN/MX – переключатель из минимального режима в максимальный.

AD0…AD15 – совмещённая магистраль адреса и данных.

A16/ST3…A19/ST6 – совмещённая шина адреса и состояний. В первом такте цикла обмена выдаётся адрес, в последующих двух состояние. Т.к. шина адреса 20-ти разрядная, то это позволяет адресовать 1Мгб памяти (640 Кб, остальные на другие нужды, например BIOS).

R – синхросигнал чтения информации.

W – синхросигнал записи информации.

M/IO – показывает с каким устройством производится обмен (память или УВВ). К микропроцессору можно подключить 64К 8-ми разрядных портов, которые адресуются адресной шиной А0 …А15.

STB – синхросигнал выдачи адреса.

BHE/ST7 – 1. Показывает выдаются ли данные по старшему байту данных.

ST7 – сигнал состояния.

В первом такте выдаётся сигнал BHE, дальше сигнал состояния.

OP/IP – показывает в каком направлении ведётся обмен по шине данных. Данный сигнал управляет работой ключей.

DE – сигнал разрешения. Он становится активным на время передачи данных по магистрали. Данный сигнал управляет работой ключей.

HLDA – сигнал подтверждения ПДП.