- •Этапы развития микропроцессорной техники.

- •Классификация микропроцессоров.

- •Виды обменов в микроЭвм.

- •Обмен по прямому доступу в память.

- •Обмен по прерыванию.

- •Микропроцессор 580вм80.

- •Intr – вход запроса прерывания.

- •Inta – сигнал подтверждения обработки прерывания. Он говорит о том, что микропроцессор начал обрабатывать прерывание. Обработки прерывания начинается на границе между двумя командами.

- •Синхронизация работы микропроцессора. Микросхема 580гф24.

- •Типы машинных циклов микропроцессора 580вм80. Микросхема 58вк28/38.

- •Построение разрядно-модульных микропроцессоров.

- •Микропроцессорная секция 1804вс1.

- •Микропроцессорный комплект бис 1815 для конвейерных систем цос.

- •Универсальный процессорный элемент 1815вф1.

- •Сумматор последовательных числе 1815им1.

- •Бис ортогональной регистровой памяти 1815ир1.

- •Цифровая фильтрация на микропроцессорном комплекте 1815.

- •Микропроцессор 1815 вф3.

- •Особенности реализации систем цос на бис 1815вф3.

- •Микропроцессор 1810вм86/88.

- •Inta – сигнал подтверждения прерывания.

- •Модель процессора 1810вм86 для программистов.

- •Программный счётчик и регистр флагов. Флаги, входящие в младший байт повторяют флаги 580-ого процессора.

- •Сопроцессор 1810вм87.

- •Системный контроллер 1810вг88.

- •Включение процессора 1810вм86 в максимальном режиме.

- •Арбитр шин 1810вб89.

- •Организация приоритетного арбитража.

- •2.На системной магистрали располагается память, на резидентной магистрали только увв.

- •Программируемый контроллер прерываний 1810вн59.

- •Контроллер пдп 1810вт37.

- •Процессоры 2, 3 и 4 – ого поколения.

- •Процессор 80386.

Микропроцессор 1815 вф3.

Микропроцессор ВФ3 имеет 2 особенности, делающие его несовместимым с остальными микросхемами данной серии:

Информация обрабатывается данным микропроцессором представлена в знакоразрядной форме.

Микропроцессор ведёт обработку дынных старшими разрядами вперёд.

Информация

в микропроцессоре описывается троичным

кодом: Xi={1,0,![]() }.

Такое описание позволяет обойтись без

знакового разряда. Однако код имеет

избыточность, т.е. одно и то же слово

можно представить несколькими способами.

Например: Х=1

=01.

Код является позиционным. Чтобы обойти

неоднозначность описания слов принято

ограничение при котором положительные

числа описываются цифрами 0 и 1, о

отрицательные числа описываются с

помощью цифр 0 и

.

Т.е. если Х=+0,0101=0,0101. Х=-0,0101=0,0

0

.

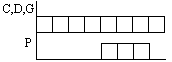

Каждый разряд в микропроцессоре

передаётся по 2-м шинам: положительной

и отрицательной. Запятая в микропроцессоре

выполняет роль маркера разделяющего

слова и передаётся уровнем 1 по обоим

шинам.

}.

Такое описание позволяет обойтись без

знакового разряда. Однако код имеет

избыточность, т.е. одно и то же слово

можно представить несколькими способами.

Например: Х=1

=01.

Код является позиционным. Чтобы обойти

неоднозначность описания слов принято

ограничение при котором положительные

числа описываются цифрами 0 и 1, о

отрицательные числа описываются с

помощью цифр 0 и

.

Т.е. если Х=+0,0101=0,0101. Х=-0,0101=0,0

0

.

Каждый разряд в микропроцессоре

передаётся по 2-м шинам: положительной

и отрицательной. Запятая в микропроцессоре

выполняет роль маркера разделяющего

слова и передаётся уровнем 1 по обоим

шинам.

|

D+ |

D- |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

Знак |

1 |

1 |

Обработка начиная со старших разрядов обусловлена тем, что при этом проще выполняются некоторые операции характерные для систем ЦОС. Часто обработка начинается не дожидаясь прихода всех разрядов числа.

Микросхема выполняет одновременно 2 операции:

S=A*B;

P=(C

D)G;

D)G;

Под * понимается операция сложение, вычитание, взятие модуля числа и сравнение чисел.

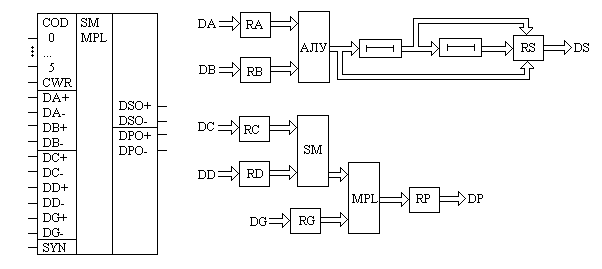

Шина COD 0…5 – шина выбора режима. По этим проводам микросхема настраивается на выполнение определённых операций.

CWR – синхросигнал для записи кода.

DA, DB, DC, DD, DG – шины входных данных.

SYN – синхросигнал для ввода данных.

DS – выходная шина первой операции.

DP – выходная шина результата второй операции.

Входные переменные А и В записываются в одноразрядные регистры RA и RB. Назначение этих регистров – это привязка данных А и В к тактовым сигналам. После этого входные данные поступают на АЛУ. АЛУ выполняет операцию закодированную разрядами COD. Это могут быть операции сложения, вычитания, сложения и вычитания со взятием модуля, а также операция сравнения, в результате выполнения которой на выход выдаётся большее из двух чисел А и В. В результате операции сложения может произойти переполнение, т.е. микросхема работает с числами меньше 1, т.е. с правильными дробями. Установкой определённых разрядов кода можно заставить микросхему сдвигать результат на один разряд в сторону младших разрядов или не делать этого. Во втором случае за корректность результата отвечает разработчик. Следом за АЛУ установлены две схемы (регистра) задержки. Они предназначены для задержки выходного сигнала с целью выравнивания задержек в схеме сложения и в схеме умножения. С выходов АЛУ и элементов задержки результат попадает на одноразрядный регистр результата RS. В зависимости от разрядов COD регистр RS запоминает одно из трёх значений.

Два входных числа C и D поступают на одноразрядные регистры RC и RD, которые осуществляют привязку этих чисел к синхросигналу. Сумматор SM выполняет операцию сложения или вычитания в зависимости от разрядов COD. Входное число G поступает на 4-х разрядный регистр RG. ОН осуществляет задержку таким образом, чтобы сигнал на его выходе появлялся одновременно с выходом сигнала на сумматоре SM.

Схема умножения MPL выполняет операцию умножения в соответствии с уравнением. Результат запоминается на одноразрядном регистре RP. На сумматоре возможно переполнение, поэтому если необходимо, то производится масштабирование результата суммирования при помощи разрядов COD.(при ????).

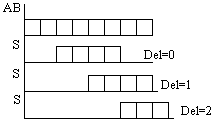

На схеме сумматора при отсутствии выравнивания результата, результат на выходе появляется с дисперсностью равной 3-м тактам.

Если схема суммирования производит выравнивание сигналов, то задержка выходного сигнала кратна двум тактам.

Вторая схема, которая выполняет умножение также задерживает выходной сигнал и его задержка зависит от наличия или отсутствия выравнивания. При отсутствии выравнивания задержка производится на 6 тактов:

При наличии выравнивания задержка происходит на 4 такта:

Микросхема выполнена по И2Л технологии и имеет напряжение питания от 1,5 до 5В.